Устройство управления блоком памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении систем памяти для ЭВМ. Целью изобретения является расширение области применения за счет исключения зависимости параметров выходных сигналов от тактовой частоты. Цель достигнута введением в устройство одновибраторов 3 и 4, элементов 2,5,9,11 задержки и элементов И 6 и 7. Поскольку выходные сигналы устройства не зависят от тактовой частоты, стало возможным, например, повысить быстродействие блока ОЗУ и ЭВМ в целом путем увеличения тактовой частоты. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51) 5 G 11 С 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTHPblTHRM

ПРИ ГКНТ СССР

1 (21) 4267669/24-24 (22) 24.06.87 (46) 07.02.90. Бюл. Р 5 (72) И.В.Терехов и Б.И.Ткач (53) 681.325(088.8) (56) Патент Японии У 58-53432, кл. С 11 С 7/00, 1983.

Универсальная вычислительная маши-. на БЭСМ-6. Техническое описание.

Ч.З, кн. 1, с. 26-32,87, кн.2, с. 70-71. (54) УСТРОЙСТВО УПРАВЛЕНИЯ БЛОКОМ

ПАМЯТИ .(57) Изобретение относится к вычис„„SU„„1541670 А1

2 лиФельной технике и может быть использовано при построении систем памяти для ЭВМ. Целью изобретения является расширение области применения за счет исключения зависимости параметров выходных сигналов от тактовой частоты. Цель достигнута введением в устройство одновибраторов 3 и 4, элементов 2, 5, 9y ll задержки и элементов И 6 и 7. Поскольку выходные сигналы устройства зависят от тактовой частоты, стало возможным, например, повысить быстродействие блока ОЗУ и ЭВМ в целом путем увеличения тактовой частоты. 2 ил. 3

1541670

Изобретение относится к вычислительной технике и может быть использовано при построении систем памяти для ЭВМ.

Целью изобретения является расширение области применения за счет исключения зависимости параметров выходных сигналов от тактовой частоты.

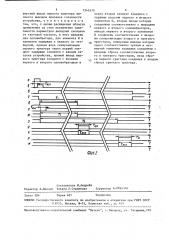

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 временные диаграммы работы устройства.

Устройство содержит первый триггер 1, гервый элемент 2 задержки, первый 3 и второй 4 одновибраторы, второй элемент 5 задержки, первый 6 второй 7 элементы И, второй триггер

8, третий элемент 9 задержки, третий триггер 10, четвертый элемент 11 задержки, вход 12 запуска, выходы признаков конца цикла выборки 13, конца цикла обращения 14, готовности 15.

Устройство работает следующим образом, Принимают, что второй триггер на выходе устройства формирует признак окончания цикла выборки, третий триггер признак окончания цикла обращения, а первый триггер - признак готовности блока памяти.

По сигналу запуска триггер 1 пе( реключается в единичное состояние (фиг. 2в). На нулевом выходе триггера 1 появляется сигнал низкого уровня (фиг. 2г), означающий, что блок памяти занят. Положительный уровень сигнала с единичного выхода триггера 1 поступает на первые входы одновибраторов 3 и 4, являюшиеся входами запуска. Положительным фронтом сигнала с триггера 1 одновибраторы запускаются. При этом, на инверсных выходах одновибраторов 3 и 4 устанавливаются сигналы низкого уровня (фиг. 2ж,з). Длительность импульса, сформированного на прямом выходе первого одновибратора 3, выбирается равной длительности цикла выборки.

Длительность импульса на. прямом выходе второго одновибратора 4 выбирается равной длительности цикла обращения.

Положительный уровень с инверсного выхода одновибратора 3 поступает на вход триггера 8 и на первый вход элемента И 6. На второй вход элемен5

10 !

45 та И б поступа т через элемент 5 задержки сигнал с единичного выхода триггера 1. Это необходимо для того, чтобы исключить ложное срабатывание элемента И 6 в момент переходного процесса в одновибраторе 3 (фиг.2e), Таким образом, после окончания положительного импульса одновибратора

3 на входах 1 и 2 элемента 6 совпадают положительные сигналы (фиг,2е, ж) и на С-вход триггера 8 поступает сигнал, передним фронтом которого триггер 8 устанавливается в единичное состояние (фиг. 2и). На инверсном выходе триггера 8 появляется отрицательный уровень сигнала (фиг. 2к), который через элемент 9 задержки поступает на вход сброса триггера 8 и устанавливает его в нулевое состояние. При этом на единичном выходе триггера 8 (фиг. 2и) формируется сигнал окончания цикла выборки, длительность которого определяется элементом 9 задержки.

Аналогичным образом, с помощью одновибратора 4,формируется сигнал на единичном выходе триггера 10 (фиг. 2л,н). Отрицательный сигнал с нулевого выхода триггера 10 поступает через третью линию 11 задержки на вход сброса триггера 1 и устанавливает его в нулевое состояние. В результате на выходе устройства появляется сигнал высокого уровня— признак готовности к очередному циклу работы (фиг. 2г).

Таким образом, введение двух одновибраторов, двух элементов И и четырех элементов задержки с соответствующими связями позволяет исключить зависимость временной диаграммы работы устройства от частоты поступления тактирующих импульсов и повысить быстродействие ЭВМ путем увеличения частоты следования тактирующих импульсов.

Формула изобретения

Устройство управления блоком памяти, содержащее триггеры с первого по третий, причем информационный вход первого триггера является входом запуска устройства, прямые выходы второго и третьего триггеров являются соответственно выходами признака конца цикла выборки и признака конца цикла обращения устройства, ин3

У

Составитель И.Андреев

Редактор А.Шандор Техред Л.Сердюкова Корректор А.Обручар

Подписное

Тираж 487

Заказ 284

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

1!3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r.Óæãîðîä, ул. Гагарина, 101

5 154 версный выход первого триггера является выходом признака готовности устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения за счет исключения зависимости параметров выходных сигналов от тактовой частоты, в него введены два одновибратора, два элемента И и элементы задержки с первого по четвертый, причем вход синхронизации первого триггера через первый элемент задержки соединен с входом запуска устройства, прямой выход первого триггера соединен с входами первого и второго одновибраторов и! 670 6 через второй элемент задержки с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с выходами первого и второго одновибраторов, выходы первого и второго элементов

И соединены соответственно с входами синхронизации второго и третьего триггеров, инверсные выходы которых через соответственно третий и четвертый элементы задержки соединены с входами сброса соответственно второго и третьего триггеров, вход сброса первого триггера соединен с входом сброса третьего триггера,