Запоминающее устройство с идентификацией ошибок

Иллюстрации

Показать всеРеферат

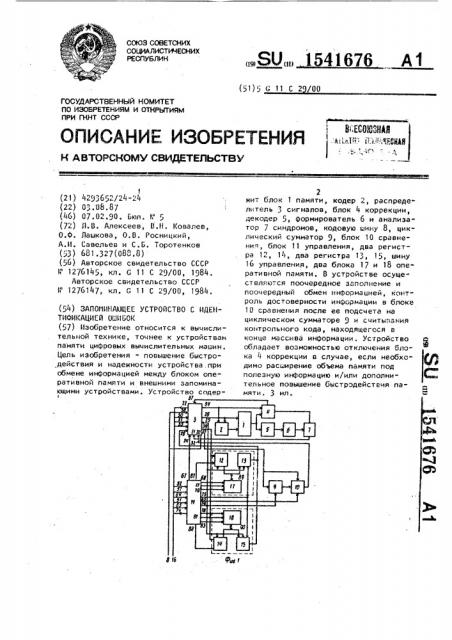

Изобретение относится к вычислительной технике, точнее к устройствам памяти цифровых вычислительных машин. Цель изобретения - повышение быстродействия и надежности устройства при обмене информацией между блоком оперативной памяти и внешними запоминающими устройствами. Устройство содержит блок 1 памяти, кодер 2, распределитель 3 сигналов, блок 4 коррекции, декодер 5, формирователь 6 и анализатор 7 синдромов, кодовую шину 8, циклический сумматор 9, блок 10 сравнения, блок 11 управления, два регистра 12,14, два регистра 13, 15, шину 16 управления, два блока 17 и 18 оперативной памяти. В устройстве осуществляются поочередное заполнение и поочередный обмен информацией, контроль достоверности информации в блоке 10 сравнения после ее подсчета на циклическом сумматоре 9 и считывания контрольного кода, находящегося в конце массива информации. Устройство обладает возможностью отключения блока 4 коррекции в случае, если необходимо расширение объема памяти под полезную информацию и/или дополнительное повышение быстродействия памяти. 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51) С 11 С 2 00

3СЕОИВНВ

l,: 1(l. 1т! !;(I":; !..0@Я

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЦТИЯМ

ПРИ ГКНТ СССР

1 (21) 42936 2/24-24 (22) 03. 08.87 (46) 07.02.90 Вюл. V (72) Л.В. Алексеев, U.Н. Ковалев, О.ф. Лашкова, О.В. Росницкий, А.И. Савельев и С.Б. Торотенков (.г3) 681.327(088.8) (5á) Авторское свидетельство СССР (с 127614. р, кл. С 11 С 29/00, 1984.

Авторское свидетельство СССР (1 127614/, кл. G 11 С 29/00, 1984. (54) ЗАПОИИНА(ОЦЕЕ УСТРОЙСТВО С ИДЕНТИФИКАЦИЕД 0((ИВОК (57) Изобретение относится к вычислительной технике, точнее к устройствам памяти цифровых вычислительных машин.

Цель изобретения - повышение быстродействия и надежности устройства.при обмене информацией между блоком оперативной памяти и внешними запоминающими устройствами. Устройство содерс И

„„Я0„„1541676 А1

2 жит блок 1 памяти, кодер 2, распреде" литель 3 сигналов, блок 4 коррекции, декодер, формирователь 6 и анализа" тор 7 синдромов, кодовую шину 8, циклический сумматор 9, блок 10 сравнения, блок 11 управления, два регистра 12, 14, два регистра 13, 15, шину

16 управления, два блока 17 и 18 оперативной памяти. В устройстве осуществляются поочередное заполнение и поочередный обмен информацией, контроль достоверности информации в блоке

10 сравнения после ее подсчета на циклическом сумматоре 9 и считывания контрольного кода, находящегося в конце массива информации. Устройство обладает возможностью отключения блока 4 коррекции в случае, если необходимо расширение объема памяти под полезную информацию и/или дополнительное повышение быстродействия памяти. 3 ил.

1 41676

Изобретение относится к вычислительной технике и может быть использовано в качестве запоминающего устройства ЦВИ и в устройствах обмена информации между внеыними запоминающими устройствами (ВЗУ) с коррекцией и обнаружением многократных ошибок.

Цель изобретения - повышение быстродействия и надежности устройства.

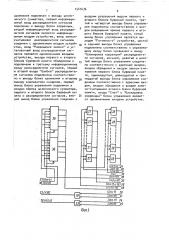

Ila фиг. 1 изображена структурная схема запоминающего устройства; на фиг. 2 - структурная схема распределителя си — íàëîâ; на фиг. 3 - структурная схема блока управления.

Устройство содержит блок 1 памя ти, кодер 2, распределитель 3 сигналов, блок 4 коррекции, декодер формирователь 6 синдромов, анализатор 7 синдромов, информационную ыину

0, циклический сумматор 9, блок 10 сравнения, блок 11 управления, первые входной 12 и выходно" 13 регистры, вторые входной 14 и выходной 1 > регистры, управляющую шину 16„ первый блок 17 оперативно" памяти, второй блок 16 оперативной памяти.

Распределитель 3 сигналов содержит (фиг . 2) элемент ИЛИ 19, имеющий входы 20 и 21, являющиеся соответственно 3g первым и вторым входами "Ошибка" рвс."

1 пределителя 3, и выход 22, являющийся выходом "Ошибка" устройства. Распреде, литель 3 также содержит триггер 23, имеащий входы 24 и 2g, являющиеся со1 ответственно входом Блокировка кор35 рекции" и установочным входом коммутатора, выход 26, элементы И 27, и 28, информационный вход 29, вход 30 записи-считывания, вход 31 разрешения записи, выходы 32-34, установочный вход

35, элементы ИЛИ-И 36, информационные входы 17 и 38 и выход 39.

Бгок 11 управления (фиг. 3) содержит г;ервый элемент НЕ 40, вход которо-45 го подключен к входу первого элемента

И 41, к входу второго элемента И 42, к входу первого элемента И-ИЛИ-НЕ 43, к входу второго элемента И-ИЛИ-НЕ 44, к одному из входов первого элемента

И-НЕ 4 и второго элемента И-НЕ 46 и к одним из входов третьего элемента

И 47, четвертого элемента И 48, пятого элемента И 49, шестого элемента И 50 и к входу 91 записи-считывания блока

11. Вход . р2 начальной установки блока подсоединен к шине 16 и к второму элементу НЕ 53, выход ксторого подсоединен к первому входу первого счетчио ка 94, к первому входу второго счетчика Ц и к выходу 96 блока 11. Вход

57 "Старт" блока 11 подключен к первым входам элемента И 41 и седьмого элемента И 58 и к входу генератора 59.

Выход генератора 59 подсоединен к входам первого элемента И-ИЛИ 60 и второго элемента И-ИЛИ 61, третьего элемента И-ИЛИ-НЕ 62, четвертого элемента

И-ИЛИ-НЕ 63 и второго элемента

И"ИЛИ-НЕ 44, Вход 64 "Счет" блока 1 подключен к входам первого элемента

И-ИЛИ 60 и второго элемента И-ИЛИ 61, к входам третьего элемента И-ИЛИ-НЕ 62, к входу четвертого элемента И-ИЛИ-HE

63 к входам первого элемента И-ИЛИ-НЕ

43 и второго элемента И-ИЛИ-HE 44.

Вход 65 "Блокировка коррекции" блока 11 подключен к входу третьего элемента НЕ 66, выход которого подключен к выходу 67 блока 11. Третий выход счетчика г4 подсоединен к выходу

68 блока 11 управления. Выход счетчика у4 подсоединен к одному из входов третьего элемента И-НЕ 69, к одному из входов первого элемента ИЛИ 70.

Вход триггера 71 подсоединен к выходу 72 счетчика Я, Выход элемента

ИЛИ 73 подключен к выходу 74 блока 11, имеющего также выход 7 . Выход третьего элемента И-ИЛИ-НЕ 62 подсоединен к входу первого одновибратора 76„ выход которого является выходом 77 блока

11 управления и подключен к входу четвертого элемента НЕ 78. Выход четвертого элемента НЕ 78 подсоединен к одному из входов первого элемента

И-НЕ 4, выход которого является выходом 79 блока 11. Выход четвертого элемента И-ИЛИ-НЕ 63 подсоединен к входу второго одновибратора ОО, выход которого является выходом 81 блока

11 и подключен к входу пятого элемента НЕ 82. Выход второго элемента И-НЕ

46 является выходом 83 блока 11. Выход третьего одновибратора 84 является выходом 85 блока 11 управления. Выход второго элемента ll--ИЛИ-НЕ 44 подсоединен к входу четвертого одновибратора 86, выход которого является выходами 87 и 88 блока 11.

Регистры 12 и 13 и блок 17 образуют первый блок 89 буферной памяти, регистры 14 и l q и блок 18 — второй блок 90 буферной памяти.

Устройство работает следующим образом.

1541676

Для приведения устройства в исходное состояние на вход блока 11 управления с шины 16 подается сигнал начальной установки, который поступает через элемент ПЕ 53 на входы счетчи5 ков 54 и Я . Этот же сигнал подается на вход распределителя 3, устанавливая триггер 23 в "0" состояние, а также на входы первого 12 и второго 1О

14 регистров, на входы первого 13 и второго 1 регистров и на вход циклического сумматора 9.

В режиме записи информация поступает на вход распределителя 3 с шины 8 и подается на входь элементов ИЛИ-И

3á.

По сигналу "3.=лись-считывание" информация передается в регистр 12 или в регистр 14 в зависимости от поступившего на них разрешения с блока 11.

Если, к примеру, информация поступила в регистр 12, то она запись вается в блок 17, при этом адрес записи постоянно меняется с помощью счетчика. 25

После заполнения блока 17 по сигналу, пришедшему с выхода блока 11, информация через регистр 13 поступаBY на входы распределителя 3 и далее через элементы И 28 по сигналу разре- д0 шения, пришедшему на вход 31 распределителя 3, подается в блок 1 и кодер 2. В то же время информация заполняет блок 18 по аналогичным сигналам, поступающим на него с блока 11. За счет этого повышается быстродействие устройства при записи, а аналогичным образом и при считывании информации из блока 1 в случае, когда период работы блока 1 больше периода работы 40 интерфейса.

В режиме считывания из блока 4 информация поступает на вход распределителя 3, на входы элементов ИЛИ-И

36 и далее на входы регистра 12 и на входы блока 17, а после его заполнения - на входы регистра 14 и далее в блок 18. Управление распределением заполнения регистров и блоков памяти осуществляется сигналами с блока 11, После заполнения блока 17 информация по сигналу, пришедшему с выхода блока

11 через регистр 13 поступает íà.sxo-. ды,элементов 27 и далее на шину 8, на циклический сумматОр 9 и на блОк 10, Иа циклическом сумматоре . 3 подсчитывается контрольная сумма массива информации, а в блоке 10 сравнения контрольная сумма сравнивается со считанной из блока 1 (контрольная сумма массива записывается в блок 1 е ре, 1ме записи). При несравнении контрольных сумм вырабатывается сигнал "" гибка", который поступает на вход гаспределителя 3 и далее на элемент ИЛИ 1g а затем как сигнал неисправности - в шину 16. За счет этого, если даже информация, поступившая из шины 8 на кодер 2, будет уже искажена, циклический сумматор g подсчитывает сумму массива и после сравнения с контрольным кодом, который замыкает массив, с помощью блока 10 будет определена ошибка, пропущенная при коррекции, формула изобретения

Запоминающее устройство с идентификацией ошибок, содержащее блок памяти, кодер, декодер, формирователь синдромсв„ анализатор синдромов, блок коррекции и. блок управления, причем информационный вход блока памяти подключен к выходу кодера, выход блока памяти подключен к информационному входу блока коррекции и входу декодера, вы" ход которого соединен с входом формирователя си-:. дрома, выход формирователя синдрома соединен с входом анали" затора синдрома, первый выход которого подключен к управляющему входу блока коррекции, входы начальной установ" ки, записи-считывания и вход "Старт" блока управления являются одноименными входами устройства, о. т л и ч а ющ е е с я тем, что, с целью повышения быстродействия и надежности уст" ройства, в него введены первый и второй блоки буферной памяти, циклический сумматор, блок сравнения и распределитель сигналов, причем первый выход распределителя сигналов соединен с входом записи-считывания блока памяти и управляющим входом кодера, второй выход распределителя сигналов подключен к установочным входам блока коррекции и кодера, третий выход распределителя сигналов подключен к информационному входу циклического сумматора, первому информационному входу блока сравнения l1 является информационным выходом устройства, четвертый выход распределителя сигналов соединен с информационными входами первого и второго блоков буферной памяти, пятый выход распределителя сигналов является выходом "Ошибка" устройства, второй информационный вход блока

1 г43676 сравнения подключен к выходу цикли ческого сумматора, первый информационный вход распределителя сигналов подключен к выходу блока коррекции, 5 второй информационный вход распределителя сигналов является информационным входом устройства, вход записи.считывания распределителя сигналов соединен с одноименным входом устрои- О

;ства, вход "Разреыение записи" и ус тановочный вход распределителя сигналов являются одноименными входами ,устройства, выходы первого и второго блоков буферной памяти бъединены и 15 подключены к третьему информационному, входу распределителя сигналов, первый и второй входы "Ошибка" распределителя сигналов подключены соответственно к выходу блока сравнения и второму 2р

,выходу анализатора синдрома, первый выход блока управления подключен к входам сброса циклического сумматора„ первого и второго блоков буферной памяти и распределителя сигналов, вто- 25 рой выход блока управления соединен с входами разрешения выдачи первого и второго блоков буферной памяти, третий и четвертый выходы блока управления подключены соответственно к входам разрешения приема первого и второго блоков буферной памяти, пятый выход блока управления является выходом "Готовность" устройства, шестой и седьмой выходы блока управления подключены соответственно к управляющему входу блока сравнения и входу

"Блокировка коррекции" распределителя сигналов, восьмой, девятый и десятый выходы блока управления соединены соответственно с адресным входом, входом обращения и входом записи-считывания первого блока буферной памяти, одиннадцатый, двенадцатый и тринадцатый вымоды блока управления соединены соответственно с адресным входом, входом обращения и входом записи-считывания второго блока буферной памяти, входы "Счет" и "Блокировка коррекции" блока управления являются одноименными входами устройства.

1541676

E5(0m 1Е) Составитель В. Рудаков

Редактор А. шандор Техред Л.Серд окова Корректор И. Самборская

Заказ 205 Тираж 488 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина,101