Комбинационный сумматор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ. Цель изобретения - упрощение комбинационного сумматора на МОП-транзисторах с индикацией моментов окончания переходных процессов. Комбинационный сумматор содержит в каждом разряде двадцать восемь МОП-транзисторов, четыре нагрузочных элемента и четыре элемента НЕ. Сигналы на парафазных выходах суммы сумматора используются для индикации моментов окончания переходных процессов. 1 ил.

CO)03 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5))5 С 06 F 7/50

ОПИСАНИЕ ИЗОБРЕТЕНИ

К А BTGPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

flO ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21 ) 43431 61 /24-24 (22) 17 . 1 ),87 (46) 15. 02. 90. Бюл. ))- 6 (7) ) Ленинградский электротехнический институт им. В. И. Ульянова (Ленина) (72) В.И.Варглавский, А,N.Êoíäðàòüåâ, Н.N.Êðàâ÷åíêo и Б.С.Цирлин (53) 681.325.5 (088 ° 8) (56) Авторское свидетельство СССР

Vi- 1411737, кл. С 06 Р 7/50,29.01.87, Авторское свидетельство СССР

9 1465881, кл. С 06 Г 7/50,09.03,87, Изобретение относится к вычислительной технике и может быть использовано в процессорах цифровых ЭВМ.

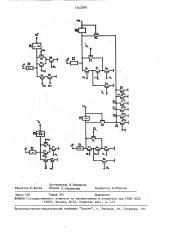

Цель изобретения — упрощение комбинационного сумматора на NOII-транзисторах с индикацией моментов окончания переходных процессов, На чертеже представлена схема одного разряда комбинационного сумматора.

Каждый разряд комбинационного сумматора содержит 1 ОП-транзисторы 1

28, нагрузочные элементы 29 — 32, элементы НЕ 33 — 36, входы прямых и инверсных значений первого а, а и второго b, Ь слагаемых и переноса иэ предыдущего разряда р, р, выходы прямых и инверсных значений суммы данного разряда s, s и переноса -в — c следующий разряд р, р

„,ЯО„„154 399 А 3

2 (54) КОМБИНАПИОНН))И СУММАТОР (57) Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ. Пель изобретения — упрощение комбинационного сумматора на МОЛ-транзисторах с индикацией моментов окончания переходных процессов. Комбинационный сумматор содержит в каждом разряде двадцать восемь МОЛ-транзисторов, четыре нагрузочных элемента и четыре элемента HE. Сигналы на парафазных выходах суммы сумматора используются для индикации моментов окончания переходных процессов. ил.

Сумматор работает следующим образом.

В интервалы времени между двумя laeaL последовательными суммированиями сумматор находится в инертном состоя- ф нии, лри котором на входы кажцого СФ разряда подается нулевая комбинация © входных сигналов: . a=a=b b p p O. При этом все транзисторы 1 — 28 закрыты и на выходах устанавливаются нулевые значения s= s= р = p О.

Если на входы разряда сумматора подается единичный рабочий набор сигналов a b=p=) и a=b=p=0, то транзисторы 1 - 8 открываются и на входах элементов НЕ ус танавливается значение потенциаЛа, соответствующее логическому "0", а на их выходах р и s— значение "1". При этом открывается транзистор 23 и поскольку транзисто15ч3399 ры 9, 25 и 27 также открыты, на входе элемента HE 35 сохраняется значение "0" до . тех пор, пока все входы сумматора не возвратятся в инертное, состояние.

Если на входы разряда сумматора подается нулевой рабочий набор сигналов а"b=p=p и а=Ър 1, то открываются транзисторы 12 — 19 и на входах элементов HE 34 и 36 появляется зна-!! !! — ю чение О, а на их выходах р и s— значение "1". При этом открывается транзистор 24 и поскольку транзисторы 20, 26 и 28 также открыты, на вхо" 15 де элемента НЕ 36 сохраняется значение "0" до тех пор, пока все входы сумматора не возвратятся в инертное состояние.

Если на входы разряда сумматора 20 подается рабочий набор сигналов, в, котором значение "1" появляется на одном прямом и двух инверсных входах (например, a=b=p=l и a b=p=0), то на входе элемента НЕ 34 устанавливается 25 значение "0", а на его выходе р значение "1", в результате чего откроются транзисторы 10 и 11 и на входе элемента НЕ 35 установится значение !!р!!, а на его выходе з — значе- 30 ние "1", При этом открывается транзистор 23 и поскольку открыты также транзисторы 20, 25 и 28, значение "О" на входе элемента HE 35 будет сохраняться до тех пор, пока все входы сумматора не возвратятся в инертное состояние, Если на входы разряда сумматора подается рабочий набор сигналов, в 40 котором значение "1" появляется на двух. прямых и одном инверсном входе (например, а=Ь=р=l и аЬ=р=0), то на входе элемента НЕ 33 появляется значение "О", а на его выходе р — значение "1", в результате чего откроются транзисторы 21 и 22 и на входе элемента НЕ 36 установится значение

"0", а на его выходе s — значение

При этом открывается тРанзистоР

24 и поскольку открыты также и транзисторы 20 25 и 27, значение "0" на входе элемента НЕ 36 будет сохраняться до тех пор, пока все входы сумматора не возвратятся в инертное состояние.

Таким образом, рабочее состояние выходов в и s каждого разряда. устанавливается только после того, как все его входы перейдут из инертного состояния в рабочее. При этом рабочее состояние выходов переноса в следую° « щий разряд pl и р проверяется в следующем разряде. Так как переход выходов s u s каждого разряда в инертное состояние происходит только после того, как на всех его входах установится инертное состояние, сигналы с выходов s u s могут использоваться в качестве сигналов завершения переходных процессов в сумматоре, Формула изобретения

Комбинационный сумматор, содержащий в каждом разряде четыре элемента

НЕ! четыре нагрузочных элемента и двадцать восемь МОП-транзисторов, причем затворы первого, второго и третьего транзисторов объединены и подключены к прямому входу первого слагаемого, затворы четвертого, пятого и шестого транзисторов — к прямому входу второго слагаемого, затворы седьмого, восьмого и девятого транзисторов — к прямому входу переноса из предьдущего разряда, затворы десятого, одиннадцатого транзисторов и выход первого элемента НŠ— к инверсному выходу переноса в следующий разряд, затворы двенадцатого, тринадцатого и четырнадцатого транзисторов к инверсному входу первого слагаемого, затворы пятнадцатого, шестнадца- того и семнадцатого транзисторов — к инверсному входу второго слагаемого, затворы восемнадцатого, девятнадцатого и двадцатого транзисторов — к инверсному входу переноса из предьдущего разряда, а затворы двадцать первого, двадцать второго транзисторов и выход второго элемента HE - к прямому выходу переноса в следующий разряд, истоки первого, второго и пятого транзисторов соединены с первым выводом первого нагрузочного элемента и входом второго элемента НЕ, истоки двенадцатого, тринадцатого и шестнадцатого транзисторов соединены с первым выводом второго нагрузочного элемента и входом первого элемента НЕ, стоки первого и двенадцатого транзисторов соединены с истоками соответственно. четвертого и пятнадцатого транзисторов, стоки второго и пятого транзисторов соединены с истоком седьмого транзистора, а стоки

1543399 тринадцатого и шестнадцатого транзисторов — с истоком восемнадцатого транзистора, истоки третьего и одиннадцатого транзисторов соединены с первым выводом третьего нагрузочного

5 элемента . и входом третьего элемента

НЕ, выход которого соединен с прямым выходом суммы данного разряда и затвором двадцать третьего транзистора,, 1„-. истоки четырнадцатого и двадцать второго транзисторов соединены с первым выводом четвертого нагрузочного элемента и входом четвертого элемента

НЕ, выход которого соединен с инверсным выходом суммы данного разряда и затвором двадцать четвертого транзистора, сток третьего транзистора соединен с истоками шестого и десятого транзисторов, а исток восьмого транзистора — со стоками шестого и одиннадцатого транзисторов, сток четыр- надцатого транзистора соединен с истоками семнадцатого и двадцать первого транзисторов, а исток девятнадца- 25 того транзистора, — со стоками семнадцатого и двадцать второго транзисторов, вторые выводы нагрузочных элементов подключены к шине питания сумматора, а стоки четвертого, девятого, пятнадцатого и двадцатого транзисторов — к его общей шине, о т л и— ч а ю шийся тем, что, с целью упрощения, в каждом его разряде прямые и инверсные входы первого и.вто-. рого слагаемых подключены к затворам соответственно двадцать пятого, двадцать шестого, двадцать седьмого и двадцать восьмого транзисторов, истоки которых соединены между собой и с истоками девятого, двадцатого, двадцать третьего и двадцать четвертого транзисторов, стоки седьмого, восьмого, десятого, восемнадцатого, девятнадцатого, двадцать первого, двадцать пятого, двадцать шестого, двадцать седьмого и двадцать восьмого транзисторов объединены и подключены к общей шине сумматора, стоки двадцать третьего и двадцать четвертого транзисторов соединены с входами соответственно третьего и четвертого элементов НЕ.

1543399

Составитель В,Черников

ТехРед Л. Сердюкова КоРРектоР А.0б РУчаР

Редактор Е.Копна

Заказ 401 Тираж 561 Подл исн се

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101