Логарифмическое вычислительное устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является повышение точности. Логарифмическое вычислительное устройство содержит логарифмические преобразователи 2, первый и второй операционные усилители 3 и 4, первый и второй усилительные транзисторы 5 и 6, первый и второй ограничительные диоды 7 и 8, первый и второй двухполюсники с отрицательным сопротивлением 9 и 10, антилогарифмирующий элемент 11, преобразователь ток-напряжение 12, блок контроля четности 13, шесть масштабных резисторов 14-19, два токоограничительных резистора 20 и 21, шину нулевого потенциала 22, две группы дополнительных масштабных резисторов 24, два токозадающих резистора 25 и 26, логарифмирующий элемент 27, операционный усилитель 28, блок выделения знака сигнала 29, переключатель полярности 30. Работа устройства основана на реализации логарифмического алгоритма вычисления произведения и отношения сигналов в степени. 3 ил.

СС ОЭ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (11) (51)5 С 06 С 7/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4275887/24-24 (22) 29.05.87 (46) 15.02.90. Бюл. У б (71) Учебно-научно-производственный комплекс "Кибернетика" при Томском политехническом институте им. С.М.Кирова (72) К.И.Заподовников (53) 681.335(088.8) (56) Справочник по нелинейным схемам/Под ред. Д.Н1ейнголда. М.: Map,.

1977, с. 379-382, фиг. 3.6.2.

Авторское свидетельство СССР

В 1282163, кл. G 06 G 7/16, 1985. (54) ЛОГАРИФМИЧЕСКОЕ ВЫЧИСЛИТЕЛЬНОЕ

УСТРОЙСТВО (57) Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является повышение точности.

Логарифмическое вычислительное устГ

2 ройство содержит логарифмические преобразователи, первый и второй операционные усилители 3 н 4, первый и второй усилительные транзисторы 5 и

6, первый и второй ограничительные диоды 7 и 8, первый и второй двухполюсники с отрицательным сопротивлением 9 и 1О, антилогарифмнрувщий элемент ll преобразователь ток-напряжение 12, блок контроля четности 13, шесть масштабных резисторов 14-19, два токоограничительных резистора 20 и 21, шину нулевого потенциала 22, две . группы дополнительных масштабных резисторов 24,два токозадающих резистора

25 и 26, логарифмирувщий элемент 27, g операционный усилитель 28, блок выделения знака сигнала 29, переключатель полярности 30. Работа устройства основана на реализации логарифмического алгоритма вычисления произведения и отношения сигналов в степени. 3 ил. 2

3 1543425. Изобретение относится к электри"ческим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Цель изобретения — повышение точности

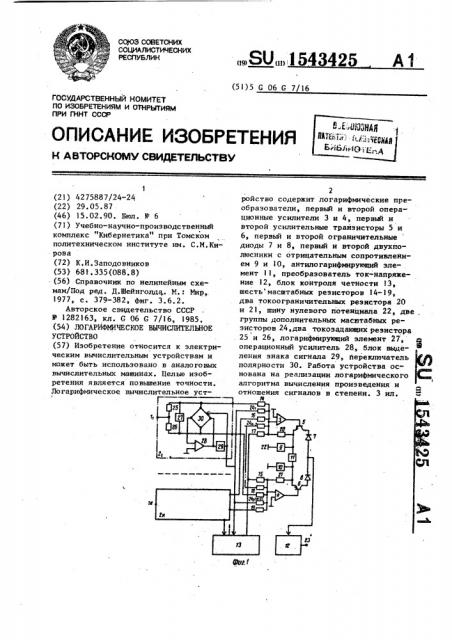

На фиг. l изображена функциональная схема логарифмического вычислительного устройства; на фиг. 2 и 3 —функциональные схемы переключателя полярности и двухполюсника с отрицательным сопротивлением.

Устройство содержит входы 1,..., 1„, логарифмические преобразователи

2,,...,2, первый 3 и второй 4 операционные усилители, первый 5 и второй

6 усилительные транзисторы, первый

7 и второй 8 ограничительные диоды, первьй 9 и второй 10 двухполюсники с отрицательным сопротивлением, антилогарифмирующий элемент ll,. преобразователь 12 ток — напряжение, блок l3 контроля четности, с первого по шестой масштабные резисторы 14-19, первый 20 и второй 21 токоограничительные резисторы, шину 22 нулевого потенциала, выход 23, первую группу

:дополнительных масштабных резисторов

24s,...,241„.g, вторую группу дополни- 30 тельных масштабных резисторов

24(eд „,...,24 <„э)» первый 25 и второй

26 токозадающие резисторы, логарифмирующий элемент 27, операционный усилитель 28, блок,29 выделения знака сигнала, переключатель 30 полярности„ первый 31 и второй 32 переключат4ли, первый 33 и второй 34 входы, первый 35 и второй 36 выходы, управляющий вход 37, операциоиюй усилитель 38, первый 39, второй 40 и третий 41 масштабные резисторы и первый

42 и второй 43 выводы.

Логарифмическое вычислительное устройство работает следующим образом.

Предположим, что работает один сквозной канал, состоящий из логарифмического преобразователя 2„, сумматора, образованного первым операционным усилителем 3 с соответствующими масштабными резисторами, блока 13 контроля четности, s качестве которого можно использовать, например, постоянное запоманающее устройство, выходного антилогарифмического узла, состоящего нз усилительных транзисторов 5 и 6, ограничительных диодов

7 и 8, двухполюсников 9 и 10 с отрицательным сопротивлением и антилогарифмирующего элемента 11.

При наличии на входе 1, положительного сигнала на выходе блока 29 выделения знака формируется "1", на выходе положительного суи нала логарифмического преобразователя 2, формируется напряжение, пропорциональное логарифму отношения сигнала с входа

11 и величины сопротивления второго токозадающего резистора 26. На выходе отрицательного сигнала логарифмического преобразователя 2, напряжение практически равно нулю. Напряжение. с этих выходов логарифмического преобразователя 2, инвертируется первым сумматором на первом операционном усилителе

3 и вторым сумматором на втором операционном усилителе 4 и к антилогарифмирующему элементу 11 прикладывается разность напряжений с первого и второго выходов. Ток антилогарифмирующего элемента 11 является антилогарифмом от логарифма отношения, т.е. пропорционален отношению сигнала с входа

1, к величине сопротивления второго токозадающего резистора 26.

Усилительные транзисторы 5 и 6 и ограничительные диоды 7 и 8 служат для передачи этого тока на вход преобразователя 12 ток — напряжение.

Так, для получения положительного напряжения на выходе 23 при инвертирующем преобразователе 12 ток — напряжение с выхода блока 13 контроля четности на операционные усилители

3 и 4 через масштабные резисторы 17 и 15 подается "1". Поступая одновременно на операционные усилители 3 и

4, это напряжение не изменяет ток антилогарифмирующего элемента 11, но вызывает отрицательное смещение на выходах этих усилителей, что приводит к включению первого усилительного транзистора 5 в режим повторителя тока. Ток протекает через эмиттер и коллектор усилительного транзистора 5, ограничительный диод 7 на вход преобразователя 12 ток — напряжение. Паразитную утечку через первый токоограничительный резистор

20 компенсирует первый двухполюсник с отрицательным сопротивлением 9.

При изменении полярности сигнала на входе 1> на отрицательную на вы— ходе операционного усилителя 28 также изменяется знак, что регистрируется блоком 29 выделения знака и на

15 его выходе устанавливается "0". С помощью переключателя полярности 30 создается цепь для прохождения сигнала: первый токозадающий резистор

25, логарифмирующий элемент 27. Сигнал логарифмического преобразователя. 2, формируется на выходе отрицательного сигнала. Этот сигнал пропорционален логарифму отношения модуля величины сигнала с входа 1, и величины сопротивления первого токозадающего резистора 25. Разностное напряжение между выходами логарифмического преобразователя 2, через сумматоры поступает на антилогарифмирующнй элемент ll, не изменяя его тока.

На выходе блока 29 выделения знака устанавливается "0". Являясь синфазным, это напряжение одинаково смещает выходные сигналы операционных усилителей 3 и 4 в область положительных напряжений, что приводит к включению усилительного транзистора 6 в режим повторителя тока.Ток протекает через эмиттер и коллектор и второй ограничительный диод 8 на вход преобразователя 12 ток — напряжение. Так как направление тока относительно входа преобразователя 12 оказывается противоположным, то знак напряжения на выходе 23 меняется на противоположный.

На выходе 23 формируется напряжение, пропорционапьное произведению сигналов на их отношение в степени, определяемой числом каналов.

Ф о р м у л а изобретения

Логарифмическое вычислительное уетройство, содержащее первый и второй операционные усилители, к инвертирующим входам которых подключены первые выводы соответственно первого и второго масштабных резисторов, третий и четвертый масштабные резисторы, первые выводы которых соединены между собой, пятый и шестой масштабные резисторы, первые выводы которых соединены между собой, неинвертирующие входы первого и второго операционных усилителей подключены к шине нулевого потенциала, первый усилительный транзистор, эмиттер которого соединен с первым выводом первого токоограничительного резистора, второй усили" тельный транзистор, эмиттер которого

43425 6 соединен с первым выводом второго токоограничительного резистора, первый и второй ограничительные диоды, антилогарифмирующий элемент, N логарифмических преобразователей, каждый из которых содержит операционный усилитель, логарифмирующий элемент, первый и второй токозадающие резисторы, неинвертирующий вход операционного усилителя соединен с шиной нулевого потенциала, первый вывод первого токозадающего резистора является информационным входом логарифмического преобразователя, второй вывод первого токозадающего резистора соединен с первым выводом логарифмирующего элемента, о т л .и ч а ю щ е е с я тем, что, с целью повышения точности, в него введены блок контроля четности, преобразователь ток — напряжение, первый и второй двухполюсники с отрицательным сопротивлением, две группы дополнительных масштабных резисторов, 25 а в каждый логариФмический преобразователь введены блок выделения знака сигнала и переключатель цолярнос" ти, причем в каждом логарифмическом преобразователе первый вывод первогО

3р токозадающего резистора через второй токозадающий резистор соединен с вторым выводом логарифмирующего элемента, первый и второй выводы которого соединены соответственно с первым и вторым входами переключателя полярности и являются соответственно выходами положительного и отрицательного сигналов логарифмического преобразователя, первый и второй выходы

4О переключателя полярности подключены соответственно к инвертирующему входу и выходу операционного усилителя выход которого соединен с вхоЭ дом блока выделения знака сигнала, выход которого подключен к управляющему входу переключателя полярности и является импульсным выходом логарифмического преобразователя, первый вывод третьего масштабного резис5О тора соединен с инвертирующим вкодом первого операцирнного усилителя, к выходу которого подключена база первого усилительного транзистора, первый вывод пятого масштабного резистора соединен с иивертирующим входом второго операционного усилителя ° к выходу которого подключена база второго усилительного транзистора, первые выводы первой группы дополнительf 543425

Составитель О.Отраднов

Т ех ред я . диды к, Корректор В, Гирняк

Редактор Л.Пчолииская

Заказ 402 Тираж 555 Подписное, ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

1 13035„ Иосква, Ж-35 Раушская иаб., д. 4!5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101

Ь ных масштабных резисторов соединены с инвертирующим входом первого операционного усилителя, первые выводы второй группы дополнительных масштабных резисторов соединены с инверти5 рующим входом второго операционного усилителя, выходы положительного сигнала логарифмических преобразователей подключены к вторым выводам соответственно первого, третьего масштабных резисторов и соответствующих дополнительных масштабных резисторов первой гщтпны, выходы отрицательного сигнала логарифмических преобразова15 ,телей подключены к вторым выводам со ответственно пятого, шестого масштабных резистсров и соответствующих дополнительных масштабных резисторов второй группы, импульсные выходы лога-20

\рифмических преобразователей соединены с соответствующими входами блока контроля четности, выход которого подключен к вторым выводам второго и четвертого масштабных резисторов, 25 второй вывод первого токоограничительного резистора соединен с инвертирующим входом. первого операционного усилителя, второй вывод второго токоограничительного резистора соединен с инвертирующим входом второго операционного усилителя, эмиттер первого усилительного транзистора соединен с первым выводом антилогарифмирующего элемента и через первый двухполюсник с отрицательным сопротивлением подключен к шине нулевого потенциала эмиттер второго усилительного транзистора соединен с вторым выводом антилогарифмирующего элемента и через второй двухполюсник с отрицательным сопротивлением подключен к шине нулевого потенциала, коллектор первого усилительного транзистора соединен с катодом первого ограничительного диода, к аноду которого подключен катод второго ограничительного диода и вход преобразователя ток — напряжение, выход которого является выходом логарифмического вычислительного устройства,, анод второго ограничительного диода соединен с коллектором второго усилительного транзистора, информационные входы логарифмических преобразователей являются входами логарифмического вычислительного уст- ройства.