Преобразователь форматов чисел

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении преобразователей чисел с плавающей запятой. Целью изобретения является расширение класса решаемых задач за счет обеспечения преобразования чисел с плавающей запятой в системы с различными большими основаниями. Поставленная цель достигается тем, что в преобразователь форматов чисел, содержащий сумматор порядка 1, блок деления 4, коммутатор-сдвигатель 6, формирователь дополнительного кода 12, формирователь дополнительного кода 12, введены вычитатель по модулю три и сумматор по модулю пять, входы которых соединены с входом 11 коэффициента увеличения основания преобразователя. 1 ил.

СОЮЭ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ ,РЕСПУБЛИН (19) (И) (51) 5 Н 03 М 7/12

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ (21) 4243843/24-24 (22) 19.03.87

, (46) 15. 02. 90. Бюл. tt- 6 (72) В.Г.Евстигнеев и А.Н.Кошарновский (53) 681.325(088.8) (56) Авторское свидетельство СССР

Р 717755, кл. Н 03 М 7/ 12, 1977.

Авторское свидетельство СССР

В 14766 15, кл. Н 03 M 7/12, 1986 . (54) ПРЕОБРАЗОВАТЕЛЬ ФОРМАТОВ ЧИСЕЛ (57) Изобретение относится к вычислительной технике и может быть использовано при построении преобразо2 вателей чисел с плавающей запятой.

Целью изобретения является расширение класса решаемых задач за счет обеспечения преобразования чисел с плавающей запятой в системы с различными большими основаниями. Поставленная цель достигается тем, что в преобразователь форматов чисел, содержащий сумматор 1 порядка, блок 4 деления, коммутатор-сдвигатель 6, введены образующие формирователь 12 дополнительного кода вычитатель 3 по модулю и сумматор 5 по модулю, входы которых соединены с входом 11 коэффициента увеличения основания преобразователя. 1 ил.

1543550

-%

А = А, S ° . (1) 45

Ч + Ч

q (m — L) (mod m) L = q (шос1 и) Окончательное Б -ичное значение мантиссы А получается разбивкой

I двоичного представлЬния мантиссы А на группы по m S< -ичных разрядов.

Преобразователь работает следующим образом.

По входам 1, 11, 9 и 8 на устрой.Ство подаются порядок q» числа с плавающей .запятой, величина m называемая коэффициентом увеличения осИзобретение относится к вычислительной технике и может быть использовано ггри построении преобразоватеsIeA чисел с плавающей. запятой.

Цель изобретения — расширение класСа решаемых задач за счет обеспечеНия преобразования чисел с плавающей запятой в системы с различными большими основаниями.

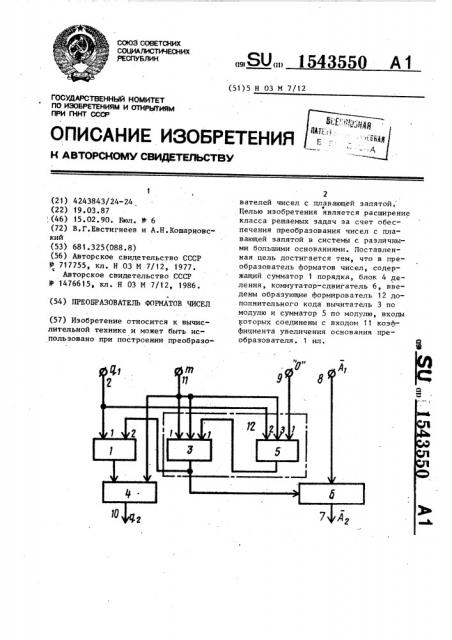

10 EIa чертеже приведена блок-схема

1 редлагаемого преобразователя.

Преобразователь содержит сумматор порядка, вход 2 порядка преобразователя, вычитатель 3 по модулю, блок

Р деления, сумматор 5 по модулю, коммутатор-сдвигатель 6, выход 7 антиссы преобразователя, вход 8 маниссы преобразователя, вход 9 логи еского нуля преобразователя, выход

1 0 порядка преобразователя и вход 11 оэффициента увеличения основания реобразователя.

Вычитатель.3 по модулю в совокупг1ости с сумматором 5 по модулю обра1уют формирователь 12 дополнительног е кода.

В основу работы предлагаемого устройства положено следующее.

Пусть число в позиционной систе- Ме счисления с основанием S< в форме ;

% с, плавающей запятой вида А = А; $, требуется перевести в представление

cI плавающей запятой с основанйем Б ида A = А, S, где S.,1, S< вания систем счисления; q — S -ичый порядок числа А; А - S -ичная антисса числа А, q - S -ичный порядок числа А", А — Я -ичная мантисс а числа А.

11 40

IIoJloKHM 8 = S, (m = 2,3, в е ° ) °

Itðè сделанных допущениях можно запис, ать нования, константа нуль и S -ичная мантисса А . Ha o Tope 5 rro моду{ лю вычисляется величина L=qI (mod m) которая поступает на вход вычитателя 3 по модулю, где вычисляется величина q = (m — I.) (mod m). Величина q с выхода вычитателя 3 по.моду.лю поступает на вход сумматора 1 порядка, где вычисляется сумма q, +q, поступающая на вход блока 4 деления, вычисляющего величину q< = (q< +

+ q)/m, которая поступает на выход

10 преобразователя. Одновременно величина q с выхода вычитателя 2 по модулю поступает на,,управляющий вход коммутатора-сдвигателя б,наполняющего операцию сдвига мантиссы числа на q S -ичных разрядов вправо, т.е. вычисляется А = А S. !

В таблице для S, = 16 и различных значений S представлены выражения для вычисления величин q и А,,полученных из выражений (1).

Из таблицы следует, что при S

2 и S =- 2 или 2, т.е. при

В 46

m = 2 . блок 4 деления может быть выполнен как сдвиговый регистр, сдвигающий значение Ч + q на К двоич1 ных разрядов вправо.

Для S g = 2 из (1),.после подста(2. новки О = 4 и О = Mq q получим

К Б (modN), q (M — L) (modN), и алгоритм (1) принимает вид

4Ч,+q — — — А А, 2 г

Отсюда следует, что блок 4 деления и в этом случае может быть выполнен как сдвиговый регистр, сдвигающий двоичный код величины 4Ч, + q вправо на N двоичных разрядов. Коммутатор-сдвигатель 6 в этом случае выполняется как двоичный сдвиговый регистр сдвигающий мантиссу А.„ вправо на разрядов. Окончательное S --ичное значение мантиссы А получается разбивкой двоичного представления А< на группы по M.äâoè÷íûõ разрядов.

Формула из обре тения

Преобразователь форматов чисел, содержащий сумматор порядка, блок деления, формирователь дополнительного кода и коммутатор-сдвигатель, информационные входы и выходы которого соответственно являются входами и вьгходами мантиссы преобразователя,.

5 1543550 6 входы характеристики которого соеди- личными большими основаниями, в нем иены с первыми входами сумматора формирователь дополнительного кода порядка и входами характеристики фор- содержит сумматор по модулю и вычимирователя дополнительногЬ кода, . татель по модулю, вход вычитаемого

5 выходы которого соединены с управ- которого соединен с выходом сумматоляющими входами коммутатора-сдвигате- ра по модулю, первый вход которого ля и с вторыми входами сумматора соединен с входом логического нуля порядка, выходы которого соединены преобразователя, вход коэффициента с входами делимого блока деления, 10 увеличения основания которого соедивыходы которого являются выходами по-, нен с входом уменьшаемого вычитате- рядка преобразователя, о т л и ч а — ля по модулю, входом делителя блока ю шийся тем, что, с целью рас- деления и вторым входом сумматора ширения класса решаемых задач за по модулю, третий выход которого явсчет обеспечения преобразования чисел 15 ляется входом формирователя дополнис плавающей запятой в системы с раз- тельного кода.

Выражения для с и А

Значения

Я, m если q — четное (L = О)

-1

= А ° S, если q — нечетное (L = 1)

S =2

m= 2

12

S,-=г

m=3

L= 0

S,, если? = 1 — 2

Б,, если Ь = 2 если

12

Ц

-i

А

= А

$ 2

16

m= 4

L=0

А,, еслибы= 1

S +, если = 2

S< если L = 3

Ч =

Я

Чч если

= А1

= А

= А

Составитель M.Àðøàâñêèé

Техред М,Ходанич Корректор В. Кабаций

Редактор A.Îãàð

Заказ 408 Тираж 656 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж 35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.Ужгород, ул. Гагарина, 101

q,/ã, (q +

q,/3, (q + (q +

q,/4, (q, + (q + (q +

А<= А,, 1)/<, А

А А, 2) /3, А

1)/3, А

А = А, 3)/4, А

2) /4, А

1)/4, А