Устройство для приема частотно-фазовых сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике. Цель изобретения - упрощение устройства путем сокращения числа функциональных блоков. Устройство содержит частотный детектор 1, линию задержки 2, интеграторы 3 и 8, блок 4 выделения несущей, фазовый детектор 5, АЦП 6 и 10, г-р 7 частот, ключевой блок 9, г-р 11 синхрокомбинации, регистр 12, блок 13 сумматоров дискретный согласованный фильтр 14 и блок коррекции (БК) 15. При правильном выделении синхрокомбинации фильтром 14 через каждые N тактов в БК 15 будет производиться суммирование символов N-разрядных информационных слов с символами коррекции. Этим достигается устранение влияния скачков фазы опорного колебания на верность информационных символов в фазовом подканале устройства. Эти скорректированные информационные символы с БК 15 поступают на выход устройства. Цель достигается введением БК 15, позволяющего сократить число функциональных блоков устройства. 2 ил.

СОЮЗ СОВЕТСНИХ

СООИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51) 5 H 04 L 27/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМ,Ф СВИДЕТЕЛЬСТВУ

Рыхл

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4350564/24-09 (22) 02.11.87 (46) 15.02.90. Бюл. И 6 (71) Харьковский политехнический институт им. В,И. Ленина (72) А.А. Серков, И.А. Иванов, И.И. Сватовский и В.Н. Верба (53) 621.334.62(088.8) (56) Авторское свидетельство СССР

И 1425868, кл. Н 04 L 27/22, 17.03.87 (54) УСТРОЙСТВО ДЛЯ ПРИЕМА ЧАСТОТНОФАЗОВЫХ СИГНАЛОВ (57} Изобретение относится к радиотехнике. Цель изобретения — упрощение устр-ва путем сокращения числа функциональных блоков. Устр-во содержит частотный детектор 1, линию задержки 2, интеграторы 3 и 8, блок. SU,» 1543563 A 1

4 выделения несущей, фазовый детектор 5, АЦП 6 и 10 г-р 7 частот, ключевой блок 9, г-р 11 синхрокомбинации, регистр 12, блок 13 сумматоров, дискретный согласованный фильтр 14 и блок коррекции (БК) 15. При правильном выделении синхрокомбинации фильтром 14 через каждые N тактов в ВК 15 будет производиться суммирование символов N-разрядных информационных слов с символами коррекции.

Этим достигается устранение влияния скачков фазы опорного колебания .на верность информационных символов в фазовом подканале устр-ва. Эти скорректированные информационные символы с bK 15 поступают на выход устрва. Цель достигается введением БК 15, позволяющего сократить число функциональных блоков устр-ва. 2 ил.

Ю% РИ1 Х

Йииь!

543563

Данное напряжение интегрируется за время такта первым интегратором 3, передаточная функция которого определяется выражением

10 v„= — -„- ) v„(t)at, (3)

1 а где С - постоянная времени интегрирования.

Напряжение с выхода первого интегратора поступает на вход первого аналого-цифрового преобразователя (АЦП) 6, который преобразует данное напряжение а последовательность двоичных символов (код), соответствующую

20 частоте принятого элемента сигнала.

Данный код поступает на первый выход устройства.

Линия 2 задержки производит задержку сигнала на время t равное с

2:;. длительности обработки элемента сиг нала в частотном подканале устройства (на один такт). Задержанный на один такт сигнал поступает на вход

ы - соответственно круговая часо о 55 тота и начальная фаза несу;щего колебания;

dogt) " закон изменения частоты сигнала; дЦ (t) ---закон изменения фазы сигна" ла.

Я

C входа устройства сигнал поступает на вход частотного детектора 1 и унию 2 задержки. На выходе частот-! ного детектора 1 формируется напряжение, которое является функцией отклонения значения частоты принимаемого элемента сигнала (т.е. сигнала, принимаемого за тактовый инИзобретение относится к радиотехнике и может быть использовано в радиотехнических системах передачи дискретной информации для приема частотно-фазовых сигналов.

Цель изобретения - упрощение устройства путем сокращения числа функциональных блоков.

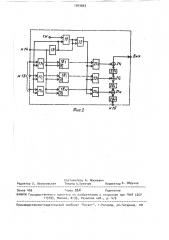

На фиг. 1 представлена структурная электрическая схема предпоженного устройства; на фиг. 2 - вариант выполнения блока коррекции.

Устройство для приема частотнофазовых сигналов (фиг. 1) содержит частотный детектор 1, линию 2 задержки, первый интегратор 3, блок 4 выделения несущей, фазовый детектор 5, первый аналого-цифровой преобразователь 6, генератор 7 частот, второй интегратор 8, ключевой олок 9, вто-, рой аналого-цифровой преобразователь

10> генератор 11 синхрокомбинации, регистр 12, блок 13 сумматоров, дискретный согласованный фильтр 14 и блок 15 коррекции.

Блок 15 коррекции (фиг. 2) содержит Т-триггер 16, элементы И 17,17ц, JK-триггер 18,-18„, счетчик 19, дойолнительные Т-триггеры 20„- 20, сумматоры по модулю два 21,-21, элемент ИЛИ 22 и дополнительные элементы И 231-23q.

Устройство работает следующим образом. йа вход устройства, т.е. на входы частотного детектора 1 и линии 2 задержки, поступает частотно-фазовый сигнал, который можно представить а виде

$(с) А61п(ы t+ лы(3) с1 :+Щ(")+ Ч,1 (1) о где А - амплитуда огибающей сигнала;

I тераал) f от частоты настройки частотного детектора 1 лп= лм (с — н) ° блока 4 выделения несущей, а котором производится когерентная подстройка колебания опорного генератора (не показан) по принятому сигналу. Данное опорное колебание поступает на вход генератора 7 частот, формирующего сетку опорных колебаний. Одно из этих колебаний, частота которого равна частоте принятого элемента сигнала, через ключевой . блок 9 поступает на второй вход фазового детектора 5. На выходе фазового детектора 5 формируется напряжение, являющееся функцией разности фаз гфинятого, и опорного р,„ сигналов; чф,= +,(÷.-ч.„) ° (4)

Данное напряжение выделяется вторым интегратором 8 и поступает на вход второго АЦП 10, который преобразует его в код, соответствующий фазе принятого сигнала., Последовательность символов с выхода первого АЦП 6 поступает на вход дискретного согласованного фильтра

14, который формирует на своем выходе сигнал логической единицы только в случае совпадения поступающей на вход последовательности с образцовой синхрокомбинацией, поступающей с выходов генератора 11 синхрокомбинации.

5 15435

Последовательность символов с выхода второго АЦП 10 преобразуется регистром 12 в параллельный код и поступает на вторую группу входов блока 13 сумматоров, который поразрядно склады- вает по модулю два данный код с образцовой синхрокомбинацией, поступающей на первую группу его входов. 8 случае правильного выделения дискрет- 10 ным согласованным фильтром 14 пере-данной синхрокомбинации сигнал логической единицы с его выхода поступает на управляющий вход блока 15 коррекции, устанавливая в нулевое начальное 15 состояние JK-триггеры 18,-18 . Этот же управляющий сигнал задерживается

Т-триггером 16 на один такт (для обеспечения синхронности информационных потоков частотного и фазового: 20 подканалов, т.к. в фазовом канале уже была задержка на такт) и разрешает прохождение сигналов коррекции через элементы И 17, -17 на K-входы

JK-триггеров 18,-18, одновременно 25 обнуляя счетчик 19. Счетчик 19 является счетчиком по модулю N, т.е. при подсчете каждого N-ro тактового импульса на его выхоДе формируется сигнал логической единицы и счет-З0 чик 19 обнуляется.

Управляющий сигнал с выхода Т-триггера 16 или сигнал с выхода счетчика 19 через элемент ИЛИ 22 разрешает выдачу символов коррекции с выходов JK-триггеров 18,-18 через дополнительные элементы И 23„ -23 на сумматоры по модулю два 21„-21„.

Таким образом, при правильном выделении синхрокомбинации дискретным согласованным фильтром 14 через каждые N тактов в блоке 15 коррекции будет производиться суммирование символов N-разрядных информационных слов, поступающих на вторые входы соответ- 45 ствующих сумматоров по модулю два

21, -21, с символами коррекции с выходов дополнительных Т-триггеров 20„20, поступающими на первые их входы, чем достигается устранение влияния скачков фазы опорного колебания на верность информационных символов в фазовом подканале устройства. Скорре ктирова нные информа цион ные символы с выхода блока 15 коррекции поступают на второй выход устройства.

Формула изобретения

Устройство для приема частотнофазовых сигналов, содержащее последовательно соединенные частотный детектор, первый интегратор, первый аналого-цифровой преобразователь и ключевой Ьлок, сигнальwe входы и выход которого соединены соответственно с выходами генератора частот и с одним входом фазового детектора, другой вход и выход которого соединены соответственно с выходом линии задержки, который подключен к входу блока выделения несущей, и с входом второго интегратора, выход которого через второй аналого-цифровой преобразователь подключен к входу регистра, выходы которого соединены с одними входами блока сумматоров, другие входы которого соединены с выходами генератора синхрокомбинации и с одними входами дискретного согласованного фильтра, к другому входу которого подключен выход первого аналого-цифрового преоЬразователя, который является первым выходом устройства, входом которого является вход частотного детектора, который соединен с входом линии задержки, о тл и ч а ю щ е е с я тем, что, с целью упрощения устройства путем сокращения числа функциональных блоков, введен блок коррекции, сигнальный и управляюц1ий входы которого соединены соответственно с выходом второго. аналого-цифрового преобразователя и с вы" ходом дискретного согласованного фильтра, при этом выход блока выделения несущей подключен к входу генератора частот, а выходы блока сумматоров соединены с корректирующими вхо»» дами блока коррекции, выход которого является вторым выходом устройства.

15435б3

gu/Х.

Составитель A. Москевич

Редактор Л. Веселовская Техред A.Кравчук Корректор А. 06РУчаР

Заказ 409 Тираж Ч 6 Подписное

ВНИИПИ Государственного комитета по изобретениям .и открь тиям лри ГКНТ СССР

113035, Иосква, Н-35, Раушская наб., д, 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул,Гагарина, 101