Устройство для реализации булевых функций

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и предназначено для реализации булевых функций. Цель изобретения - упрощение устройства. Устройство для реализации булевых функций содержит регистр 1, счетчик 2, генератор тактовых сигналов 3, блок 4 определения области функции и логическую схему 5 реализующую ДНФ. В течение каждого такта синхронизации N-разрядные двоичные коды(N-число аргументов булевой функции) с выходов регистра 1 и счетчика 2 поступают на соответствующие входы блока 4 определения области функции, код результата преобразования поступает на входы логической схемы 5, реализующей ДНФ и осуществляющей реализацию очередной функции. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛ ИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU„„154521 (51) 5 G 06 F 7 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

° °

° °

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

И А BTOPCHOMV СВИДЕТЕЛЬСТВУ

1 (21) 4324496/24-24; 4336900/24-24 (22) 09 ° 10.87 (46) 23.02,90. Бюл, Р 7 (71) Могилевский, машиностроительный институт и Могилевская областная больница (72) Б.Я,Советов, С.А,Яковлев, Г,В.Куклин, Н,А.Вислович и В.Г.Борозна (53) 681.3 (088.8) (56) Авторское свидетельство СССР

9 1032451, кл. G 06 Р 7/00, 1982.

Авторское свидетельство СССР

11 1418696, кл. G 06 F 7/00, 1987. (54) УСТРОЙСТВО ДЛЯ РЕАЛИЗАЦИИ

БУЛЕВЫХ ФУНКЦИЙ (57) Изобретение относится к автоматике и вычислительной технике и

2 предназначено для реализации булевых функций. Цель изобретенияI упрощение устройства. Устройство для реализации булевых функций содержит регистр 1, счетчик 2, гене-, ратор тактовых сигналов 3, блок

4 определения области функции и логическую схему 5, реализующую ДНФ.

В течение каждого такта синхронизации и-разрядные двоичные коды (n- число, аргументов булевой функции) с выходов регистра 1 и счетчика

2 поступают на соответствующие входы блока 4 определения области функции, код результата преобразования поступает на входы логической схемы 5, реализующей ДНФ и осуществляющей реализацию очередной функции. 1 ил.

1545212 эультат преобразования поступает на входы логической схемы 5, реализующей ДНФ, осуществляющей реализацию очередной функции, После того, как все булевые функции для набора, хранящегося в регистре 1, реалйэованы, счетчик 2 обнуляется и формирует управляющий сигнал, разрешающий запись в.регистр йового двоичноro набора, присутствующего в этот момент на группе информационных входов 6 устройства. Процесс вычисления повторяется циклически, Составитель В,Сорокин

Редактор Г.Гербер Техред М,Ходанич Корректор N.Кучерявая в

Заказ 491 .Тираж 563 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.Ужгород, ул. Гагарина,!01

Изобретение относится к автоматике и вычислительной технике и предназначено для реализации булевых функций.

Цель изобретения — упрощение

5 устройства.

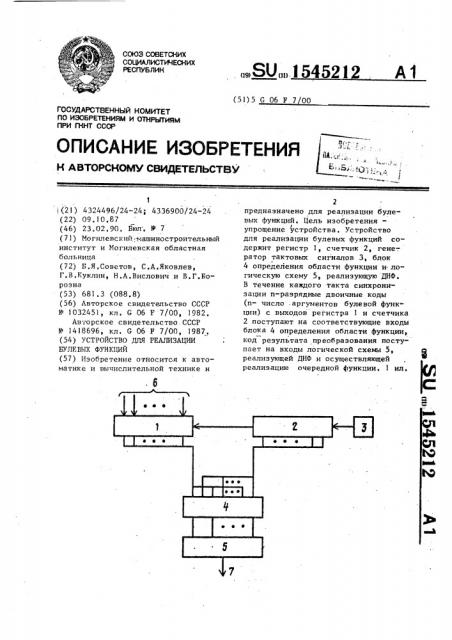

На чертеже представлена структурная схема устройства для реализации булевых функций.

Устройство содержит регистр 1, счетчик 2, генератор 3 тактовых сигналов, преобразователь 4 определения области функций, логическую схему

5, реалиэующую ДНФ, группу информационных входов 6 и выход 7.

Устройство работает следующим об" разом.

Блок 4 области определения функций может быть реализован, например, на основе сумматора .или элементов исключающее

ИЛИ, В начальный момент времени устройство находится в исходном состоянии: счетчик 2 обнулен и выдает 25

«3 управляющий сигнал, разрешающий прием входных данных в регистр 1. В момент запуска генератора 2 тактовых сигналов содержимое счетчика 2 увеличивается на единицу и его управляющий сигнал блокирует прием входных данных в регистр 1.

В течение каждого такта синхронизации и-разрядные двоичные коды (п — число аргументов булевой функ35 ции), хранящиеся в регистре 1 и счетчике 20 поступают на вход блока

2 области определения функций, РеФормула изобретения

Устроиство для реализации булевых функций, содержащее регистр, счетчик и логическую схему, реализующую

ДНФ, причем информационные входы группы устройства соединены с информационными входами регистра, вход разрешения записи которого соединен с управляющим выходом счетчика, вход разрешения счета которого соединен с тактовым входом устройства, выход логической схемы, реализующей

ДНФ, соединен с выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью упрощения, оно еодержит блок определения области функций, причем вход логической схемы, реализующий ДНФ, соединен с выходом блока определения области функций, первый и второй входи которого соединены соответственно с выходом регистра и информационным выходом с летчика,