Устройство для извлечения квадратного корня и его обратной величины

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для аппаратного вычисления квадратного корня и его обратной величины в избыточной системе счисления в форме с фиксированной запятой. Целью изобретения является повышение быстродействия устройства. Устройство позволяет потактно обрабатывать данные по мере их поступления и осуществлять одновременно коррекцию полученных результатов после каждой итерации. 1 ил.

СОЮЗ СОВЕТСНИК

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (51)5 G 06 F 7/552

ОПИСАНИЕ ИЗОБРЕТЕНИ

Н А BTOPCHOMV СВИДЕТЕЛЬСТВУ

Ч. при х (у1 !

0 при у.) х,.

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГННТ СССР (21 ) 4417074/24-24 (22) 18.04.88 (46) 23.02.90, Бюл. № 7 (71 ) Киевский институт инженеров гражданской авиации им. 60-летия

СССР (72) И.А. Жуков, Л.Я . Нагорный (SU), Джай Сингх (IH) и Жозеф

Бахендузи (BI) (53 ) 681 .323(088.8 ) (56) Авторское свидетельство СССР

¹ 732863, кл. G 06 F 7/552, 1978, Авторское свидетельство СССР № 1024914 кл. G 06 F 7/552, 1983.

Изобретение относится к вычислительной технике и может быть использовано для аппаратного вычисления квадратного корня и его обратной величины.

Цель изобретения — повышение быстродействия устройства.

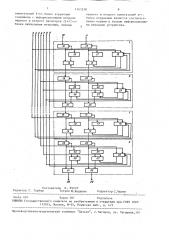

На чертеже представлена структурная схема устройства.

Устройство состоит из блоков 1 вычисления итерации, блоков.2 коррекции, синхровходов 3-8 устройства, входа 9 логического нуля, информационных входов 1 0 и li устройства; блоки 1 вычисления итерации содержат регистры 12 и 13, сумматоры 14 и 15, регистры 16 и 17 сдвига, блок 18 анализа разности; блоки 2 коррекции содержат регистры f9 и 20, вычитатели

„„SU„„1545218

2 (54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАД-, РАТНОГО КЦРНЯ И ЕГО ОБРАТНОЙ ВЕЛИЧИНЫ (57) Изобретение относится к вычислительной технике и может быть использовано для аппаратного вычисления квадратного корня и его обратной величины в избыточной системе счисления в форме с фиксированной запятой. Целью изобретения является повышение быстродействия устройства. Устройство позволяет потактно обрабатывать данные по мере их поступления и осуществлять одновременно коррекцию полученных результатов после каждой итерации. 1 ил.

21 и 22, регистры 23 и 24 сдвига, блок 25 анализа разности, коммутаторы 26 и 27, информационные выходы 28 и 29 устройства.

Вычисление квадратного корня и его обратной величины производится по алгоритму, содержащему разностные рекуррентные соотношения

- (1+11 х . = х. + q.,õ. 2

- (+ 1 гдех =х, у =1, х, у — значение после первого шага i-й итерации

1545218 — l»2,...,п порядковый номер итерации; число разрядов аргумента;

5 прямой и обратный код сигнала сравнения значений

1;» 4 ° у»

В результате получают

e у !»„= у !! х!

Известно, что при вычислениях с помощью алгоритма (:1) происходит удлинение значений на величину К. оп» ределяемую соотношением

+ 2: ) —" !

=!!

Таким образом, полученные значения х., у,, в К . раз больше истинного

1 1

i 1 ! значения длины вектора после поворота, поэтому необходима коррекция по- . лученных результатов, т ° е. необходимо

25 найти х. —, у . —, При правильно организованной операции деления должно выполняться равенство

Z

К» 30 где число Z — частное от деления может быть представлено в виде произи ведения, т.е. Z = P.. (1- C- ;2 ).

1 !=0

Torpa х .. ! х.Z= ! (l + 2 — 2! )- /2

i=a !

»

-1

=.х,. П (1 — G2 ) !

=о

1

1 — +.Z

П(1+2.) у,.!

y. II (1-G2 )

i-o

1"де,,-дс х ..., у ., — значение после первого шаг» 1-й интеО при х". с у" ! !

1 при у ) х1, 50

Тогда алгоритм (21 для коррекции полученных результатов при реализации алгоритма (1!

1 1 -i х" = х.-Гх. 2 1 1 у,,=у.,— Cy2

55 рации в результате коррекции.

Устройство р.!ботает следующим образом.

Рассматривают работу блока вычисления итерации. В первом такте в регистр 12 заносится по входу 10 значение x = х, в регистр 13 заносится по входу 11 значение у,,= 1, с приходом импульса на синхровход 1 в регистры 12 и 13 записываются значения х = х, у, = 1. Регистры 16 и 17 сдвига соединяются с соответствующими вторыми входами сумматоров 14 и 15 таким образом, что на входы поступают значения х и у со сдвигом на один разряд вправо, кроме того, на первый вход сумматоров 14 и 15 поступают значения х и у .

Полученные на выходах сумматоров

14 и 15 величины х, и у 1 поступают ! 1 в блок 2 коррекции, где осуществляется коррекция результата. Работа сумматоров 14 и 15 управляется по величинам и o <, которь!е эа счет сравнения значений х у. определяются в блоке

» !

18, с приходом импульса на синхровход

2 в блок 18 анализа разности записываются значения х . и у. а с прихо-! » дом импульса на синхровход 3 значения цифр а. и а . передаются для управ ! ления сумматоров 14 и 15. Во втором такте производится запись результатов вычислений иэ первого блока 2 коррекции во второй блок l, т.е. полученные значения х;, и у. после пер»Ф 1+» вого шага i-й итерации в результате коррекции иэ первого блока 2 записываются в регистры 12 и 13 второго блока 1 соответственно. Одновременно в регистры 12 и 13 первого блока поступакт коды второго операнда. В первом блоке 1 производится выполнение первой итерации над вторым операндом, аналогично, как в первом такте, выполняется первая итерация над первым операндом, а во втором блоке 1 выполняется вторая итерация над первым операндом. В третьем такте производится запись результатов вычислений из первого и второго блоков 2 коррекции во второй и тре ий блок 1 соответственно, и одновременно в регистры 12 и 13 первого блока

1 вычисления итерации поступают коды третьего операнда. В первом блоке 1 выполняется первая итерация над треть1545218 6 им операндам, ва втором — вторая итерация над вторым операндом, в третьем — третья итерация над первым операндом. В дальнейшем результаты из предыдущих блоков поступают в последующие блоки, а в первый блок поступают два операнда и т.д.

Рассматривают работу блока 2 коррекции.

Значения х. и у на выходах сум1 т

1 маторав поступают соответственно в регистры 19 и 20. С приходом импульса на синхровход 4 в регистры 19 и 20 записываются значения х . и у., Ре1 гистры 23 и 24 сдвига осуществляют сдвиг значений х и у . на один раз-, ряд вправо, т.е. их умножение на 2 а результаты (сдвинутые значения х .2 и у .2 ) поступают на первые входы коммутаторов 26 и 27 .соответственна, На вторые входы коммутаторов 26 и 27 поступают сигналы логического нуля. С приходом импульса на синхровход 5 в блоке 25 анализа разности записываются значения х т т и у, а с приходом импульса на синт хровход 6 значения цифр G = О,1 передаются для управления коммутаторов 26 и 27. На первые входы вьтчитателей 21 и 22 поступают соответственно значения х,, у ., а на вторые

1 входы вычитателей 21 и 22 поступают соответственно значения C-,õ. 2

С. у 2 . В каждом блоке 2 коррекции вычисляется алгоритм {2). В каждом

i-м (i = 1,2,...,n) итерационном блоке I и блоке 2 коррекции сдвиг на один разряд вправо осуществляется путем жесткого соединения выходов разрядов регистров с входами разрядов регистра сдвига со сдвигом на данное число разрядов.

15

25

40

Устройство для извлечения квадратного корня и его обратной величины, состоящее иэ и блоков вычисления (где п — число разрядов аргумента) итерации, каждый из которых содержит первый и второй регистры, первый и второй сумматоры, первый и второй регистры сдвига, блок анализа. разности, причем входы разрешения записи первого и второго регистров соединены с первым синхравхадом устройства, в ин- формационные входы подключены соответственно к первому. и второму информула изобретения 45 формационным входам ус.трайства, т ьтхс— ды первого и втарагп регисгров сое-динены с первыми входами соответственна первого и второго сумматоров, с входами первого и второго регистров сдвига и с первым и вторым информационными выходами блока анализа разности соатВетственна, первый и второй управляющие входы которого подключены к второму и третьему синхравходам устройства соответственно, а первый и второй выходы соединены с вторым и третьим синхровходами устройства соответственна, а т л и ч аю щ е е с я тем, что, с целью повышения быстродействия, в нега дополнительно введены и блоков коррекции, каждый из которых содержит первый и второй регистры, первый и второй ре-! гистры сдвига, первый и второй коммутаторы, первый и второй вычитатели, блок анализа разности, ттричем выходы первого и второго сумматоров i-го (i = l. 1n) блока итерации соединены с информационными входами соответственна первого и второго регистров i-го блока коррекции, входы разрешения записи которых соединены с четвертым синхравхадом устройства, выход первого регистра i-го блока коррекции соединен с первым входом первого вычитателя, с информационным входом первого регистра сдвига и пер- . вым информационным входом блока анализа разности i-ro блока коррекции, выход второго регистра i-ro блока коррекции подключен к первому входу второго вычитателя, информационному входу второго регистра сдвига и второму информационному входу блока анализа разности i-го блока коррекции, выходы первого и второго регистров сдвига i-ro блока коррекции соединены с первыми входами соответственно первого и второго коммутаторов того же блока коррекции, вторые входы которых подключены к пятому синхровходу устройства, а выходы — к вторым входам соответственна первого и второго вычитателей i-ro блока коррекции, первый и второй управляющие входы блока анализа разности i-ro блока коррекции соединены соответственна с шестым и седьмым синхровходами устройства, а первый и второй выходы — с третьити входами первого и второго коммутаторов того же блока коррекции, выходы первого и второго

l 545218 я ккг У

Составитель И. Жуков

Редактор Г. Гербер Техред M.Ходанич

Корректор С,Черни

Заказ 491 Тираж 561 Подписное

БНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

1l303 5, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r.Óæãîpoä, ул. Гагарина, 10l вычитателей 1 — 0 блока коррекции соединены с информационными входами первого и второго регистров (i+I)-rn блока вычисления итерации, выходы первого и второго вычитателей и-г< блока коррекции являются соответственно первым и вторым информационны5 ми выходами устройства.