Преобразователь частоты в код

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной и измерительной технике и может быть использовано в составе управляющих и измерительных систем, обрабатывающих первичную частотную информацию. Цель изобретения - повышение точности. Указанная цель достигается за счет того, что в устройство, содержащее блок 4 вычислений и управления, триггер 1, регистр 5 и блок 9 памяти, введены триггеры 3 и 6, элементы И 2 и 7 и буферный элемент 8. Введение этих элементов и использование программного счетчика центрального процессора в качестве таймера для формирования кода периода позволило синхронизировать начало преобразования с началом периода входного сигнала, а также увеличить частоту "заполнения" измеряемого интервала, что повышает точность преобразования. 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (11) А1 (51)5 Н 03 И 1/60

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ.ГКНТ СССР (21) 4365545/24-24 (22} 18.01. 88 (46) 28. 02, 90. Вюл. Р 8 (71) Рязанский радиотехнический институт (72) В.Н.Локтюхин и А.Н,Терехин (53) 681.325(088.8) (56) Иелкунов Н.Н., Дианов A,П.

Универсальный одноплатный микроконтроллер. — Иикропроцессорные средства и системы, 1986, l:"--5, с. 65-69.

Лон похин В.Н. Функциональный преобразователь частоты в код на основе микропроцессора. — Известия вузов, Приборостроение, 1985, Р 4, с. 540543. (54) 11РВОВРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД (57) Изобретение относится к вычислительной и измерительной технике и

2 может быть использовано в составе управляющих и измерительных систем, обрабатывающих первичную частотную информацию. Цель изобретения — повышение точности. Указанная цель достигается за счет того, что в устройство, содержащее блок 4 вычислений и управления, триггер 1, регистр 5 и блок 9 памяти, введены триггеры 3 и 6, элементы И 2 и 7 и буферный элемент 8. Введение этих элементов н использование программного счетчика центрального процессора в качестве таймера для формирования кода периода позволило синхронизировать начало преобразования с началом периода входного сигнала, а также увеличить частоту "заполнения" измеряемого интервала, что повьппает точно с ть преоб разов ания. 3 ил.

1547065

И зобретение относится к вычислительной и измерительной технике и

I может быть использовано в составе управляющих и измерительных систем

5 обрабатывающих первичную частотную информацию.

Цель изобретения — повышение точности.

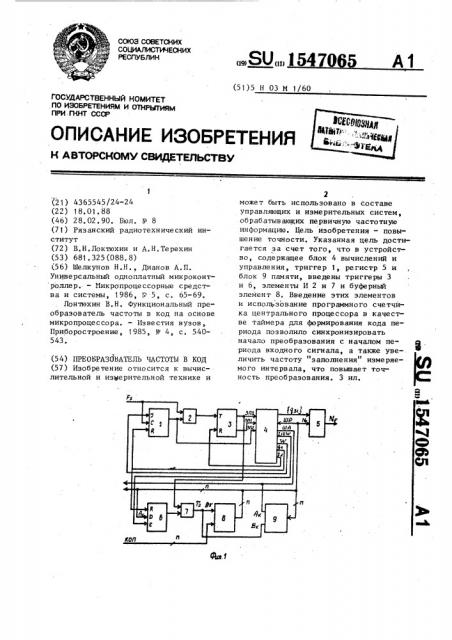

На фиг. 1 изображена функциональная схема предлагаемого преобразо,вателя; на фиг. 2 — схема блока вы числений.и управления; на фиг. 3— лок-схема алгоритма работы преобраователя.

Преобразователь содержит триггер

1, элемент И 2, триггер 3, блок 4

ычислений и управления, регистр 5, триггер 6, элемент И 7, буферный элемент 8 и блок 9 памяти. 20 (Блок 4 вычислений и управления содержит центральный процессор 10, так,товый генератор 11, блок 12 приори тетных прерываний, шинный формирователь 1 3, системный кон тролле р 1 4 и 25 элементы И 15 — 19.

Преобразователь работает следующим образом.

Преобразуемая частота F ïîñòóïàет на тактовый вход триггера 1 и на элемент И 2. K моменту начала преобразования блок 4 очищает необходимые регистры устанавливает в "0" триггеУ ,ры 1,3 и 6, вырабатывая сигналы q, 1 и я и (в ре ультате выполнения ко манды HLT останова) переходит в режим ожидания, о чем свидетельствует по,явление сигнала W, в качестве кото-!

; рого может быть использован сигнал

WATT центрального процессора.

Сигнал W ..разрешает прохождение импульсов преобразуемой частоты F„ в схему микропроцессорного преобразователя частоты в код (МПЧ1). По заднему фронту очередного импУльса F „, 45 триггер 1 устанавливае.тся в "1", разрешая прохождение следующего импуль са Р„ через элемент И 2 на вход триг.гера 3. По заднему фронту этого импульса триггер 3 устанавливается в

"1",в результате чего по линии ЗПО с прямого выхода триггера 3 в блок 4 и на элемент И 7 поступает сигнал запроса прерывания, подготавливая подключение буферного элемента 8 к шине данных преобразователя.

С приходом запроса по линии ЗПО в центральный процессор (ЦП) 10 бло.ка 4 поступает команда CALLTFN abrso ва подпрограммы преобразования периода Т„входного сигнала в код И т

Блок 4 выходит из режима ожидания и инициирует блок 12 на прием импульса Р„ и в результате выполнения команды ОИТ Ак (Ах=1, I/OW=1) устанавливает триггер 6 в " 1". В результате на выходе элемента И 7 формируется сигнал S, поступающий на входы разрешения буферного элемента 8 и блока 9 памяти.

Под воздействием сигнала S блок 9 памяти отключается от шины данных, а буферный элемент 8 подключается к ней, в результате чего на шине данных устанавливается код короткой операции NOP который на протяжении времени Ts действия сигнала Б постоянно считывается ЦП 10, в котором выполняе тся инкремент содержимого программного счетчика PC с частотой

Fo

F =-п где >, — тактовая частота для цП 10 (для 580 ик 80 Р =2 МГц;

n — число тактов выполнения команды NOP (n=4), Таким образом реализуется преобразование T И . С окончанием Т„ в МПЧК формируется запрос по линии

ЗП1, при этом буферный элемент 8 отключается от шины данных, а блок 9 памяти к ней подключается. Инкремент

PC прерывается и содержимое (PC)=Ns, пропорциональное длительности Т

Яэ перегружается в стек, а в PC загружается начальный адрес подпрограммы

1 вычисления N = — где N =И +дИ а

И s т т

4N — код коррекции задержки операций инкремента РС при преобразовании.

Вычисленный код N р по сигналам и q переписывается в регистр 5.

Таким образом, использование предлагаемого преобразователя позволяет при небольших аппаратурных затратах и использовании программного счетчика в качестве таймера повысить точность преобразования почти в четыре раза и для частоты входного сигнала

F 300 Гц обеспечить относительную погрешность d =-0, 037.

Формула изоб ре тен ия

Преобразователь частоты в код, содержащий блок вычислений и управления, входы-выходы которого соединены с входами регистра и информационными выходами блока памяти и являются шиной данных, адресные выходы блока вычислений и управления подключены к адресным входам блока памяти и являются шиной адреса, тактовый вход первого триггера является входной шиной, выходы регистра являются выходной шиной устройства, о тл и н а ю шийся тем, что, с целью повышения точности, в него введены второй и третий триггеры, первый и второй элементы И и буферный элемент, выходы которого подключены к шине данных, информационные входы. являются шиной задания кода, а вход разрешения объединен с входом разрешения блока памяти и подключен к выходу первого элемента И, первый и второй входы которого подключены к прямым выходам второго и третьего

47065 6 триг ге ров соотве тственно, входы уста-, новки в "0" которых подключены к первому и второму выходам блока вычислений и управления соответствен-.

5 но, пе рвый и в торой входы ко торо го ,. подключены к прямому и инверсному выходам тре тье го тригге ра, тре тий вход объединен с первым входом второго элемента И и подключен к выходу первого триггера, вход установки в

"0" которого объединен с входом установки в "0" второго триггера, I-вход подключен к третьему выходу блока вычислений и управления, четвертый и пятый выходы которого подключены к тактирующему входу второго триггера и входу загрузки регистра соответственно, информационный вход второго 0 триггера подключен к шине данных, второй вход второго элемента И является входной шиной, а выход соединен со сче тным входом тре тье ro тригге ра.

1547065

Составитель В. Гейнрихс

Техред Л. Сердокова Корректор В. Гирняк

Редактор А. Ревин

Подписное

Тирая 664

Заказ 85

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб. ° д. 4/5

Производственно-издательский комбинат "Патент", г.уагород, ул. Гагарина, 101