Способ аналого-цифрового преобразования и устройство для его осуществления

Иллюстрации

Показать всеРеферат

Изобретение относится к информационно-измерительной технике, может быть использовано для высокопроизводительного, прецизионного аналого-цифрового преобразования аналоговых сигналов и является усовершенствованием изобретения по а.с. N 1305848. Цель изобретения - повышение точности преобразования. Цель достигается дополнением устройства, реализующего алгоритм преобразования с выделением и уравновешиванием сигнала, пропорционального значению ошибки для каждого периода преобразования, узлом компенсации систематических составляющих сигнала ошибки. Функция узла - поддержание остаточного значения сигнала ошибки в диапазоне его точного измерения. Узел состоит из линии задержки, которая компенсирует динамическую составляющую в сигнале ошибки, последовательно соединенных блока компараторов, элементов И, реверсивного счетчика и цифроаналогового преобразователя, образующих блок компенсации статической составляющей сигнала ошибки. 2 з.п. ф-лы, 3 ил.

СООЗ СОВЕТСНИХ

ССЦИАЛИСТИЧЕСНИХ

РЕСПУбЛИК

<»>SU<„>>S ($f)$ H 03 М 1/10

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

Г (61) 1305848 (21) 4188223/24-24 (22) 29.01.87 (46) 07.03.90. Бюл. № 9 (72) С.Н.Логинов, Е.М.Прошин и А.С.Семенов (53) 681.325(088.8) (56) Балакай В.Г. и др. Интегральные схемы АЦП и ЦАП.- M.: Энергия, 1978, с.76-77, рис.1-24.

Авторское свидетельство СССР № 1305848, кл. Н 03 M 1/10, !985. (54) СПОСОБ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ (57) Изобретвние относится к информационно-измерительной технике, может быть использовано для высокопроизводительного, прецизионного аналогоцифрового преобразования аналоговых сигналов и является усовершенствоИзобретение относится к информащаонно-измерительной и вычислительноФ технике, может быть использовано для прецизионного преобразования аналоговых сигналов в код и является усовершенствованием изобретения по авт.св. ¹ 1305848.

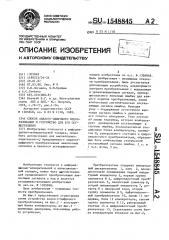

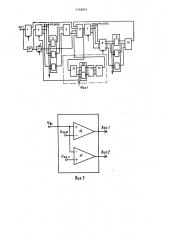

Цель изобретения — повьппение точности преобразования, На фиг.! представлена структурная схема устройства аналого-цифрового преобразования; на фиг.2 — конструкция блока компараторов; на фиг.3 временные диаграммы, поясняющие рабо-. ту устройства.

2 ванием изобретения по а.с. 1305848, Цель изобретения — повышение точности преобразования. Цель достигается дополнением устройства, реализующего алгоритм преобразования с выделением и уравновешиванием сигнала, пропорционального значению ошибки для каждого периода преобразования, узлом компенсации систематических составляющих сигнала ошибки. Функция узла — поддержание остаточного значения сигнала ошибки в диапазоне его точного измерения. Узел состоит из линии задержки, которая компенсирует динамическую составляющую в сигнале ошибки, последовательно соединенных блока компараторов, элементов И, реверсивного счетчика и цифроаналогового преобразователя, образующих блок компенсации статической составляющей сигнала ошибки. 2 с,.и

1 з п ° ф лыр 3 ила

Преобразователь содержит амплитудный дискретизатор 1, ключ 2, последовательно соединенные первый амплитудный анализатор 3, первую группу элементов И 4, цифроаналоговый преобразователь 5, аналоговый сумматор 6 ° второй амплитудный анализатор 7 ° регистр 8 с инверсией кода, вторую группу элементов И 9, цифроаналого-вый преобразователь 10 ° линию 11 задержки, блок 12 компараторов, третью группу элементов И 13, реверсивный счетчик 14 и цифроаналоговый преобразователь 15. Структурная схема бло- .ка компараторов показана на фиг.2, 1 548845 где компаратор 16 сравнивает выходное напряжение аналогового сумматора с верхней границей диапазона амплитудного анализатора 7, а компаратор

17 " с нижней границей диапазона, 5

Аналого-цифровой преобразователь работает следующим образом.

До момента стробирования амплитудного дискретизатора ключ 2 находится в открытом состоянии и пропускает задержанный на время 3 преобразуемый входной сигнал на вход аналогового сумматора (график 8), группы элементов И 4аи 9 закрыты (графики 6 и 7), в результате выходные напряжения цифроаналоговых преобразователей

5 и 10 близки к нулю (графики 10 и

13)) кодовая комбинация на вьйоде реверсивного счетчика 14 установлена предшествующими периодами преобразования, а цифроаналоговый преобразо ватель 15 в этом случае выдает неко-! торое компенсирующее напряжение (график 13). С приходом стробирующего им-25 пульса в момент времени t (график 1) производится выборка мгновенного значения преобразуемого сигнала, На вы— ,ходе аналогового сумматора (график

1 1) появляется напряжение ошибки, 30 величина которого зависит от выходного напряжения амплитудного дискретизатора, аддитивного смещения цифроаналоговых преобразователей 5 и 10, компенсирующего напряжения цифроаналогового преобразователя 15, преобразуемого входного сигнала, задержанного на время 3, собственно аддитив. ного смещения аналогового, кроме того при цифровом преобразовании на- 40 пряжения аналогового сумматора на результат кодирования влияет и собственное аддитивное смещение амплитудного анализатора 7. Иными словами в каждом периоде преобразования выделяется суммарная ошибка, которую привносят все узлы преобразователя, участвующие в иэмерении младших разрядов.. В момент времени производится стробирование амплитудных анализаторов 3 и 7, после чего ключ

2 закрывается.

По окончании кодирования старших разрядов входного сигнала и сигнала систематических ошибок преобразовате"

55 ля в момент времени стробируется регистр 8, запоминающий код ошибок, а также открываются группы элементов

И 4 и 9. На этом этапе производится формирование аналогового эквивалента старших разрядов входного напряжения и сигнала ошибок преобразователя, соответственно цифроаналоговыми преобразователями 5 и 10.Таким образом, аналоговое напряжение младших разрядов формируется из расностного напряжения между заполненным значением входного сигнала, аналогового эквивалента старших разрядов и аналогового эквивалента систематических ошибок. В момент времени t, повторно, в течение периода преобразования осуществляется стробирование амплитудного анализатора 7, который в этом случае кодирует уже младшие разряды преобразуемого напряжения. Сразу же после стробирования блока

7 ключ 2 открывается, а группы элементов И 4 и 9 закрываются, По окончании динамических процессов в цифроаналоговых преобразователях 5 и 10 и ключе 2 устройство готово к следующему периоду кодирования входной велич ины.

Рассмотрим теперь случай, когда сигнал ошибки к моменту его цифрового кодирования окажется за пределами диапазона амплитудного анализатора

7 (на фиг.3, период преобразования

Т1). В момент времени t>, когда производится стробирование амплитудных анализаторов, этот стробирующии импульс через открытый вентиль группы элементов И 13 поступает на один из выходов реверсивного счетчика 14.

Выбор входа счетчика зависит от того, какой граничный уровень диапазона амплитудного анализатора 7 был превышен. В данном случае превьппен верхний уровень преобразователя и поэтому срабатывает компаратор, открывающий вентиль, пропускающий стробирующий импульс на суммирующий вход счетчика. В результате эквивалентное коду счетчика 14 напряжение цифроаналогового преобразователя 15 увеличивается на один квант, что в свою очередь вызывает пропорциональное уменьшение выходного напряжения аналоговоro сумматора, Итеративный цикл компенсации ошибки продолжается до тех пор, пока сигнал ошибки не окажется в диапазоне кодирования амплитудного анализатора 7. В рассмотренном случае для компенсации было достаточно одного цикла, 5 15

Линия 11 задержки в устройстве необходима для компенсации в сигнале ошибки преобразователя, составленной от приращения входного преобраэуемого напряжения за время между моментами стробирования амплитудного дискретизатора и амплитудного анализатора

7. Степень соответствия задержки временному отрезку между стробирующими импульсами сказывается лишь на величине сигнала ошибки, которая измеряется амплитудным анализатором

7. На точность преобразования входного напряжения величина задержки влияния не оказывает. К факторам, ограничивающим точность преобразования, можно отнести частотно-фаэовые искажения, вносимые линией задержки при формировании сигнала ошибки.

Статическая точность цифроаналогового преобразователя 15 также не влияет на точность преобразования входной величины, так как блок компенсации работает в следящем режиме, а сам цифроаналоговый преобразователь

15 находится в цепи итеративной обратной связи. Дополнительная погрешность от этого преобразователя вызывается лишь его собственными шумами, которые складываются с аналоговым сигналом младших разрядов. Величина кванта преобразователя 15 должна иметь такое значение, чтобы вызывать смещение выходного напряжения сумматора приблизительно на половину шкалы амплитудного анализатора 7, В этом случае наиболее полно исгольэуется диапазон последнего при измерении оставшейся части сигнала ошибки. Если время одного цикла итерации не превышает времени кодирования входной величины, на компенсацию систематической составляющей сигнала ошибки затрачивается минимальное время, т.е. цикл итерации должен укладываться в период преобразования, Технико-экономический эффект возникает за счет снижения требований к точности цифроаналоговых преобразователей, аналогового сумматора и амплитудного дискретизатора, которые допускают значительные аддитивные смещения как во времени, так и от температуры, а также эа счет уменьшения затрат на настройку и эксплуатацию преобразователя благодаря компенсации систематической составляющей сигнала

48845 6 ошибки в процессе кодирования входной величины. формула изобретения

1 . Способ аналого-цифрового преобразования по авт.св. У 1305848> о т— л и ч а ю щ н и с я тем, что с целью повышения точности преобразования, в нем одновременно с преобразо10 ванием в код старших разрядов преобразуемого напряжения сравнивают напряжение разности между запомненным и текущим значениями преобразуемого напряжения с границами диапазона преобразования, формируют соответствующий код, преобразуют последний в компенсирующее напряжение, которое вычитают иэ напряжения разности между запомненным и текущим значениями преобразуемого напряжения в каждом периоде преобразования, а преобразуемое напряжение перед преобразованием в код старших разрядов задерживают. . 2.Устройство аналого-цифрового преобразования по авт.св. Р 305848 ° о т л и ч а ю щ е е с я тем, что в него введены блок компараторов, третья группа элементов И, реверсивный счетчик, третий цифроаналоговый преобразователь, линия задержки, включенная в разрыв связи входной шины с информационным входом первого амплитудного анализатора, вход блока компараторов соединен с выхо35 дом аналогового сумматора, а выходы подключены к соответствующим первым входам элементов И третьей группы, вторые входы которых являются первой управляющей шиной, а выходы соединены соответственно с входаМи суммирования и вычитания реверсивного счетчика, выход которого через третий цифроаналоговый преобразователь подключен к пятому входу аналогового

45 сумматора.

3.устройство по п,2, о т л и— ч а ю щ е е с я тем, что блок компараторов выполнен на двух компараторах, неинвертирующий вход первого

50 из которых и инвертирующий вход второго объединены и являются входом блока, инвертирующий вход первого компаратора и неинвертирующий вход второго являются соответственно шинами верхнего и нижнего граничных напряжений диапазона преобразования второго амплитудного анализатора а выходы компараторов являются выходами блока.

1548845

1548845

) х(1 -Г) Редактор Н,Лазаренко

Подписное

Тираж 666

Заказ 145

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101

СтроЮ 1 уа

С/Цюд 2 б(ЛИЧО

Стоод 3 дцпэ

СтроЮ 4

A(/77

Cmpol 5 рег 8 строуб 6 юлека. М

Страд 7 .мее и

V » 8 ключа ад 9

У®Г

Фщг е

ЩЮ5 gba ff сую атом

Ygp 8

Vtpa. Ац 12 а цгпю вых И

ЦДЛ15

Составитель В.Махнанов

Техред Л.Сердюкова Корректор М.Максимишинец