Устройство для сопряжения двух магистралей

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для сопряжения двух электронно-вычислительных машин в вычислительных комплексах. Целью изобретения является повышение скорости обмена информацией между магистралями за счет полного использования времени между обращениями к блоку памяти. Поставленная цель достигается тем, что в устройство для сопряжения двух магистралей, содержащее генератор импульсов, элемент НЕ, блок памяти и два блока связи, каждый из которых содержит регистр адреса, дешифратор зоны, группу элементов И, триггер, два элемента И, коммутатор магистрали, введены четыре элемента ИЛИ, два элемента задержки и два формирователя импульса по спаду сигнала. Введение новых элементов и связей обеспечивает сброс регистров адреса сразу после окончание обращения к блоку памяти, чем достигается полное использование времени между обращениями к блоку памяти, уменьшается время блокировки одного блока сопряжения другим и повышается быстродействия устройства. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 G 06 F 13/14

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЬ!ТИЯМ

ПРИ ГКНТ СССР (21) 4438664/24-24 (22) 08.06.88 (46) 15.03.90. Бюл. № 10 (72) В. П. Ремезов и Э. P . Лесневский (53) 681,3 (088 .8) (56) Авторское свидетельство СССР № 1241249, кл. G 06 F 13/14, 1984.

Авторское свидетельство СССР № 1283781, кл. С 06 F 13/14, 1987. (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ДВУХ

МАГИСТРАЛЕЙ (57) Изобретение относится к автоматике и вычислительной технике и мо" жет быть использовано для сопряжения двух электронно-вычислительных машин .в вычислительных комплексах. Целью изобретения является повышение скорости обмена информацией между магистралями за счет полного использования времени между обращениями к блоку паИзобретение относится к области автоматикии вычислительной техники и может быть использовано для сопряжения двух электронно-вычислительных машин (ЭВМ) в вычислительных комплексах.

Цель изобретения — повышение скорости обмена информацией между магистралями за счет полного использования времени между обращениями к бло ку памяти.

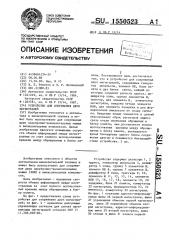

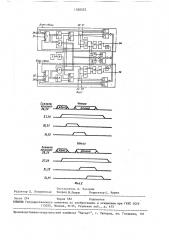

На фиг. 1 представлена схема устройства для сопряжения двух магистралей; на фиг. 2 — временные диаграммы управляющих сигналов для случая организации магистралей согласно ОСТ 11

11,305.903-80, „„SU„„1550523 А 1

2 мяти. Поставленная цель достигается тем, что в устройство для сопряжения двух магистралей, содержащее генератор импульсов, элемент НЕ, блок памяти и два блока связи, каждый из которых содержит регистр адреса, дешифратор зоны, группу элементов И, триггер, два элемента И, коммутатор магистрали, введены четыре элемента

ИЛИ, два элемента задержки и два формирователя импульсов по спаду сигнала. Введение новык элементов и связей обеспечивает сброс регистров адреса сразу после окончания обращения к блоку памяти, чем достигается полное использование времени между обращениями к блоку памяти, уменьшается время блокировки одного блока сопряжения другим и повышается быстродействия устройства. 2 ил.

Устройство содержит регистры 1, 2 адреса, генератор импульсов 3, дешифратор 4 зоны, группу 5 элементов И, элемент НЕ 6, группу 7 элементов И, дешифратор 8 зоны, триггеры 9, 10„ элементы И 11, 12, 13, 14, элементы

ИЛИ 15 !6, 17, 18. элементы 19, 20 задержки, блок 21 памяти, коммутатор

22 магистрали, формирователи 23, 24 импульса, коммутатор 25 магистрали

На фиг. 1 показаны адресно-информационные шины 26 первой магистрали, шина

27 управления обменом первой магистрали, шина 28 управления обменом второй магистрали, адресно-информационные шины 29 второй магистрали, шина

30 чтения и шина 31 записи первой<

5 15505 первый и второй блоки связи, каждый из которых содержит регистр адреса, дешифратор зоны, группу элементов И, триггер, первый и второй элементы И, коммутатор магистрали, причем в кажУ дом блохе связи первая группа информационных входов-выходов коммутатора магистрали является группой входоввыходов устройства для подключения к адресно-информационным шинам соответствующей магистрали и подключена к группе информационных входов регистра адреса, информационные выходы которого соединены с первыми входами 15 элементов И группы и с входами дешифратора зоны, выход которого соединен с информационным входом триггера, прямой выход которого соединен с вторыми входами элементов И группы, с 20 первыми входами первого и второго элементов И, со стробирующим входом коммутатора магистрали, первый вход управления коммутатора магистрали является входом устройства для под- 25 ключения к шине записи соответствующей магистрали и соединен с вторым входом первого элемента И, второй вход управления коммутатора магистрали является входом устройства для 3р подключения к шине чтения соответствующей магистрали и соединен с вторым входом второго элемента И, вторые группы информационных входов-выходов коммутаторов магистрали первого и

35 второго блоков связи соединены с информационными входами-выходами блока памяти, адресные входы которого соединены с выходами элементов И групп первого и второго блоков связи, выход 4р генератора импульсов соединен с тактовым входом триггера первого блока ,связи и с входом элемента НЕ, выход

23 которого соединен с тактовым входом триггера второго блока связи, выход триггера. первого блока связи соединен с входом сброса триггера второго блока связи, выход триггера второго блока связи соединен с входом сброса триггера первого блока связи, синхровходы регистров адреса первого и вто-, рого блоков связи подсоединены к входам устройства для подключения к шинам синхронизации первой и второй магистралей соответственно, о т л ичающее с я тем, что, с целью повышения скорости обмена информацией между магистралями, в него введены первый и второй элементы ИЛИ и в каждый из блоков связи — формирователь импульса, элемент задержки и элемент

НЕ, причем в каждом блоке связи первый и второй входы элемента ИЛИ соединены с выходами первого и второго эле ментов И соответственно, выход элемента ИЛИ соединен с входом элемента задержки, выход которого соединен с входом формирователя импульса, выход которого соединен с входом сброса регистра адреса, выходы элементов задержки первого и второго блоков связи подключены соответственно к выходам устройства для подключения к шинам ответа первой и второй магистралей, выходы первых элементов И первого и второго „блоков связи соединены соответственно с первым и вторым входами первого элемента ИЛИ, выходы вторых элементов И первого и второго блоков связи соединены соответственно с первым и вторым входами второго элемента ИЛИ, выходы первого и второго элементов ИЛИ соединены соответственно с входами разрешения записи и чтения блока памяти.

1550523

Бланж еАтзи

Сааиалы /ление наааиах:,4е ес а ны

N,29

Ю,32

Зались

Сигналы иа ишиах ес Данные

26,0

Составитель А. Засорин

Редактор Л. Пчолинская Техред И.яндык Корректор С. Черни

Заказ 274 Тираж 562 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r Ужгород, ул. Гагарина, 161