Устройство для сопряжения канала связи с эвм

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в телеметрических системах, предназначенных для сбора, хранения и обработки принимаемой информации. Целью изобретения является повышение быстродействия. Устройство содержит блок управления, два блока памяти, селектор, блок синхронизации, счетчик адреса, регистр, три коммутатора, три элемента И, элемент ИЛИ. 1 з.п. ф-лы, 3 ил.

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (5))5 G 06 F 13 32

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ (21) 4427367/24-24 (22) 17.05.88 (46) 15. 03. 90. Бюл. М 10 (72) В. А. Гриневич „Д. Е. Ефимов, В. K. Иванов, С. В. Исаев, Ю. M. Никитин и P. M. Николайчук (53) 681 .325 (088.8) (56) Авторское свидетельство СССР

II- 1269144, кл. G 06 F 13/00, 1985.

Авторское свидетельство СССР

1251091, кл. С 06 F 13/00, 1985.

Изобретение относится к вычислительной технике и может быть использовано в телеметрических системах, предназначенных для сбора, хранения и обработки принимаемой информации.

Цель изобретения — повышение быстродействия.

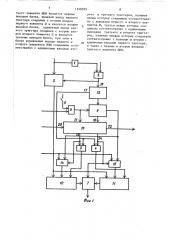

На фиг. 1 представлена схема устройства; на фиг. 2 — схема блока синхронизации; на фиг. 3 — схема блока управления.

Устройство содержит селектор 1, элементы И 2, 3, 4, регистр 5, счетчик 6 адреса, коммутатор 7, элемент

ИЛИ 8, установочный вход. 9, блоки 10, 11 памяти, блок 12 синхронизации, блок 13 управления,.коммутатор 14, коммутатор 15, вход запуска 16 блока

12, второй выход 17 блока 12, первый выход 18 блока 12, вход 19 блока 13, вход 20 блока 13, вход 21 начальной установки блока 13, первый 22 выход

„„ЯУ„, 1556525 А 1

2 (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ KAIAJIA

СВЯЗИ С ЭВИ (57) Изобретение относится к вычислительной технике и может быть использовано в телеметрических системах, предназначенных для сбора, хранения и обработки принимаемой информации.

Целью изобретения является повышение быстродействия. Устройство содержит блок управления, два блока памяти, селектор, блок синхронизации, счетчик адреса, регистр, три коммутатора, три триггера И, элемент ИЛИ. 1 з.п. флы 3 ил блока !3, третий выход 23 блока 13 и второй выход 24 блока 13.

Блок 12 синхронизации содержит генератор 25 импульсов, элемент И 26, счетчик 27, дешифратор 28.

Блок 13 управления содержит элементы ИЛИ 29-31, элементы И 32, 33, триггеры 34-36.

Устройство работает следуюпдм образом.

При подаче сигнала по входу 9 или поступлении на первый вход элемента

ИЛИ 8 устройство устанавливается в начальное состояние, при котором на; выходе счетчика 6 адреса устанавливается нулевой адрес, на третьем 23 и втором 24 выходах блока управления

13 устанавливается соответственно высокий и низкий уровни. При этом элемент И 3 разрешает прохождение импульса записи в блок 10 памяти, коммутатор 14 соединяет адресный вход

1550525; блока 10 памяти с выходом счетчика 6 адреса, элемент И 4 запрещает прохождение импульса записи в блок 11, адресный вход которого с помощью комму5 татора 15 соединен с адресным выходом приемника информации, а коммутатор 7 соединяет выход блока 11 памяти с информационным входом приемника информации. IÎ

При появлении порции информации, которую селектор 1 определяет как начальную, на его выходе появляется сигнал разрешения прохождения синхро- 15 сигнала через элемент 2 И. Причем сигнал разрешения на выходе селектора

1 появляется в определенный промежуток времени и стробирует сигнал синхронизации. Синхроимпульс на выходе элемента И 2 зафиксирует данные в регистре 5 и запустит блок.12 синхронизации. Запуск блока 12 синхронизации состоит в том, что импульс с входа запуска 16 поступает на вход уста- 25 новки счетчика 27, на выходе которого появляются сигналы низкого уровня, что в свою очередь приводит к появлению сигнала высокого уровня на третьем выходе дешифратора 28. Этот сигнал разрешает прохождение сигналов с генератора 25 импульсов через элемент

И 26 на тактовый вход счетчика 27. В результате чего состояния на выходе счетчика 27 будут изменяться, и на первом и втором выходах дешифратора

28 последовательно во времени появляется по импульсу. Причем частота следования сигналов с генератора 25 импульсов выбрана такой, чтобы были

40 соблюдены временные соотношения установления данных на выходе регистра 5, записи в блоки 10 или 11 памяти и перевода .адреса в счетчике 6 адреса.

Импульс с первого выхода дешифратора

28 блока 12 синхронизации через элемент И 3 поступает на вход записи блока 10 памяти и записывает данные, установленные на выходе регистра 5 по адресу, установленному счетчиком

6 адреса и подаваемому через коммута тор 14 на адресно вход блока 10 памяти. Импульс со второго выхода дешифратора 28 блока 12 синхронизации подается на счетный вход счетчика 5 адреса и увеличивает его содержимое на единицу, что соответствует адресу следующей ячейки. При появлении следующего синхроиж ульса описанный процесс повторяется — данные записываются в следующую. ячейку блока 10 памяти. При заполнении блока 10 памяти на выходе переполнения счетчика 6 адреса появляется импульс, который поступает в блок 13 управления, где он поступает на первые входы элементов

И 32, 33 но на третьем входе элемента И 32 установлен низкий уровень, поступающий с нулевого выхода триггера 36, поэтому импульс со входа 19 поступает на нулевой вход триггера

35, при этом íà его нулевом выходе," устанавливается высокий уровень, который поступит на нулевой вход триггера 36 и на первый вход элемента

ИЛИ 31, при этом триггер 36 изменяет свое состояние, на третьем выходе 23 появляется низкий уровень, а на втором выходе 24 — высокий уровень, на выходе элемента ИЛИ 31 появляется высокий уровень. После появления этих сигналов элемент И 3 запрещает прохождение импульсов записи на блок 10 памяти, адресный вход которого через коммутатор 14 соединяется с адресным выходом приемника информации, а выход .блока 10 памяти соединяется через коммутатор 7 с информационным входом приемника информации, элемент И 4 разрешает прохождение импульсов записи на блок 11 памяти, адресный вход которого соединен через коммутатор 15 с выходом счетчика 6 адреса. Кроме того на выходе 22 блока 13 появляется сигнал, свидетельствующий о том, что блок 1 0 памяти заполнен. По этому сигналу приемник информации может приступить к считыванию информации блока

10 памяти. При этом приемник информации устанавливает .адрес ячейки блока памяти иэ которого необходимо считать информацию, а информацию считывает с выхода коммутатора 7. По окончании считывания информации приемник информации должен подать импульс на вход 20 блока 13. Этот импульс поступает на вторые входы элемента ИЛИ 29 и 30, с выходов этих элементов импульсы поступают на единичные входы триггеров 34 и 35 при этом на их единичных выходах устанавливается высокий уровень, который поступает на входы элементов И 33 и 32, на нулевом выходе триггера 35 устанавливается низкий уровень, что приводит к снятию сигнала на выходе 22 блока 13.

5 155052

В это самое время со входа устройства записываются в блок 11 памяти аналогично процессу записи в блок 10 памяти. При переполнении счетчика 6 адреса на его выходе переполнения

5 появляется импульс, который подается в блок 13 управления и переключает триггер 36, если до этого был подан сигнал по входу 20, который разрешит прохождение этого импульса переполнения через элемент И 32. Если же сигнал по входу 20 не был подан, то триггер 36 не переключит, т.е. последующая информация будет вновь записа- 15 на в блок ll памяти. Поэтому для исключения потерь информации при выводе из устройства, необходимо чтобы цикл чтения бып короче цикла ввода информации в устройство. 20

Для повторной установки устройст- . ва в начальное положение необходимо или воспользоваться входом установки

9, или подать импульс сброса с установочного выхода источника информациие

Формула изобретения

1. Устройство для сопряжения канала связи с 3ВМ, содержащее блок управления, блок синхронизации, регистр, счетчик адреса, селектор, два блока памяти, первый коммутатор, три элемента И, элемент ИЛИ, причем информа35 ционный вход регистра соединен с информационным входом селектора и является входом устройства для подключения к информационному выходу канала связи, первые входы первого элемента 40

И и элемента ИЛИ являются входами уст» ройства дЛя подключения соответственно к синхровходу и установочному выходу канала связи, первый вход логического условия и первый выход бло- 45 ка управления являются входом и выходом устройства для подключения соответственно к выходу сброса прерывания и входу запроса прерывания ЭВМ, информационный выход первого коммутато- 0 ра является выходом устройства для . подключения к информационному входу

ЭВМ,.второй вход элемента ИЛИ является установочным входом устройства, О т л и ч а ю щ e e с я тем что 55 с целью повышения быстродействия, в него введены второй и третий коммутаторы, причем первый информационный вход второго коммутатора соединен с

5 6 первым информационным входом третьего ком;мутатора и является входом устройства для. подключения к адресному вьгходу ЭВМ, при этом вьг од селектора соединен с вторым входом первого элемента И, выход которого соединен с входом записи регистра и с входом запуска блока синхронизации, первый синхровыход которого соединен со счет

HbM входом счетчика адреса, установо-.ный вход которого соединен с выходам элемента ИЛИ и с установочным входом блока управления, второй вход логического условия которого соединен с выходом переполнения счетчика адреса, выход которого соединен с вторыми информационными входами второго и третьего коммутаторов, информационные выходы которых соединены соответственно с адресными входами первого ч второго блоков памяти, информационные выходы которых соединены соответственно с первым и вторым информационными входами первого коммутатора, управляющий вход которого соединен с управляющим входом третьего коммутатора, с вторым выходом блока управления и с первым входом второго элемента И, выход которого соединен с входом записи второго блока памяти, информационный вход которого соединен .с информациочным выходом регистра и с инфсрмационным входом первого блока памяти, вход записи которого соединен с выходом третьего элемента И, первый вход которого соединен с управляющим входом второго коммутатора и с третьим выходом блока управления, второй синхровыход блока. синхронизации соединен с вторыми входами второго и третьего элементов И.

2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что блок упра". вления содержит три триггера, три элемента ИЛИ, два элемента И, причем первый вход первого элемента ИЛИ соединен е первым входом второго элемента ИЛИ, с первым единичным входом первого триггера и является установочным входом блока, второй вход,первого элемента ИЛИ соединен с вторым входом второго элемента ЦЗИ и являет»ся первым входом логического условия блока, первый вход первого элемента

И соединен с первым входом второго элемента И и является вторым входом логического условия блока, выход тре1550525 тьебо элемента ИЛИ является первым выходом блока. нулевой выход первого триггера соединен с вторым входом первого элемента И и является вторым

l выходом блока, единичный выход первого триггера соединен с вторым входом второго элемента И и является третьим выходом блока, при этом в блоке управления выходы первого и 0 второго элементов ИЛИ соединены соответственно с единичными входами второго и третьего триггеров, нулевые входы которых соединены соответственно с выходами первого и второго элементов И, третьи входы которых соединены соответственно с единичными выходами третьего и второго триггеров, нулевые выходы которых соединены соответственно с нулевым и вторым; единичным входами первого триггера, а также с первым и вторым входами третьего элемента ИЛИ.

1550525

Фиг. 2

Составитель С, Пестмал

Техред M .Дидык Корректор В. Кабаций

Репактор Л. Пчолинская

Заказ 274 Тираж 566 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при 1 КНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101