Устройство для псевдообращения матриц

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для использования в системах обработки информации, поступающей от сложных динамических объектов. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что для матриц специального вида псевдообратная матрица может быть найдена как произведениее транспонированной матрицы на постоянный множитель. Особенностью работы устройства является новый алгоритм псевдообращения матриц специального вида. 1 ил.

союз соВетских социА лист ичесних

РеспуБлик (Я)5 С 06 Е 15 36

ГОсудАРстВенный комит=т по изоБРетениям и откР1 1тиям пРи гкнт сссР с

ОПИСАНИЕ ИЗОБРЕТЕНИЯ и AВТОРСНОМУ СВИДЕТЕЛЬСТВУ! а а ... а

L 11

Ъ h+1 а а а . ° . а

N М+1 уй+ 2 ° rn+ и а а а ... а

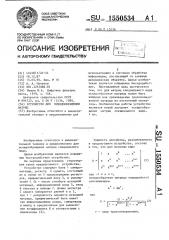

А =КА где (2)

Й(6 !) q Г g(qi)1

1-а 1 — а т — знак транспочирования. (21) 4345871/24-24 (22) 18.12.87 (46) 15.03.90. Бюл. № 10 (72) А. А. Матвеев (53) 681 .325(088 .8) (56) Мизин И.А. Цифровые фильтры.

Связь, 1979, с. 146.

Авторское свидетельство СССР № 894722, кл. G 06 F 15/36, 1980. (54) УСТРОЙСТВО ДЛЯ ПСЕВДООБРАЩЕНИЯ

МАТРИЦ (57) Изобретение относится к вычислительной технике и предназначено для

Изобретение относится к вычислительной технике и предназначено для псевдообращения матриц специального вида.

Целью изобретения является повышение быстродействия устройства.

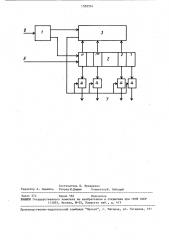

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит блок 1 синхронизации„ регистр 2 сдвига, состоящий из и групп по 1 одноразрядных регистров, арифметический блок 3, и умножителей 4 (n — число столбцов исходной матрицы), информационный вход 5, вход

6 запуска и выходы 7. Длина регистра

2 сдвига выбирается равной и х 1, где 1 — разрядность элемента исходной матрицы. Арифметический блок имеет три информационных входа, синхровход и выход и предназначен для вычисления коэффициента К в соответствии с выражением (2).

ÄÄSUÄÄ 1550534 А t

2 использования в системах обработки информации, поступающей от сложных динамических объектов. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что для матриц специального вида псевцообратная матрица может быть найдена как произведение транспонированной матрицы на постоянный множитель ° Особенностью работы устройства является новый алгоритм псевдообращения матриц специального вида.

1 ил.

Сущность алгоритма, реализованного в предлагаемом устройстве, состоит в том, что для матрицы вида где -1 (а 1, псевдообратная матрица определяется соотношением

1550534 Устройство работает следующим об разом.

На вход 6 запуска подается сигнал запуска„ и с первого выхода блока 1 синхронизации на сихровход регистра 2 сдвига поступает последовательность из и импульсов. Одновременно на информационный вход устройства подается последовательность элементов перВой строки исходной матрицы, которая записывается в регистр 2 сдвига. Ког а вся строка запишется в регистр 2 сдвига, на первый, второй и третий

Ннформационные входы арифметического блока 3 поступают соответственно второй, m-й и и-й элементы первой строки исходной матрицы, т.е. а, а и ь а . По импульсу с второго выхода блоka 1 синхронизации в арифметическом блоке 3 в соответствии с выражением (2) вычисляется коэффициент К, который с выхода арифметического блока 3

Подается на вторые входы умножителей

4, на первые входы которых поступают элементы первой строки исходной матрицы. При этом с выходов умножителей ,На выходы устройства поступает произ9едение первой строки на коэффициент

К, которое, в соответствии с (1)

Представляет собой первый столбец. матрицы-результата.

Остальные столбцы матрицы-результата вычисляются в соответствии с (1) аналогично первому за исключением того, что на синхровход арифметического блока не подается синхроимпульс, а число К подается на вторые входы умножителей вплоть до вычисле- ния последнего столбца матрицы-результата.

Формула изобретения

Устройство для псевдообращения матриц, содержащее регистр сдвига, .состоящий из и групп по 1 одноразрядных регистров с параллельными вы-. ходами в каждой (n — число столбцов исходной матрицы; 1 — разрядность элемента исходной матрицы), арифметический блок, и умножителей и блок сихронизации, первый и второй выходы которого соединены с синхровходами соответственно регистра сдвига и

20 арифметического блока, параллельные выходы х-й группы регистров сдвига соединены с первьм входом i-го умножителя, выход которого является х-м выходом устройства (i = 1, п), вход

25 запуска которого подключен к входу . запуска блока синхронизации, о т— л и ч а þ ù е е с я тем, что, с целью повышения быстродействия, информационный вход устройства подключен к последовательному входу регистра сдвига, параллельные выходы второй

m-й и и-й групп регистров подключены соответственно к первому, второму и третьему информационным входам ариф35 метического блока, выход которого подключен к вторым входам всех умножителей (m — число строк исходной матрицы).

1 550534

Составитель К. Кухаренко

Редактор А. Лежнина Техред M.Äèäûê КорректорВ. Кабаций

Заказ 274 Тираж 562 Подписное

ВНИИПИ Государственного комитета о изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101