Запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных системах. Целью изобретения является расширение области применения устройства за счет возможности косвенной адресации. Запоминающее устройство содержит формирователь сигналов записи 1, накопитель 3, дешифратор 4, формирователь адресных сигналов 5. Введение формирователя режима адресации 6 позволяет реализовать косвенный способ адресации. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) А1 (5g)g G 11 C 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОбРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГННТ СССР (21) 4357473/24-24 (22) 04.01.88 (46) 15,03.90. Бюл, ¹ 10 (71) Московский институт электронной техники (72) В.В,Баринов, М.А.Губаревич и А.Ф.Макаренко (53) 681,327.6(088,8) (56) Соучек Б, Микропроцессоры и микроЗВМ. Советское радио, 1979, с. 136.

Алексеенко А. Г., Шагурин. И-.И, Микросхемотехника. Учебное пособие для вузов/под ред. И.П.Степаненко.

M. Радио и связь, 1082-416с, с.247, рис. 7.1.

2 (54) ЗАПОМИНА10ЩЕЕ УСТРОЙСТВО (57) Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных системах. Целью изобретения является расширение области применения устройства за счет возможности косвенной адресации. Запоминающее устройство содержит формирователь сигналов sanucu 1, накопитель 3, дешифратор 4, формирователь адресных сигналов 5.

Введение формирователя режима адресации 6 позволяет реализовать косвенный способ адресации, 2 ил.

1550582

ЗУ работает следующим образом.

В режиме записи информации сигна- 30 лы кода адреса- А,,...,Aó поступают .с входов 7 в формирователь 6. Управляющий сигнал, поступающий на вход 9

1 формирователя режима адресации, разРешает прохождение кода адреса с внешних входов 7 на формирователь 5 адресных сигналов. Формирователь 5 необходимым образом преобразует сигналы кода адреса (согласует внешние и внутренние логические уровни, уси- 40 ливает сигналы, формирует дополнительный код адреса А,,...,А ) и передает в дешифратор 4.:последний в соответствии с поступившим кодом адреса выбирает в матри:ge накопителя 45

3 элементы памяти (ЭП), в которые в дальнейшем будет осуществляться запись информации (или считывание в режиме считывания информации)..

Формирователь 1 сигналов записи преобразует информационные сигналы

D» ..., П„„ поступающие на него с входа 2 ЗУ (согласует внешние и внутренние логические уровня, усиливает их, формирует дополнительный код

D» ...,Dr@ и обеспечивает запись входной информации в соответствии с кодом адреса в выбранные ЭП накопителя 3 ..

Запоминающее устройс гво (ЗУ) от носится к цифровой вычислительной технике и может быть использовано в вычислительных системах.

Целью изобретения является расширение области применения устройства за счет возможности косвенной адресации.

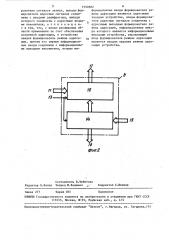

На фиг. 1 изображена схема запоминающего устройства; на фиг. 2— структурная схема формирователя ре жима адресации.

ЗУ (фиг. 1) содержит формирова тель 1 сигналов записи, информаци онные входы 2, накопитель 3, дешиф ратор 4, формирователь 5 адресных

:сигналов, формирователь 6 режима

;адресации, адресные входы 7, инфор-! мационные выходы 8, вход 9 вида ре, жима адресации.

Формирователь режима адресации (фиг. 2) содержит коммутатор 10, ,вторые информационные входы 11, ад ресный выход 12, управляющий вход

13, мультиплексор 14, первые инфор,мационные входы 15, информационные, выходы 16.

В режиме считывания информации при прямом способе адресации вь1борка

ЭП в накопителе 3 производится точно так же, как и в режиме записи: сигналы кода адреса с входов 7 ЗУ через формирователь 6 поступают на формирователь 5 и далее через дешифратор 4 на накопитель 3. Считанная из накопителя 3 информация под воздействием сигнала управления на входе 9 поступает через формирователь

6 на выход 8 ЗУ.

При косвенном способе адресации для выполнения следующей операции служит выходная информация предыдущей операции. Для этого управляющий сигнал на входе 9 запрещает прохождение кода адреса с входов 7 на формирователь 5 и разрешает прохождение выходной информации, используемой в качестве кода адреса, из накопителя 3 на формирователь 5 адресных сигналов.

Возможность работы ЗУ с прямой и косвенной адресацией обеспечивает формирователь 6 режима адресации (фиг. 2). Мультиплексор 14 в зависимости от управляющего сигнала на входе 13 передает информацию с входов 15 либо на информационные выходы

16 (при прямом способе адресации), либо на вторую группу входов коммутатора 10 (при косвенном способе адресации). Коммутатор 10, в свою очередь, под действием того же управляющего сигнала на входе 13 подключает к адресным выходам 12 либо входы 11 (при прямом способе адресации), либо вторую группу выходов мультиплексора 14 (при косвенном способе адресации).

Таким образом, введение в ЗУ формирователя режима адресации позволяет реализовать косвенный способ адреса- . ции, что значительно расширяет область применения ЗУ, особенно при использовании в вычислительных системах совместно с микропроцессорами.

Формула изобретения

Запоминающее устройство, содержащее формирователь сигналов записи, входы которого являются информационными входами устройства, формирователь адресных сигналов, дешифратор и накопитель, информационные входы которого соединены с выходами формиЮ фиг2

Составитель В.Чеботова

Редактор Е.Копча Техред М.Ходанич, Корректор С.Шекмар

Заказ 277 Тираж 485 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r.Óêãoðoä, ул. Гагарина, 101

5 15 рователя сигналов записи, выходы формирователя адресных сигналов соединены с входами дешифратора, выходы которого соединены с адресными входами накопителя, о тлича юще ес я тем, что, с целью расширения области применения за счет обеспечения косвенной адресации, в устройство введен формирователь режима адресации, причем его первые информационные входы соединены с информационными выходами накопителя, вторые ин50582 6 формационные входы формирователя режима адресации являются адресными входами устройства, входы формирователя адресных сигналов соединены с

5 адресными выходами формирователя режима адресации, информационные выходы которого являются информационными выходами устройства, управляющий вход формирователя режима адресации является входом задания режима адресации устройства.