Мультиплексор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано в качестве коммутатора или универсального логического модуля при построении устройств цифровой обработки информации. Цель изобретения - упрощение конструкции мультиплексора. Поставленная цель достигается тем, что мультиплексор содержит четыре элемента НЕ 1 - 4, двадцать один элемент ИЛИ 5 - 25, четыре элемента И 26 - 29, четыре адресных входа 30 - 33, шестнадцать информационных входов 34 - 49 и выход 50. Сложность мультиплексора по числу входов логических элементов равна 72, а быстродействие, определяемое глубиной схемы, равно 5&Tgr;, где &Tgr; - задержка на вентиль. Мультиплексор работает в двух режимах. В режиме коммутатора на его адресные входы подаются переменные X<SB POS="POST">1</SB>, X<SB POS="POST">2</SB>, X<SB POS="POST">3</SB>, X<SB POS="POST">4</SB>, составляющие двоичный номер информационного входа, который подключается к выходу. В режиме универсального логического модуля на информационные входы подается вектор значений (таблица истинности) реализуемой логической функции F, переменные которой подаются на адресные входы. 1 ил., 1 табл.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

091 (И) (51)5 G 06 F 7 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСВ"ВУ (54) МУЛЬТИПЛЕКСОР

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ AEHT СССР (21) 4454103/24-24 (22) 04,07.88 (46) 23 ° 03 ° 90 ° Бюл. V 11 (72) Л.Б.Авгуль и В.П.Супрун (53) 681.3(088.8) (56) Авторское свидетельство СССР

h" 1487023 кл. G 06 F 7/00, 1987.

Интегральные микросхемы: Справочник. / Под ред. Б.В.Тарабрина. - И.:

Радио и связь, 1984, с. 68. (57) Изобретение относится к вычис2 лительной технике,и микроэлектронике и может быть использовано в качестве коммутатора или универсального логическоro модуля при построении устройств цифровой обработки информации .

Цель изобретения — упроц ение конструкции мультиплексора. Поставленная цель достигается тем, что мультиплексор содержит четыре элемента HE 1-4, двадцать один элемент ИЛИ 5-25, четыре элемента И 26-29, четыре адресных входа 30-33, шестнадцать информационных входов 34-49 и выход 50.

Сложность мультиплексора по числу

1552170

20 входов логических элементов равна

72, а быстродействие, определяемое глубиной схемы, равно 5, где ь, задержка на вентиль. Мультиплексор работает в двух режимах. В режиме коммутатора на его адресные входы подаются переменные х,, х, X>„ x<„ составляюшие двоичный номер информа1

Изобретение относится к вычисли-! 3 тельнои технике и микроэлектронике и может быть использовано в качест ; ве коммутатора или универсального ( логического модуля при построении устройств цифровой обработки инфор,,мации.

Цель изобретения - упровение кон струкции мультиплексора.

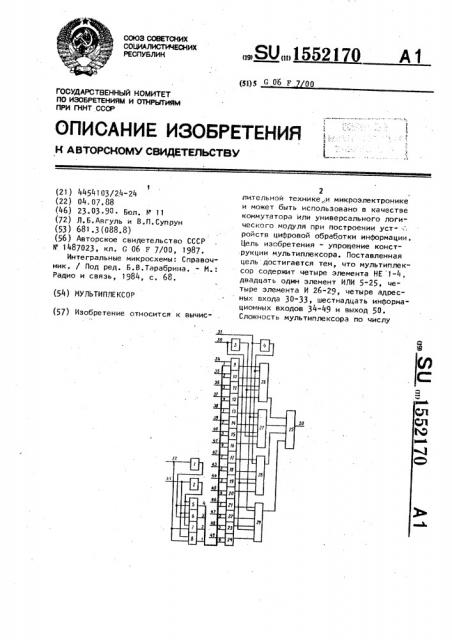

На чертеже представлена схема мультиплексора.

Мультиплексор содержит четыре, элемента HE 1-4, двадцать один эле,мент ИЛИ 5-25, четыре элемента И 26-. . 29, четыре адресных входа 30-33, шестнадцать информационных входов 34-49., выход 50.

Мультиплексор работает в двух ре,жимах.

В режиме коммутатора на адре сные . входы 30-33 подаются двоичные переменные х, - х4 соответственно, сос ; тавляювие двоичный номер N = 2 X + у С)

+ 2 х + 2 х > + ? х4 инфоРмационного входа, который подключается к выходу 50. Работа мультиплексора в этом режиме поясняется таблицей„ в которой символом " н обозначено безразличное состояние.

В режиме универсального логического модуля на информационные входы

34-49 поступает вектор значений (таб45 лица истинности) Y = (у„, у„, у, ) реализуемой логической функции четырех переменных F =- F.(õ,, х, х3, х ), двоичные аргументы которой х, х4 поступают на адресные входы 3033 соответственно. На выходе 50 сигнал Z совпадает со значением функции

F на данном наборе аргументов х, -х °

Пример. Определим сигналы на информационных входах мультиплексора при реализации логической функции

F(x< ух рx) уxy) = х x) v x x x ционного входа, который подключается к выходу. В режиме универсального логического модуля на информационные входы подается вектор значений (таблица интенсивности) реализуемой логической функции F, переменные которой подаются на адресные входы. 1 ил., 1 табл.

Очевидно, что Y = (0,0,1,1,0,1,1,1, 0,0,0,0.0,0 1,0,0). Тогда сигнал логического нуля должен быть подан на первый 34 второй 5, пятый 38, девятый 4?, десятый 43, одиннадцатый

44, двенадцатый 45, тринадцатый 46, пятнадцатый 48 и шестнадцатый 49 ин" формационные входы мультиплексора, а сигнал логической единицы - на третий 36, четвертый 37. вестой 39., седьмой 40, восьмой 41 и четырнадцатый 47 информационные входы мультиплексора.

Формула изобретения

Муль тип ле ксор, содержащий четыре элемента НЕ, четыре элемента И и элемент ИЛИ первой группы, выход которого соединен с выходом мультиплексора, i.-й вход элемента ИЛИ первой группы (i = 1,4) соединен с выходом

i-ro элемента И, i-й адресный вход мультиплексора соединен с входом i-ro элемента НЕ, первый вход первого элемента И соединен с первым входом второго элемента И и выходом первого элемента НЕ, вход которого соединен с первыми входами третьего и четвертого элементов И, второй вход четвертого элемента И соединен с вторым входом второго элемента И и входом второго элемента НЕ„ выход которого соединен с вторым входом первого элемента И и вторым входом третьего элемента И, о т л и ч а ю ц и и с я

1 тем, что, с целью упроц ения, он содержит вторую и третью группы элементов ИЛИ, причем первый вход j-го элемента ИЛИ (j = 1,16) второй г руппы соединен с I-м информационным входом мультиплексора, выход (4i — 4 + t1-го элемента ИЛИ второй группы (t = 1,4) соединен с (t+2)-м входом i-ro элемента И, второй вход

6 и первым входом четвертого элемента

ИЛИ третьей группы, второй вход которого соединен с вторым входом второго элемента ИЛИ третьей группы и входом четвертого элемента НЕ, выход которого соединен с вторым входом первого элемента ИЛИ третьей группы и вторым входом третьего элемента

H1iN третьей группы.

5 15521 (4i — 4 + c) — го элемента ИЛИ второй группы соединен с выходом t-ro элемента ИЛИ третьей группы, первый вход первого элемента ИЛИ третьей группы соединен с первым входом второго элемента ИЛИ третьей группы и входом третьего элемента НЕ, выход которого соединен с первым входом третьего элемента ИЛИ третьей группы

Выход

Информационные входы

Адре сные входы

50

Ув У У<о Ун У<2 Ун Уи У 5

42 43 44 45 46 47 48 49

Уб

У7

Х Х Х3 Хф

30 31 32 33 о У У2

34 35 36

У У У

37 38 39

Х

Х

X

Х

Х

1

Х

Х

Х

Х

X X

Х Х

Х Х

Х Х

Х Х

0 0 0 0 0

0 0 0 0 1 Х

0 0 0 1 Х 0

0 0 0 E„X 1

0 0 1 0 Х Х

0 0 1 0 Х Х

0 0 1 1 X Х

0 0 1 1 Х Х

0 1 0 0 X Х

0 1 0 0 Х Х

0 1 0 1 Х Х

0 1 0 1 X Х

0 1 1 0 X Х

0 1 l 0 Х Х

0 1 1 1 Х Х

0 1 1 1 Х Х

1 0 0 0 Х X

1 0 0 0 Х Х

1 0 0 1 Х X

1 0 0 1 Х Х

1 0 1 0 Х X

1 0 1 0 Х Х

1 0 1 1 Х Х

1 0 1 1 Х Х

1 1 0 0 Х Х

1 1 0 0 Х Х

1 1 0 1 Х Х

1 1 0 1 Х Х

1 1 1 0 X Х

E 1 1 0 Х Х

1 1 1 1 Х Х

1 1 1 1 X Х

X Х X

Х Х Х

X Х X

Х X X

Х Х Х

Х Х Х

Х Х Х

Х Х Х

0 Х Х

1. X Х

Х 0 Х

X Х

Х Х 0

X Х 1

Х Х Х

X Х Х

X Х Х

Х X Х

X Х X

Х Х Х

Х Х Х

Х Х Х

Х X Х

Х Х Х

Х Х Х

Х Х Х

Х Х Х

Х Х Х

Х Х Х

Х Х Х

Х Х Х

Х Х Х

Х X

Х X

Х X

Х .Х

Х X

X Х

Х Х

Х Х

X Х

X X

Х Х

Х Х

Х Х

Х X

Х Х

Х Х

Х Х

Х Х

0 Х

1 Х

Х 0

X. 1

Х Х

Х Х

Х X

Х Х

X Х

Х Х

Х Х

Х "Х

Х Х

Х Х

X Х

Х Х

Х X

X Х

Х Х

Х Х

Х Х

Х Х

Х Х

X Х

Х Х

Х Х

Х Х

Х Х

X Х

Х Х

Х X

X Х

Х Х

Х Х

Х Х

Х Х

0 X

1 Х

Х 0

Х

Х Х

Х Х

Х Х

Х Х

Х Х

Х Х

Х Х Х

Х Х Х

Х Х Х

Х Х Х

X Х Х

Х Х .Х

Х Х Х

Х Х Х

Х Х Х

Х К Х

Х Х Х

Х ° Х Х

Х Х Х

X Х Х

Х Х Х

Х Х Х

Х Х Х

Х Х Х

Х Х Х

Х Х Х

Х Х Х

Х Х Х

Х Х Х

X Х Х

Х Х Х

Х Х Х

0 Х X

1 Х Х

Х 0 Х

Х 1 Х

Х Х 0

Х Х

1

1

1

1

1

1

1

1

1

1

1

0

0

1