Устройство для деления чисел

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, предназначено для деления чисел и может быть использовано при построении специализированных арифметических устройств. Цель изобретения - повышение быстродействия. Устройство для деления чисел содержит взаимосвязанные K-разрядный регистр делителя, управляемый делитель частоты, блок переноса кодов, распределитель импульсов, блок элементов И, блок счетчиков результата и два элемента И, а также (K + 1)-разрядный вычитающий счетчик делимого, триггер и два элемента ИЛИ. 1 ил.

СООЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМЪГ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 3888716/24-63 (22) 19.04.85 (46) 23.03.90. Бюл . Ф 11 (71) Специальное конструкторское бюро "Кибернетика" с опытным производством Института кибернетики

АН АЗССР (72) А.P. Салаев (53) 681.325 (088.8) (56) Авторское свидетельство СССР

У 615477, кл. С 06 F 7/60, 1977. Авторское свидетельство СССР

У 690480, кл. С 06 F 7/60, 1974.

Изобретение относится к вычисли. тельной технике и может быть использовано при построении арифметических устройств.

Целью изббретения является повышение быстродействия устройства.

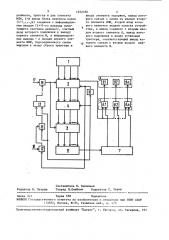

На чертеже представлена функциональная схема устройства для деления чисел.

Устройство содержит регистр 1 делителя, управляемый делитель 2 частоты, вычитающий счетчик 3 делимого, блок 4 переноса кодов, блок 5 элементов И 6,1-6.п распределитель

7 импульсов, блок 8 счетчиков 9.19.п результата, элемент 10 задержки, первый 11 и второй 12 элементы ИЛИ, триггер 13, первый 14 и второй 15 элементы И. Входами устройст„.80„„Щ2 1Я A 1 (51) 5 С 06 F 7/60

2 (54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЕЛ (57) Изобретение относится к вычислительной технике, предназначено, для деления чисел и может быть использовано при построении специализированных арифметических устройств.

Цель изобретения — повышение быстро действия. Устройство для деления чисел содержит взаимосвязанные К-разрядный регистр делителя, управляемый делитель частоты, блок переноса кодов, распределитель импульсов, блок элементов И, блок счетчиков результата и два элемента И, а также (К+1)разрядный вычитающий счетчик делимо=.

ro, триггер и два элемента ИЛИ, 1 ил. ва являются вход 15 запуска и вход

17 тактовых импульсов.

Устройство работает следующим .образом.

После занесения кода делителя А в регистр 1 делителя и кода делимого

В, отличного от нуля, в вычитающий счетчик 3 делимого импульс на входе

16 запуска через второй элемент ИЛИ

12 и второй элемент И 15 приводит триггер 13 в состояние, при котором разрешается прохождение тактовых импульсов с входа 17 через первый элемент И 14, Тактовые импульсы поступают на входы управляемого делителя 2 частоты и вычитающего счетчика 3 делимого. Каждый раз при равенстве числа в управляемом делителе 2 с числом

1552180

А в регистре 1 делителя управляемый делитель 2 выдает импульс, поступающий через открытый элемент И 6 ° 1 блока 5 элементов И на вход блока

8 счетчиков результата в счетчик 9.1.

Заполнение счетчика 9.1 происходит до тех пор, пока счетчик, 3, работающий в режиме вычитания, не окажется в нуле. При этом в счетчике Ч (,4)

9.1 образуется число )N 1, представляющее собой целую часть частнс1го от деления В на А. В управляемом делителе 2 находится остаточное число (NI 1, меньшее А.

Следующие разряды, число которых зависит от .требуемой точности результата деления, образуются следующим о разом. В момент, когда в вычитающ м счетчике 3 делимого устанавливается нуль, сигналом с выхода элемента ИЛИ 11 триггер 13 перебрасывается B состояние, при котором прекрфцается прохождение тактовых импульсов через первый элемент И 14, а остаточное число $ N) из управляемого делителя 2 посредством блока

4 переноса кодов со сдвигом на один разряд в сторону старших разряддв заносится в вычитающий счетчик

3 делимого.. Кроме того, сигнал с вых да элемента ИЛИ 11 через элемент

1 задержки устанавливает в нуль упр вляемый делитель 2, а также пос.тупает на вход распределителя 7 импульсов, в результате чего изменяется 3 состояние распределителя 7 Импульсов

ДЛя прохождения импульсов с выхода управляемого делителя 2 через элем 1нт И 6.2 блока 5 элементов И на в4од счетчика 9,2 блока 8 счетчиков

40 разультата.

Перенос остатка Nf из управляемого делителя 2 в вычитающий счетчик 3 делимого со сдвигом на Один 45 разряд в сторону старших разрядов соответствует умножению остатка на ве= личину С, где С вЂ” основание системы счисления. Поэтому при запуске устрОйства в работу через второй элемент 50

ИЛИ 12 сигналом с выхода элемента 10 задержки значение следующего разряда результата, получаемого в счетчике

9„2 блока 8 счетчиков результата, равно целой части частного от деленйя С (N) на А. Остаток снова засЦ носится со сдвигом в вычитающий счетчик 3 делимого для получения последующего разряда резупьтата в счетчике 9.3 блока 8 счетчиков результата и т.д. до выполнения с необходимой точностью операции деления.

При нулевом значении делимого В, а также при образовании нулевого остатка на какой-либо итерации сигнал с первого элемента ИЛИ 11 перебра ывает триггер 13 в состояние. при . отором запрещается прохождение тактовых импульсов через первый элемент

И 14, и одновременно посредством второго элемента И 15 блокирует запуск устройства в работу.

При нулевом значении делителя А не формируется сигнал на выходе управляемого делителя 2, поскольку коэффициент его деления находится в диапазоне от 1 до полной числовой еьжости регистра 1 делителя.

Формула изобретения

Устройство для деления чисел, содержащее К-разрядный регистр делителя, управляемый делитель частоты, блок переноса копов, распределитель импульсов, блок элементов И, блок счетчиков результата и два элемента И, причем выходы регистра делителя соединены с информационными входаьа управляемого делителя частоты, счетный вход которого подключен к выходу первого элемента И, один из входов которого является входом тактовых импульсов устройства, информационные выходы управляемого делителя подсоединены к информационным входам блока переноса кодов, управляющий вход которого связан с одним из входов второго элемента И и с входами элемента задержки и распределителя импульсов, каждый из выходов которого соединен с первым входом соответствующего элемента И блока элементов И, выход каждого элемента И блока подключен к счетному входу соответствующего счетчика блока счетчиков результата., а вторые входы всех элементов И блока подсоединены к импульсному выходу управляемого делителя частоты, выход элемента задержки подключен к входу установки в исходное состояние управляемого делителя частоты, о т л и ч а ю-, щ е е с я тем, что, с целью повьппения быстродействия, в него введены (К+1)-разрядный вычитающий счетчик.1552180

Составитель Н, Васильев

Техред Л-.Олийнык Корректор С, Черни

Редактор В. Петраш

Заказ 331 Тираж 558 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 делимого, триггер и два элемента

ИЛИ, i-й выход блока переноса кодов (i=i Е) соединен с информационным входом (i+.1)-ro разряда вычитающего счетчика делимого, счетный вход которого подключен к выходу первого элемента И, а информационные выходы — к входам первого элемента ИЛИ, подсоединенного своим . выходом к входу сброса триггера и входу элемента задержки, выход которого связан с одним из входов второго элемента ИЛИ, второй вход которого является входом запуска устройства, а выход соединен с вторым входом второго элемента И, выход которого подключен к входу установки триггера, соответствующий выход которого связан с вторым входом первого элемента И.