Устройство для обслуживания запросов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для сопряжения микро-ЭВМ с периферийными устройствами. Цель изобретения - повышение производительности. Устройство содержит два канала формирования адреса инициатора запроса, два дешифратора, две группы триггеров, J K-триггер, элемент И, коммутатор, блок коммутаторов. Каждый канал формирования адреса инициатора запроса содержит счетчик, мультиплексор, элемент ИЛИ и элемент И. В устройстве уменьшается время определения адреса инициатора запроса за счет сокращения разрядности счетчика, происходит параллельное определения адресов инициаторов запросов, если два запроса поступили одновременно в оба канала, обеспечивается переключение одного канала в активный, а другого - в пассивный режим. При этом активный канал определяет адрес инициатора запроса и передает его вместе с запросом на выход устройства, а пассивный только определяет адрес инициатора запроса и запоминает его для дальнейшей выдачи. Устройство позволяет запоминать факт прихода очередного запроса во время обслуживания текущего запроса и формировать адреса инициаторов запросов последовательно в зависимости от их значений и времени поступления от них запросов. 1 ил.

(19) (11) СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 5 G 06 F 9/46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОП(РЫТИЯМ

ПРИ ГКНТ СССР (21 4454910/24-24 (22) 05.07,88 (46) 23.03.90. Бюл. М - 11 (72) И.Д. Шапоров, Г.H. Тимонькин, С.Н. Ткаченко, С.А. Соколов, В.С. Харченко и А.В. Пименов

453) 681.325 (088.8) (56) Авторское свидетельство СССР

У 716039, кл. G 06 F 9/46, 1980.

Авторское свидетельство СССР

У 1056195, кл. G 06 F 9/46, 1982. (54) УСТРОЙСТВО ДЛЯ ОБСЛУЖИВАНИЯ

ЗАПРОСОВ (57) Изобретение относится к вычислительной технике и может быть ис--пользовано для сопряжения микроЭВМ с периферийными устройствами. Цель изобретения — повышение производительности Устройство содержит два канала формирования адреса инициатора запроса, два дешифратора, две группы триггеров, IK-триггер, элемент И, коммутатор и блок коммутатоИзобретение относится к вычислительной технике и может использоваться для сопряжения микроЭВМ с периферийными устройствами.

Целью изобретения является повышение производительности.

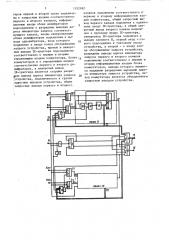

На чертеже приведена схема устройства.

Устройство содержит каналы 1.1 и

1.2 формирования адреса инициатора

2 ров. Каждый канал формирования адреса инициатора запроса содержит счетчик, мультиплексор, элемент ИЛИ и элемент

И. В устройстве уменьшается время определения адреса инициатора запроса за счет сокращения разрядности счетчика, происходит параллельное определение адресов инициаторов запросов, если два запроса поступили одновременно в оба канала, обеспечивается переключение одного канала в активный, а другого — в пассивный режимы. При этом активный канал определяет адрес инициатора запроса и передает его вместе с запросом на выход устройства, а пассивный толь- д ко определяет адрес инициатора запроса и запоминает его для дальнейшей выдачи. Устройство позволяет запоминать факт прихода очередного запроса во время обслуживания текущего запроса и формировать адреса инициаторов запросов последовательно в зависимости от их значений и времени поступления от них запросов. 1 ил.

СЛ запроса, дешифраторы 2 и 3, группы триггеров 4 и 5, IK-триггеров 6, элемент И 7, коммутатор 8, блок 9 коммутаторов, одновибратор 10, запросные входы 11, выход t2 адреса инициатора запроса, тактовый вход 13, выход 14 конца обслуживания запроса, объединенный запросный .выход 15.Каждый канал 1,1 и 1.2 содержит счетчик

" 16, мультиплексор 17, элемент ИЛИ 18, 1552182 эпемент И 19, группу 20 запросных входов, общий запросный выход 21, разрядные адресные вьгходы 22 канала.

Устройство работает следующим об5 разом.

В исходном состоянии запросы на входы 11 не поступают. Триггеры групп 4 и 5, счетчики 16 находятся в "0", элементы И 19 закрыты "0", поступающими с выходов элементов KIN

18, и запрещают прохождение тактовых импульсов с входа 13 на.-входы счет чиков 16. На выходах мультиплексоров

17 действуют нулевые сигналы, что свидетельствует об отсутствии запросов, и, следовательно, на выходе 15 будет "0". IK-триггер находится в произвольном состоянии. С входа 14 на вход элемента И 7 поступает единичный сигнал, извещающий устройство о том, что внешнее устройство управления свободно и готово к обслуживанию запросов.

Каждый канал 1.1 и 1.2 может Функ- 25 ционировать в активном или пассивном режиме. При работе в активном режиме в канале осуществляется формирование адреса инициатора запроса и выдача этого адреса на адресные выходы 12 устройства одновременно с выдачей на объединенный запросный выход 15 устройства единичного сигнала запроса. При работе в пассивном режиме в . канале осуществляется формирование адреса инициатора запроса, но он так же, как и запрос, с выхода канала на выход устройства не передается. Режимы каналов опредЕляются состоянием

IK-триггера 6. Если он находится в единичном состоянии, то канал 1.1

40 является активным, а канал 1.2 — пассивным. Если этот триггер находится в нулевом состоянии, то наоборот„

При поступлении запросов на один или несколько запросных входов 11 устройства устанавливаются в единичное состояние соответствующие триггеры первой 4 и второй 5 групп. Первый поступивший запрос в каждом канале

1.1 и 1.2 либо в одном из каналов че50 рез элемент ИЛИ 18 поступает на вход элемента И 19 и открывает его для прохождения тактовых импульсов с тактового входа 13 устройства на счетный вход С счетчика 16. 55

Счетчики 16 одного или обоих каI налов начинают подсчет числа импульсов. Текущий лвоичный код с выхода счетчика 16 поступает на.управляющие входы мультиплексора 17 соответствующего канала.. При этом к выходу мультиплексора 17 последовательно подключаются вьгходы триггеров группы 4 для первого канала или выходы триггеров группы 5 для второго канала. Когда двоичный код на выходе счетчика 6 совпадает с адресом источника, записавшего сигнал запроса в один из триггеров первой 4 либо второй 5 группы, на выходе соответствующего мультиплексора 17 возникает единичный сигнал, означающий, что адрес инициатора запроса сформирован. Этот сигнал, поступая на инверсный вход элемента И 19, запирает его, счетчих останавливается, и в нем будет записан код адреса инициатора запроса, который через адресные выходы 22 соответствующего канала поступает на информационные входы блока 9 коммутаторов. Одновременно единичный сигнал в качестве обобшенного запро— ного сигчала с выхо, Jà 21 канала поступает на информационные входы коммутатора 8.

Предположим, что первым сформирован адрес инициатора запроса в первом канале 1.1 ° Тогда, если IK-триггер 6 находится в единичном состоянии, единичный сигнал с запросного выхода

21.1, поступая íà I-вход IK-триггера, оставляет его в том же состоянии.

Если IK-триггер находится в нулевом состоянии, то через открытый сигналом с входа 14 устройства элемент И 7 синхроимпульс с тактового входа 13 поступает на С-вход IK-триггера и своим задним фронтом устанавливает

его в единичное состояние, делая первый из каналов активным;. При этом сигнал запроса и код адреса инициатэра запроса с выхода канала 1,1 проходят, соответственно,, через коммутатор 8 на объединенный запросный выход 15 и через блок 9 коммутаторов на адресную выходную шину 12, При этом в старший разрядный выход шины

12 с инверсного выхода триггера 6 передается нулевой сигнал. После приема запросного сигнала с выхода 15 внешнее управляющее устройство начинает его обслуживание и снимает о входа 14 устройства единичный сигнал, что запрещает работу элемента ."4 7 и, следовательно, делает переключе1552

45 ние триггера 6 невозможным. Режим каналов меняться не может.

После окончания обслуживания данного запроса внешнее управляющее

5 устройство устанавливает на входе 14 единичный сигнал. Передним фронтом

1 этого сигнала запускается одновибратор 10. С выхода одновибратора !О импульс, длительность которого дос- 10 таточна для гарантированного сброса триггеров групп 4 и 5, поступает на синхровходы дешифраторов 2 и 3, Но единичный сигнал появляется на одном из выходов только одного дешифратора, 15 так как единичный сигнал с прямого или инверсного выхода триггера 6 поступает на управляющий вход одного из дешифраторов. Для рассматриваемого случая открыт дешифратор 2, На 20 информационные входы дешифратора 2 поступает при этом со счетчика 16 код адреса источника обслуженного запроса. Следовательно, в момент срабатывания одновибратора 10 дешифра- 25 тор 2 выдает импульс сброса того триггера 4, в котором был записан обслуженный запрос, После этого на выхо- . де 21 канала появляется нулевой сигнал и с выхода 15 устройства снима- 30 ется общий сигнал запроса. Канал 11 может приступать к формированию адреса очередного источника запроса, если к этому времени запрос записался в один из триггеров группы 4.

Если к моменту окончания обслуживания запроса в канале 1. 1, в канале

1.2 сформирован адрес источника нового запроса, то на выходе 21 канала

1.2 наблюдается единичный сигнал, 40 который поступает на К-вход IK-триг- . гера. После появления единичного сигнала на входе 14 устройства, а его появление предусмотрено только в паузах между тактовыми импульсами, по заднему фронту первого же синхроимпульса триггер 6 переключается в нулевое состояние, Единичный сигнал с инверсного выхода триггера 6 открывает вторые половины коммутатора 8 и блока 9 коммутаторов, и обобщенный запрос и адрес инициатора запроса с выходов 21 и 22 соответственно канала 1.2 поступает на выходы 15 и 12 устройства. Канал 1.2 становится активным, а канал 1.1 — пассивным. Общий обслуживающий орган принимает к обслуживанию запрос канала 1.2.. В это время канал 1.1 может продолжать

182 6 формировать адрес инициатора очередного запроса.

Если в определенный момент времени оба канала одновременно сформируют адреса инициаторов, то единичные сигналы с выходов 21 каналов 1.1 и

1.2 одновременно поступают íà I- u

К-входы триггера 6. В этом случае триггер переходит в инверсное состояние, и устройство подключает к обслуживающему органу сначала один запрос, затем другой, Формула и з обретения

Р

Устройство для обслуживания запросов, содержащее два дешифратора, две группы из и триггеров каждая (где

n = N/2, N — количество запросов источников запросов) и первый канал формирования адреса инициатора запроса, включающий счетчик, мультиплексор, элемент И и элемент ИЛИ, при этом счетный вход счетчика соединен с выходом элемента И, прямой вход которого соединен с тактовым входом устройства, выход мультиплексора является общим запросным выходом канала и подсоединен к инверсному входу элемента И, второй прямой вход которого подсоединен к выходу элемента ИЛИ, и входов элемента ИЛИ являются запросныы входами канала и подсоединены к соответствующим информационным входам мультиплексора, К разрядных выходов счетчика (где К = log п— число разрядов двоичного кода числа, подключаемых к каналу источников запросов) подключены к соответствующим управляющим входам мультиплексора и являются разрядными выходами адреса инициатора запроса канала, запросные входы устройства с первого по и-й и с (и+1)-го по N-й соединены соответственно с $-входами соответствующих триггеров первой и второй групп, R-входы которых соединены с соответствующими выходами соответственно первого и второго дешифраторов, о т л и ч а ю щ е е с я тем, что, с целью повышения производительности, в него дополнительно введены второй канал формирования адреса инициатора запроса, IK-триггер, коммутатор, блок коммутаторов, элемент И и одновибратор, при этом С-входы триггеров пер-вой и второй групп подключены к тактовому входу устройства и к первому входу элемента И, прямые выходы триг1552182

1epos первой и второй групп подключеНы к запросным входам соответственно

Первого и второго каналов, информационные входы обоих дешифраторов

Подсоединены к разрядным выходам адреса инициатора запроса соответст вующего канала, входы синхронизации обоих дешифраторов подключены к вы оду одновибратора, вход которого подключен к входу конца обслуживания ,запроса устройства, прямой и инверсный выходы IK-триггера подсоединены соответственно к первым и вторым управляющим входам коммутатора, блока 1 коммутаторов и к управляющим входам соответственно .первого и второго дешйфраторов, а инверсный выход

IK-триггера является старшим разря,дом выхода адреса инициатора запроса устройства, подключенного к группе

1 . адресных выходов устройства, общие ,запросные выходы первого и второго каналов подключены соответственно к первому и второму информационным входам коммутатора, общий запросный выход первого канала подключен к единичному входу IK-триггера, а общий запросный выход второго канала подключен к нулевому входу IK-триггера, синхровход 1К-триггера подключен к выходу элемента И, первый вход к второго подсоединен к тактовому входу устройства, а второй — к входу конца обслуживания запроса устройства, разрядные выходы адреса инициатора запроса первого и второго каналов подключены соответственно к первым и вторым информационным входам блока коммутаторов, выходы которого являются младшими разрядными выходами адреса инициатора запроса устройства, вы— ход коммутатора является объединенньм запросным выходом устройства.