Статический преобразователь частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к силовой преобразовательной технике. Его целью является повышение перегрузочной способности путем уменьшения времени коммутации тиристоров инвертора. Устройство содержит последовательно соединенные управляемый выпрямитель 1, дроссели 2, 3 зашунтированные тиристорами с управляющими входами Н1, Н2, инвертор 4 и мост коммутирующих тиристоров. Блок управления обеспечивает заданный алгоритм управления устройством. В моменты коммутации тиристоров моста реактивность нагрузки выводится из контура их коммутации, в результате чего коммутация осуществляется в минимально возможное время. 2 ил.

СОО3 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н M 5 45

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCMGMV СВИДЕТЕЛЬСТВУ

3®

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

flO ИЗОБРЕТЕНИЯМ И 01КРЫТИЯМ

flPH ГКНТ CCCP

1 (2 1) 4450765/24-0 7 (22) 27.06, 88 (46) 23.03. 90. Бюл, 11 1 l (71) Ленинградское производственное электромашиностроительное объединение "Электросила" им.С.M,Êèðoâa (72) В.И.Эпштейн (53) 621,314.27 (088.8), (56) Richter М. Mi croprocesser

controlled. invert er-red Synchronous

motor drive. "2-nd -Int. Conf. Elec.

Variabl-Speed Driv,. London, 1979.

1.ondon - Nm York, 1979, . р. 161-614, Авторское свидетельство СССР

У 686125, кл. Н 02 К 29/04, 15.12,77, 2 (54) СТАТИЧКСКИЙ 11РЮБРАЗОВАТРЛЬ ЧАСТОТЫ (57) Изобретение относится к силовой преобразовательной технике. Его целью является повышение перегрузочной способности путем уменьшения времени коммутации тиристоров инвер" тора, Устройство содержит последовательно соединенные управляемый вып" рямитель 1, дроссели 2,3, зашунтированные тиристорами с управляющими входами Hl, Н2, инвертор 4 и мост коммутирующих тиристоров. Блок управ;ления обеспечивает заданный алгоритм,. управления устройством.В моменты коммутации тиристоров моста реактивность

1552313

V5 = Sl S2 Р5

V6 = S1.$2 Ð2

+ S2-Р5;

+ $2 ° Р2, Hl = L2 + L4 + L6

Н2 = L2 + LÇ + L5, нагрузки выводится из контура из коммутации в результате чего коммут.ация

Изобретение относится к электро. технике и может быть использовано для управления частотой вращения мощного синхронного двигателя.

Цель изобретения — повышение перегрузочной способности путем уменьшения времени коммутации тиристоров инвертора, а также исключение необходимости организации средней точки нагрузки и соединения этой точки с выводами коммутирующих тиристоров.

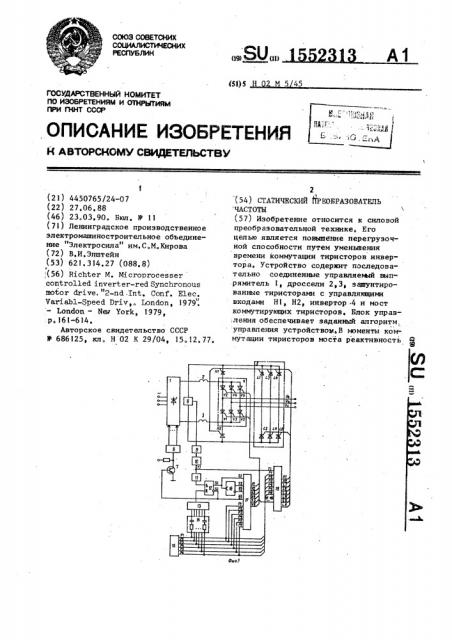

На фиг,l показана структурная схема предлагаемого устройства на фиг. 2-- временные диаграммы, поясняющие его работу.

Статический преобразователь частоты содержит последовательно соединенФ ные управляемый выпрямитель l,дроссели 2 и 3 и инвертор 4 на тиристорах с управляющими входами Vl — Чб, Выводы переменного тока инвертора 4 подключены к общим точкам цепочек последовательно включенных между вывода- О ми постоянного тока выпрямителя 1 коммутирующих тиристоров с управляю" щими входами Ll — Lá, образукицими узел 5 коммутирующих тиристоров.

Причем, подключение указанного узла

5 к выводам переменного тока инвертора 4 выполнено так, что коммутирующие тиристоры с управляющими входами Ll—

L6 соединяются основными выводами с одноименными выводами тиристоров инвертора 4, управляющими входами которых являются соответственно,Vl—

Чб, Например, анод коммутирующего .ти-, ристора с управляющим входом LÇ соединяется с анодом тиристора инвертора 45

4, управляющим входом которого является вход ЧЗ, и т,д, Параллельно дросселям 2 и 3 включены шунтирующие тиристоры с управляющими входами Hl и Н2, а параллельно входу системы 6 импульсно-фазового управления выпрямителем 1 подключается ключ 7. К выводам постоянного тока выпрямителя 1 подкпючен датчик 8 выпрямленного напряжения, выход которого подключен к входу цепи из последовательно сое55 диненных компаратора 9, первого одновибратора 10 с выходным сигналом Т1, BTopora одновибратора 11 и триггера осуществляется в минимально возможное время, 2 ил..12 с парафазными выходами Sl u Sl второй установочный вход которого подключен к выходу шестивходового логического элемента 13, реализующего логическую функцию "б ИЛИ" и входами связанного через дифференцирующие звенья 14 с выходами Pl — Рб системы

15 импульсно-фазового управления инвертором 4. Инверсный выход Sl триггера 12 соединен с управляющим входом ключа 7, а его прямой выход $1 подключен к счетному входу второго триггера 16 с парафазными выходами S2, S2. Управляющие входы Vl — Vá тиристоров инвертора подключены к выходам первого логическоro узла 17, который выполнен реализующим логические вы- . ражения

Ч! = Sl S2 Pl + S2.Pl;

V2 = $1 82 Р4 + 82.Р4;

V3 = $1 ° 82 ° РЗ + $2 PÇ;

U4 = Sl ° $2 Рб + $2Рб; для чего входы упомянутого логического узла 17 подключены к соответствующим входам триггеров 12 и 16 и к выходам Рl — Рб системы 15 импульснофазового управления тиристорами инвертора 4, ;выходы второго логического узла

18 связаны с управляющими входами

L l — 1.6 коммутирующих тиристоров и с управляющими входами Нl и Н2 шунтнрующих тиристоров, Дан" ный логический узел 18 реализует логические выражения

L1 = Тl ° PÇ VÇ;

L2 T l Рб Ч4;

L3 = Тl Р5 ° V5;

L4 = Т1 Р2 Uá

L5 = Tl-Р1 Ч1;

L6 = Tl Р4 Ч2;

155231

L2 = T1 ° Рб ° V4

НI = L2 + L4 + Lá при соответствующем подключении его входов.

Выходные напряжения (1арUb и 11с инвертора 4, имеющие приблизительно

5 синусоидальный характер, изображены на фиг„2, Адекватно их последовательности на выходах Pl — Рб системы

15 импульсно-фазового управления инвертором формируется последовательность импульсов для управления тиристорами, Причем фазовый сдвиг между указанными последовательностями, обозначенный на временной диаграмме (фиг.2), устанавливается обычно воз- 15 можно более близким к 180 эл.град, относительно точек естественной коммутации тиристоров инвертора 4 для минимизации реактивной составляющей мощности на выходе преобразователя 20 частоты, Моментам окончания импульсов на выходах Р1 . Рб системы 15, фиксируемым при помощи дифференцирующих звеньев 14, соответствуют моменты установки триггера 12 в нулевое положе- 25 ние по выходу Sl. Установка его в противоположное состояние осуществляется импульсом с выхода одновибратора

11 момент появления которого отстоит от. момента изменения знака выходного 30 напряжения IJ выпрямителя 1 на величину длительности импульса T l формируемого одновибратором 10, Интервалы нулевого состояния выхода S l триггера 12 соответствуют таким обра- 35 зом времени, необходимому выпрямителю 1 на переход в инверторный режим (напряжение Ц, фиг,2) и последующим интервалам, задаваеиим сигналом Тl для восстановления вентильной проч- 40 ности тиристоров инвертора 4. Сигналы на выходах S2, Г2 триггера 16 со счетным входом определяют очередность запрета на формирование импульсов на выходах Vl — Чб логичес- 45 кого узла 17 для управления тиристо1рами катодной и анодной групп инвертора 4. Одновременно с появлением сигналов на выходе Tl одновибратора

10 формируются импульсы на выходах 50

Ll — Ьб, Н1 и Н2 для включения коммутирукищих и шунтирунщих тиристоров, Преобразователь частоты работает следунщим образом.

При включении очередного тиристора инвертора 4, например тиристора с управляницим входом Ч4, и выключении предыдущего, а именно, тиристора с

3 6 управляющим входом U2, по срезу импульса Р4 управления последним, формируемым на выходе на выходе системы

I 5 импульсно-фазового управления инвертором 4, через дифференцирующие звенья 14 и логический элемент 13, реализующий логическую функцию

"6 ИЛИ", триггер I? переключается в состояние, соответствуницее закорачиванию входа системы 6 импульсно-фазового управления выпрямителем 1. Осу ществляется это в результате воздействия сигнала с инверсного выхода S I триггера 12 на управляющий вход ключа 7. При этом выпрямитель 1 переводится в инверторный режим работы. В момент изменения знака напряжения на его выходе, фиксируемый посредством датчика 8 выражения и компаратора 9, запускается одновибратор

10, выходной сигнал TI которого, воздействуя на вход второго логического узла 18, в соответствии с логичес ким выражением приводит к включению коммутирующего тиристора с управйяннцим входом Ь2.

Этот же импульс используется в соответствии с логическим выражением для одновременного включения шунтирующего тиристора с управляющим входом Hl. В результате отрицательное напряжение с выхода выпрямителя

1 через открытые коммутирующий тиристор с управляющим входом L2 и шунтирунхций тиристор с управляющим входом

HI прикладывается к тиристору инвертора 4 с управляющим входом V2 и запирает его, Ток, до этого протекавг ший через него, нагрузку и тиристор с управлянщим входом Ч5, замыкается по цепи, включаницей фазы нагрузки, тиристор с управляющим входом Ч5, дроссель 3 и тиристор с управляющим входом L2. В этом контуре (фиг,2) действует линейное напряжение нагрузки

U которое стремится запереть тиристоры с управляющими входами Ч5, Ь2, но этому препятствует дроссель 3.

После выдержки времени, необходимой для восстановления запирающих свойств тиристора с управляющим входом V2, соответствующей длительности импуль"

1552313 са Тl. на выходе одновибратора 10, запускается одновибратор 11, триггер

12 переключается в исходное состояние, ключ 7 размыкается, восстанавли- 5 вается выпрямительный режим выпрямителя 1. Переключение триггера 12 в исходное состояние и соответствующее состояние триггера 16 (Фиг. ? ) прекращает запрет на прохождение импульса

Р6 с выхода системы 15 импульсноФазового управления на управляющий вход V4 тиристора инвертора 4, Осуществляется это первым логическим уз-лом 17, реализующим формирование ука-15 занного импульса М в соответствии с логическим выражением

74 = Sl $? Р6 + $2 Р6

После включения тиристора с управ- ляющим входом V4 запираются тиристоры с управляющими входами L2 и Н1, Ток переводится в основной контур, образованный выпрямителем 1, дросселями 2. и 3, тиристорами инвертора 4 с управляющими входами Ч4, U5 и последующими фазами (например, Ь,с) нагрузки, Таким образом, реактивность нагрузки в предлагаемом устройстве выводится из контура коммутации тиристоров инвертора во вспомогательный контур и коммутация осуществляется в минимальнО вОзмОжнОе Время, чтО способствует повышению перегрузоч35 ной спо со био сти преобразователя частоты.

Формула изобретения

Статический преобразователь частоты, содержащий инвертор с управляющими входами Vl — V6, выводы постоянного тока которого через дроссели, шунтированные первым и вторым шунтирующими тиристорами с управляющими входами Hl Н2 подключены соответственно к катодному и анодному выводам управляемого выпрямителя, основную

5О цепочку по следовательно соединенных .первого и второго коммутирующих тиристоров с управляющими входами Ll

L2, включенную между выводами постоянного тока управляемого выпрямителя, систему импульсно-фазового управ55 пения выпрямителем с подключенным па" раллельно ее входу ключом, систему импульсно — фазового управления инверР тором с выходными сигналами Pl -Р6, последовательность которых соответствует последовательности фаз выход ных напряжений инвертора,и шесть дифференцирующих звеньев, входы которых подключены к выходам системы импульсно-фазового управления инвертором, отличающийся тем, что, с целью повышения перегрузочной способности путем уменьшения времени коммутации тиристоров инвертора, он снабжен двумя аналогично выполненными и подключенными к шинам постоянного тока выпрямителя дополнительными цепочками попарно последовательно включенных третьего и четвертого, пятого и шестого коммутирующих тиристоров с управляющими входами соответственно 1.3 — Ь6, а точки соединения тиристоров этих дополнительных и основной цепочки соединены с выходными выводами инвертора,так,что коммутирующие тиристоры с управляющими входами

Е1 — 16 соединяются основными выводами с одноименными выводами тиристоров инвертора, управляющими входами которых являются соответственно входы

Vl — 76, шестивходовым логическим элементом 6 ИЛИ, входы которого подключены к выходам упомянутых дифференцирующих звеньев, цепью из последовательно включенных датчика выпрямленного напряжения выпрямителя„ компаратора, первого одновибратора .с выходным сигналом Тl, второго одно1 вибратора и первого триггера с парафазными выходами S I Sl второй установочный вход которого подключен к выходу упомянутого логического эле-! мента 6ИЛИ, а инверсный выход $1 ,к управляющему входу ключа, вторым триггером с парафазными выходами $2> S2 . счетным входом, подключенным к основному выходу Sl первого триггера, и двумя логическими узлами, причем первый" логический узел связан с управляющими входами Vl — Ч6 тиристоров инвертора и выполнен реализующим логические выражения

Vl = S1 S2 Рl + S? PI;

V2 = Sl S2-P4 + S2 Р4;

ЧЗ = $1 ° $? P3 + S2 РЗ;

V4 = S1 S2 P6 + S2 Р6;

V5 = Sl Г2 Р5 + S2.Р5;

V6 = Sl S2*P2 + $2 P2, ! 5523!3!

О а второй логический узел выходами связан с управляющими входами L!—

Ь6 коммутирующих тиристоров и с управляющими входами Н1, Н2 шунтирующих тиристоров и выполнен реализующим

5 логические выражения

Ь! Tl РЗ V3;

Ь2 - "Tl ° P6.V4;

ЬЗ Т ° Р5 75

Ь4 T l ° Р2. V6;

L5 Т! Р Ч1;

Ь6 Tl ° Р4 U2

Н! = L2 + L4 + L6;

Н2 Ll + L3 + L5. /с

Составитель Т,Мыцык

Редактор Е,Папп Техред М.Дидык

Корректор С.Шевкун

Ю

Заказ 337 Тираж 491 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Рауаская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101 !