Устройство для частотного разделения многоканального цифрового сигнала

Иллюстрации

Показать всеРеферат

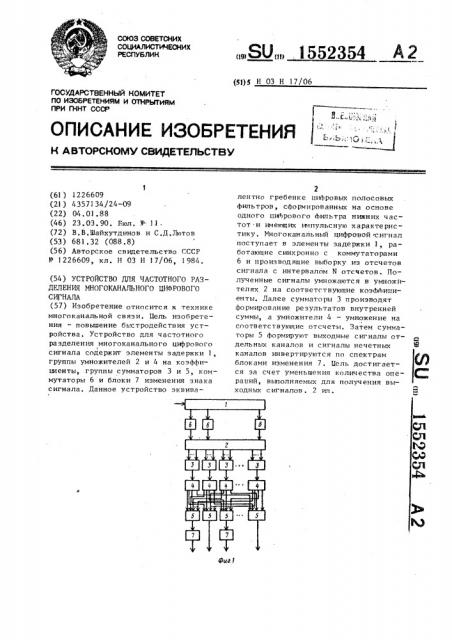

Изобретение относится к технике многоканальной связи. Цель изобретения - повышение быстродействия устройства. Устройство для частотного разделения многоканального цифрового сигнала содержит элементы задержки 1, группы умножителей 2 и 4 на коэффициенты, группы сумматоров 3 и 5, коммутаторы 6 и блоки 7 изменения знака сигнала. Данное устройство эквивалентно гребенке цифровых полосовых фильтров, сформированных на основе одного цифрового фильтра нижних частот и имеющих импульсную характеристику. Многоканальный цифровой сигнал поступает в элементы задержки 1, работающие синхронно с коммутаторами 6 и производящие выборку из отсчетов сигнала с интервалом N отсчетов. Полученные сигналы умножаются в умножителях 2 на соответствующие коэффициенты. Далее сумматоры 3 производят формирование результатов внутренней суммы, а умножители 4 - умножение на соответствующие отсчеты. Затем сумматоры 5 формируют выходные сигналы отдельных каналов и сигналы нечетных каналов инвертируются по спектрам блоками изменения 7. Цель достигается за счет уменьшения количества операций, выполняемых для получения выходных сигналов. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) Н 03 Н 17/06

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АBTOPCHOMY СВИДЕТЕЛЬСТВУ

Фиа.!

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ (61 ) 1226609 (21 ) 4357) 34/24-09 (22) 04.01 ° 88 (46) 23.03.90. Бюл. М -- )1 . (72) В.В.Шайхутдинов и С.Д.Лютов (53) 681,32 (088.8) (56) Авторское свидетельство СССР

Р 1226609, кл, Н 03 Н 17/06, 1 984. (54) УСТРОЙСТВО ДЛЯ ЧАСТОТНОГО PA3—

ДЕЛЕНИЯ МНОГОКАНАЛЬНОГО ЦИФРОВОГО

СИГНАЛА (57) Изобретение относится к технике многоканальной связи. Цель изобретения — повышение быстродействия устройства. Устройство для частотного разделения многоканального ци) рового сигнала содержит элементы задержки I, группы умножителей 2 и 4 на коэффициенты, группы сумматоров 3 и 5, коммутаторы 6 и блоки 7 изменения знака сигнала. Данное устройство эквива„„SU„„1552354 А 2 лентно гребенке цифровых полосовых фильтров, сформированных на основе одного цифрового Ьипьтра нижних частот.и имеющих импульсную характеристику. Многоканальный цифровой сигнал поступает в элементы задержки 1, ра— ботающие синхронно с коммутаторами

6 и производящие выборку из отсчетов сигнала с интервалом N отсчетов. Полученные сигналы умножаются в умножйтелях 2 на соответствующие коэбйициенты. Далее сумматоры 3 производят формирование результатов внутренней суммы, а умножители 4 — умножение на соответствующие отсчеты. Затем сумматоры 5 формируют выходные сигналы отдельных каналов и сигналы нечетных каналов инвертируются по спектрам блоками изменения 7. Цель достигается за счет уменьшения количества операций, выполняемых для получения выходных сигналов. 2 ип.

15523 54

Устройство для частотного разделения многоканального цифрового сигнала содержит элементы l задержки, первую группу умножителей 2 на коэффипиенты, группу сумматоров 3, группы умножителей 4 на.коэффициенты, группу сумматоров S, коммутаторы Ь и блоки

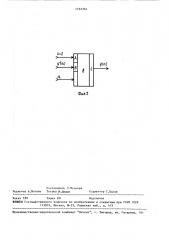

7 изменения знака сигнала. Клок 7 содержит арифметико-логическое устройство 8.

Частота дискретизации сигналов F на выходе устройства согласно теореме Котельникова должна удовлетворять услов ию

F >2Af, где A f — ширина полосы одного канала.

Если частота дискретизации многоканального сигнала (MC) кратна

f =NF (2) а i-й канал МС расположен в полосе частот

F . F

---1 а g < — -(j + 1)

2 2

У (Э) то уменьшение частоты дискретизации в N раз может быть выполнено путем взятия только каждого N-ro отсчета сигнала, т.е. путем отбрасывания (N

l) отсчетов из каждых N отсчетов сигнальной последовательности, причем спектр сигнала i-го канала переноГ сится в полосу (Π— — -) с инверсией, если i нечетно, и без инверсии, если i четно.

Частотное разделение многоканаль. ного цифрового сигнала осуществляется следующим образом.

Изобретение относится к ци2<ровой многоканальной связи, предназначено для выделения канальных сигналов из группового сит нала с частотным разделением каналов и является усовершенствованием устройства по основному авт, св. Р 1226609.

Бель изобретения — повышение- быстродействия устройства.

Поставленная цель достигается за. счет уменьшения количества операций, выполняемых для получения выходных сигналов °

На фиг. l приведена электрическая структурная схема устройства для частотного разделения многоканального цифрового сигнала, на Фиг,2 - блок изменения знака сигнала. центральная частота i-ro канала согласно (3) равна

F . F

+ — -(i + 1)

2 2 е2

27 — -(2i — 1) .

4 (4)

Нормированная к fp велич ина центральной частоты 1-го канала определяется формулой < = — — -(2з. — 1) = — -(2д — 1), (5)

q М где q = 4N, М = 2N, Устройство для частотного разделения цифрового MC эквивалентно гребенке цифровых полоеовых Ьитьтров (ЦЛФ), сформированныхна .основе одного ðoвого фильтра нижних частот (ЦФНЧ) и имеющих импульсную характеристику

21 ° (n) h(n) сов я. и, (6) где h (n) и h(n) — импульсные харак< теристики i-ro ЦПФ и ЦфНЧ.

i-го ЦПФ опредесве ртки

Сигнал на выходе ляется соотношением

3Р 4<- у (n) = Mh.(k)

1<1 k=- o

= h(k)cos (.>; kx(n

x (n — k) (7) K:о

Ю 10 Периодичность последовательности сов ИЛс. со {7,2 = (1 ) сов (<«(k + 1М) е позволяет сгруппировать слагаемые с равными по абсолютной величине множителями cosQ;k и привести выражение (7) к виду

М-> л

-1

Н<

«

<<< у. (п) = cos---(2i — 1) m (-1)«

« = о М =о

«Ь(ш + 1M) x(n — m — 1ш) . (8) Произведя выборку каждого N-го отI счета из у. (и), получают следующее выражение для сигнала íà i-м выходе устройства

y. (n) = (-1) у. (nN), (9) а с учетом (8) 35 где x(n) — последовательность отсчета МС;

N — длина последовательности

h(n).

1552354

М-I у (п) = (-! ) cosu;m (-1) х б

Е=O

s k(m + 1М)х(Н„- 1И вЂ” m). (! О) 5

Наличие множителя (-1) в (9) и (1 0) обусловлено необходимостью инверсии спектров сигналов в нечетных каналах, которая осуществляется изменением знака каждого второго отсчета. Если у(п) и у(е ) соответственно сигнал и его спектр, то преобразоваи ние Фурье последовательности (-1) >y(n) дает

15 (-1) y(n) е = 0 y(n)e

Д а - 0 rl =-™О

= У(е 1 где у(е 1 — инвертированный

g

Устройство работает следующим o6разом.

Многоканальный питеровой сигнал по25 ступает в цифровые элементы 1 задержки, работающие синхронно с коммутаторами 6 и производящие выборку из отсчетов сигнала с интервалом N отсче— тов. Полученные сигналы в умножителях

2 умножаются на .соответствующие коэффициенты базового ЦФНЧ, расчитанного из условия, что его полоса пропускания в два раза уже требуемой полосы пропускания формируемых цифровых полосовых фипьтров. Формирование ре- 35 зультатов внутренней суммы в выражении (8) производится группой суммато— ров 3, умножение на отсчеты последо— вательности cosi< /2N(2i — )m — груп— лами умножителей 4. Сумматоры 5 объе- 40 диняют выходы умножителей 4 и дюрмируют выходные сигналы отдельных каналов. Сигналы нечетных каналов инвертируются по спектрам блоками 7.

Конкретная техническая реализация 45 блока 7 определяется кодом, которым представлены отсчеты входного цифрового сигнала.

Если отсчеты сигнала представлены в прямом двоичном коде с фиксирован— ной запятой, то блок 7 представляет собой схему сложения по модулю два (ИСКЛК!ЧАЮШЕЕ KIH), на один вход которой последовательно с частотой F поступают знаковые разряды отсчетов сигнала a>(n), на другой — прямоугольные импульсы с частотой следования F/2 и скважностью 2, которые устанавливают на входе элемента ИСКЛ!ОЧА!ОШЕЕ ИЛИ уровень логической едиHHIIbl и тем самым обеспечивают инвертирование каждого второго отсчета сигнала °

При представлении отсчетов цифрового сигнала в двоичном дополнительном коде для интертирования отсчета необходимо вычесть его из числа 2. В этом случае блок 7 представляет собой арифметико — логическое устройство (АЛУ) 8, на вход А которого подается код числа 2, на вход  — последовательность отсчетов альтернируемого

/ сигнала у (п), на управляющий вход импульсы с частотой следования F/2 и скважностью, равной двум (Аиг,2) .

Инвертирование каждого второго отсчета сигнала обеспечивается тем, что при наличии на управляющем входе импульса (уровня логической единицы)

АЛУ 8 устанавливается в режим вычитания (С = А — В), а при поступлении на управляющий вход логического нуля (отсутствие импульса) АЛУ 8 устанавливается в режим повторения (С = В), Формула изобретения

Устройство для частотного разделения многокан аль но го u>&popcorn сигнала по авт. св. Р 1226609, о т л и ч ающ ее с я тем, что, с целью повышения быстродействия, выход >.-го элемента задержки подключен к входу

1-го умножителя на коэФЙиииент первой группы через i-й коммутатор, а выходы каналов устройства с нечетными номерами соединены с входами соответствующих блоков изменения знака сигнала.

1552354

Составитель С.Муэычук

Редактор А.Мотыпь Тех ред М.Дидык Корректор Т.Палий

Заказ 339 Тираж 651 Подписное

3НИИПИ Государственного комитета по изобретениям и открьггиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101