Устройство для передачи и приема дискретных сообщений

Иллюстрации

Показать всеРеферат

Изобретение относится к технике связи. Цель изобретения - повышение помехоустойчивости. Устройство содержит на передающей стороне источник 1 сообщений, регистр 2 сдвига, фазоразностные манипуляторы 3 и 6, передатчик 4, генератор 5 несущей частоты, сумматор 7 по модулю два и блок синхронизации 8, а на приемной стороне приемник 9, два идентичных канала 10 обработки сигналов, состоящие каждый из фазового детектора 11, линии задержки 12 и блока выбора 13 минимума, многоканальный коммутатор 14, запоминающие устройства 15 и 25, дешифратор 16, ключ 17, регистр 18 сдвига, сумматор 19 по модулю два, коммутатор 20, декодеры 21 и 26, блок синхронизации 22, умножители 23 и 29 частоты на два, фазовый детектор 24, блоки задержки 27 и 28 и фазовращатель 30, а также линию связи 31. Цель достигается за счет обеспечения обнаружения и исправления определенных ошибок, возникающих на выходе фазового детектора 11 и декодера 21, при воздействии помех. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51)5 Н 04 L 27/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ .ПРИ ГКНТ СССР (21) 4385232/24-g9 (22) 29.02.88 (46) 23.03.90. Бюп. ¹ 11 (71) Воронежский политехнический ин ститут (72) В.И.Ледовских (53) 621.391.23(088.8) (56) Заездный А.И., Окунев Ю.Б., Рахович Л.М. Фазоразностная модуляция и ее применение для передачи дискретной информации. - M. Связь, 1967, с. 146, рнс. 3-24 (передающая часть), с. 97, рис. 2.31 (приемная часть) . (54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА

ДИСКРЕТНЫХ СООБЩЕНИЙ (57) Изобретение относится к технике связи. Цель изобретения — повышение помехоустойчивости. Устр-во содержит на передающей стороне источник 1 со,, 80„„15523 4 A 1

2. общений, регистр 2 сдвига, фазоразностные манипуляторы 3 и 6, передатчик 4, генератор 5 несущей частоты, сумматор 7 по модулю два и блок синхронизации 8, а на приемной стороне приемник 9, два идентичных канала

10 обработки сигналов, состоящие каж дый нз фазового детектора 1 1, линии задержки 12 и блока выбора 13 миниму-. ма, многоканальный коммутатор 14, запоминающие устр-ва 15 и 25, дешифратор 16, ключ 17, регистр 18 сдвига, сумматор 19 по модулю два, коммутатор

20, декодеры 21 и 26, блок синхронизации 22, умножители 23 и 29 частоты на два, фазовый детектор 24, блоки задержки 27 и 28 и фазовращатель 30, а также линию связи 31. Цель достигается за счет обеспечения обнаружения и исправления определенных ошибок, возникающих на выходе фазового детектора 1 l и декодера 21, при воздействии помех. 2 ил.

1552394

Изобретение относится к технике связи и может использоваться при построении систем передачи цифровой информации °

Цель изобретения — повышение помехоустойчивости.

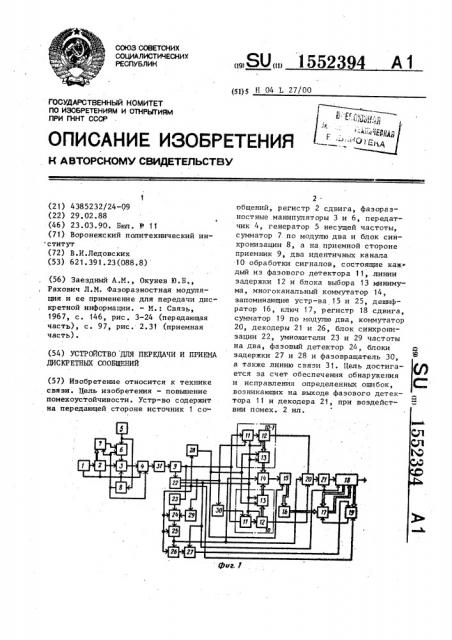

На фиг. 1 приведена структурная электрическая схема устройства; на фиг. 2 — временные диаграммы, поясняющие его работу.

Устройство для передачи и приема дискретных сообщений содержит на передающей стороне источник 1 сообщений, регистр 2 сдвига, первый фа- 15 зоразностный манипулятор 3, передатчик 4, генератор 5 несущей частоты, второй фазоразностный манипулятор 6, . сумматор 7 по модулю два и блок 8 синхронизации, на приемной стороне— приемник 9, два идентичных канала

10 обработки сигналов, состоящие каждый из фазового детектора 11, линии

12 задержки и блока 13 выбора минимума, многоканальный коммутатор 14, 25 первое запоминающее устройство (ЗУ)

15, дешифратор 16, ключ 17, регистр

18 сдвига, сумматор 19 по модулю два, коммутатор 20, первый декодер 21, блок 22 синхронизации, первый умножи- 30 тель 23 частоты на два, фазовый детектор 24, второе ЗУ 25„второй декодер 26, первый 27 и второй 28 блоки задержки, второй умножитель 29 часто- ты на два, фазовращат ель 30, а передатчик 4 и приемник 9 соединены через линию 31 связи.

Устройство работает следующим образом. !

На передающей стороне информационный сигнал источника 1 сообщений, состоящий из символов "1" и "0" длительности Т (фиг, 2а), определяемой частотой импульсов на тактовом выходе блока 8 синхронизации (фиг, 2б), представляется в виде пачек, состоящих из К символов (К 4), например из четного числа К = 4 символов (фиг.

2а), и поступает на К-разрядный регистр 2 сдвига, а после задержки в нем (фиг. 2в) — на вход фазоразностного манипулятора 3. Входы сумматора

7 по модулю два подключены к выходам четных разрядов регистра 2 (к выходам

55 нечетных разрядов при нечетном К) .

Выходные. символы сумматора 7 формируются в моменты, определяемые импульсами на выходе синхронизации блока 8 (фиг. 2г) с тактовой частотой

F/К, и используются для манипуляции по фазе (на 0,90 ) несущего колебания генератора 5 в манипуляторе 6. Манипуляция осуществляется так, что при поступлении символа "1" с выхода сумматора 7 на вход манипулятора 6, начальная фаза изменяется на величину

+90 или -90 относительно значения о а фазы на предыдущем тактовом интервале, а при поступлении символа "0" сохраняет свое значение. В результате этого она может принимать два значения: о

0 и 90 . Далее сигнал с выхода манипулятора 6 манипулируется по фазе (на О, 180 ) выходным сигналом регистра 2 с тактовой частотой F в фазоразностном манипуляторе 3. В результате в сигнал вводится основная информация о передаваемых символах источника 1 сообщений с частотой F (фиг. 2в) и дополнительная информация о четности или нечетности числа символов "1 на четных или нечетных позициях пачки с частотой Г/К (фиг. 2д) . В передатчике 4 сигнал усиливается, переносится в нужный диапазон частот и передается по линии связи.

На приемной стороне информационный сигнал с выхода приемника 9 поступает на информационные входы двух каналов

10 обработки сигналов, отличающихся сигналами, поступающими на их сигнальные входы. На сигнальный вход первого канала 10 подается несущая частота с первого выхода блока 22 синхронизации непосредственно, а на сигнальный вход второго канала 10 — со сдвигом на.

90 чер ез фаз овр ащат ель 30.

Таким образом, при поступлении очередной пачки информационных сигналов длительности КТ правильное фазовое детектирование сигналов в пачке осуществляется только в одном из каналов (фазовый детектор 11). Временное положение символов на выходах фазовых детекторов 11 показано на фиг. 2е.

Определение номера такого канала производится по результатам фазового детектирования сигнала в фазовом детекторе 24. Удвоенный по частоте в умножителе 23 информационный, сигнал сравнивается в фазовом детекторе с удвоенной по частоте в умножителе 29 несущей. Если. на интервале времени КТ фазы этих сигналов совпадают, то на выходе фазового детектора 24 в момен15523 ты действия импульсов на третьем выходе блока 2 2 синхр они з ации (фиг . 2г ) будет сформирован сигнал положительной полярности,в противном случае— отрицательной полярности. Положительность сигнала на выходе фазового детектора 24 свидетельствует о правильности детектирования К символов основной информации в первом канале

10 обработки сигналов.

Выходной сигнал фазового детектора 24 фиксируется на время КТ в ЗУ

25 (фиг. 2ж) и подключает к выходам многоканального коммутатора 14 и коммутатора 20 соответственно сигнальные

50 и информационный (фиг. 2з) выходы нужного канала.

По этому сигналу осуществляется декодирование дополнительной информации с тактовой частотой F/К в декодере 26 (фиг. 2ж) . При этом, если полярности этого сигнала на смежных интервалах времени, равных КТ, одинаковы, то на выходе декодера 26 формируется символ "0", а если противоположны — символ "1". Эта информация задерживается на время Т в блоке 27 задержки (фиг. 2и), тактируемом импульсами с второго выхода блока 22 (фиг. 2б), и поступает на один из сигнальных входов сумматора 19 по модулю два. Линия 12 задержки и блок

13 выбора минимума в каналах 10, выходы которых подключены к входам коммутаторов 14 и 20, а также блоки 1519 предназначены для обнаружения и исправления определенных ошибок,возникающих на выходе фазового детектора 11 (и, следовательно, декодера

21) при воздействии помех.

Обнаружение ошибок осуществляется следующим образом. Выходные сигналы декодера 21 (фиг. 2з) поступают на (К + 1)- разрядный регистр 18, тактируемый импульсами с второго выхода блока 22 синхронизации. Выходы четных (нечетных при нечетном К) разрядов регистра 18 подключены к соответствующим сигнальным входам сумматора

19 по модулю двя. Если число символов "1" на всех его сигнальных входах в момент действия импульса на третьем выходе блока 22 (фиг. 2г) оказывается нечетным, то на его выходе (входе ключа 17) формируется импульс, свидетельствующий о наличии ошибки при детектировании пачки, состоящей из К символов. В момент действия импульса

94 6 на выходе блока 28 задержки (фиг,2к) в блоке 13 выбора минимума осуществляется выбор наименьшего (по абсолютному уровню) из К сигналов, действующих на соседних тактовых интервалах (например, i-го сигнала, i=1,2,...,К).

Номер этого сигнала запоминается на время, равное КТ, в ЗУ 15, а в дешифраторе 16 на двух из общего числа (К + 1) выходов формируются сигналы, которые через ключ 17 изменяют состояния i-ro и (i+1)-ro разрядов регистра

18 на противоположные. По шине регистр 18 — ключ 17, содержащей (К+1) каналов, на ключ 17 поступает информация об исходных состояниях разрядов регистра. Полученные на.выходе регистра 18 символы (фиг ° 2л) являются выходным сигналом устройства.

Формула изобретения

Устройство для передачи и приема дискретных сообщений, содержащее на передающей стороне источник сообщений, последовательно соединенные первый фазоразностный манипулятор и передатчик, последовательно соединенные генератор несущей частоты и блок синхронизации, тактовый выход которого подключен к тактовым входам источника сообщений, первого фазоразностного манипулятора и передатчика, а на приемной стороне — последовательно соединенные приемник и первый фазовый детектор, первый декодер и блок синхронизации, первьпЪ выход которого соединен с сигнальным входом первого фазового детЕктора, второй его выход— с тактовыми входами первого фазового детектора и первого дЕкодера, а выход сиихронизации приемника подключен к входу блока синхронизации, о т л ич а ю щ е е с я тем, что, с целью повьппения помехоустойчивости, введены на передающей стороне последовательно соединенные регистр сдвига, сумматор по модулю два и второй фазораэностный манипулятор, выход которого подключен к сигнальному входу первого фазоразностного манипулятора, выход источника сообщений соединен с информационным входом регистра сдвига, второй выход которого подключен к информационному входу первого фазоразностного манипулятора, тактовый выход блока синхронизации соединен с тактовым входом регистра сдвига, вы1552394

Ход rенератора несущей частоты подключен к второму входу второго фазоразностного манипулятора, выход синхронизации блока синхронизации сое5 динен с входами синхронизации сумматора по модулю два, второго фазоразностного манипулятора и передатчика, а на приемной стороне введены последовательно соединенные многоканаль- 1Q

Вый коммутатор, первое запоминающее устройство, дешифратор, ключ, регистр сдвига и сумматор по модулю два, коммутаторр, фаз овр ащат ель, п осл едов ательно соединенные первый умножитель cñ частоты на два, второй фазовый детектор, второе запоминающее устройстso второй декодер и первый блок за-Цержки, второй блок задержки., второй умножитель частоты на два, последова- Zg тельно соединенные линия задержки и блок выбора минимума, выход первого фазового детектора подключен к информационному входу линии задержки, тактовые входы линии задержки и блока выбора минимума соединены с тактовым входом первого фазового детектора, причем первый фазовый детектор, линия задержки и блок выбора минимума являются первым каналом обработки сиг — 30 налов, входом синхронизации, тактовым, сигнальным и информационным входами которого являются соответственно вход синхронизации блока выбора минимума, тактовые входы фазового детектора, линии задержки и блока выбора минимума, сигнальный вход первого Фазового детектора и информационный вход первого фазового детектора, а информационным и сигнальными выходами которого 4Q являются соответственно второй выход

У линии задержки и выходы блока выбора минимума, а также второй канал обработки сигналов, идентичный первому, информационные выходы первого и вто- 45 рого каналов обработки сигналов соечинены соответственно с первым и вторым входами коммутатора, выход которого подключен к информационному входу первого декодера, выход первого декодера соединен с входом регистра сдвига, управляющие выходы которого подключены к управляюшим входам ключа, второй выход бпока синхронизации соединен с тактовыми входами первого блока задержки, второго канала обработки сигналов и регистра сдвига, второй выход которого является информационным выходом устройства, первый выход блока синхронизапии соединен с входом фазовращателя, выход которого подключен к сигнальному входу второго канала обработки сигналов. и с входом второго умножителя частоты на два, выход которого подключен к второму входу второго фазового детектора, выход приемника соединен с информационным входом второго канала обработки сигналов и с входом первого умножителя частоты на два, выход второго запоминающего устройства подключен к входу многоканального коммутатора и к третьему входу коммутатора, выход первого блока задержки соединен с вторым входом сумматора по модулю два, выход которого подключен к второму входу ключа, а третий выход блока синхронизации соединен с тактовыми входами. сумматора по модулю два, второго фазового детектора, второго запоминающего устройства и второго декодера и с входом второго бло<а задержки, выход которого подключен к второму входу первого запоминающего устройства и к входам синхронизации первого и второго каналов обработки сигналов, сигнальные выходы кото--. рых соединены с соответствующими сигнальными входами многоканального коммут".òîðà.

1552394

1 2 Э 9 5 б 7

I

Составитель И. Котиков

Редактор Н. Тупица Техред Л. Сердюкова Корректор Т.Малец

Заказ 341 Тираж 523 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент"„ г. Ужгород, ул. Гагарина, 101