Устройство для демодуляции цифровых сигналов с частотной модуляцией

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике. Цель изобретения - повышение точности демодуляции. Устройство содержит регистры 3 и 4 сдвига, блок 8 умножения на два, сумматор 9, блок деления 16 и декодирующий блок 17. Цель достигается введением управляемого ключа 1, АЦП 2, регистров 5 и 6 сдвига, генератор 7 импульсов, сумматора 10, блока 11 умножения на два, блоков запрета 12 и 13, блока 14 определения модуля числа и цифрового компаратора 15, с помощью которых исключаются из дальнейшей обработки аномальные результаты демодуляции, возникающие при малых значениях суммы кодов, находящихся в регистрах 4 и 5. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

ns,SU

А1

Р1)5 Н 04 L 27/14

1 ъ L kj+ Я

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTHPblTHRM

ПРИ ГКНТ СССР

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ (21) 4422057/24-09

{22) 10.05.88 (46) 23.03.90. Бюл. М 11 (72) С.В.Васильев, С.А.Доронин, ф.Н.Дубовик и Л.П.Котенко (53) 621.396.6(088.8) (56) Хохлов Б.И. Декодирующие устройства цветных телевизоров. — M. Радио и связь, 1987, с. 96, рис. 255.. (54) УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ЦИФРОВЫХ СИГНАЛОВ С ЧАСТОТНОЙ МОДУЛЯЦИЕЙ (57) Изобретение относится к радиотехнике. Цель изобретения — повышение

2. точности демодуляции. Устр-ао с одержит регистры 3 и 4 сдвига, блок 8 умножения на два, сумматор 9, блок 16 деления и декодирующий блок 17. Цель достигается введением управляемого ключа 1, АЦП 2, регистров 5 и 6 сдвига, генератора 7 импульсов, сумматора

10, блока 11 умножения на два, блоков

12 и 13 запрета, бпока 14 определения модуля числа и цифрового компаратора

15, с помощью которых исключаются из дальнейшей обработки аномальные результаты демодуляции, возникающие при малых значениях суммы кодов, находящихся в регистрах 4 и 5. 1 ил.

1552397

Изобретение относится к радиотехнике и может бьггь использовано в приемниках дискретной информации.

Цель изобретения — повьш|ение точнос5 ти демодуляции.

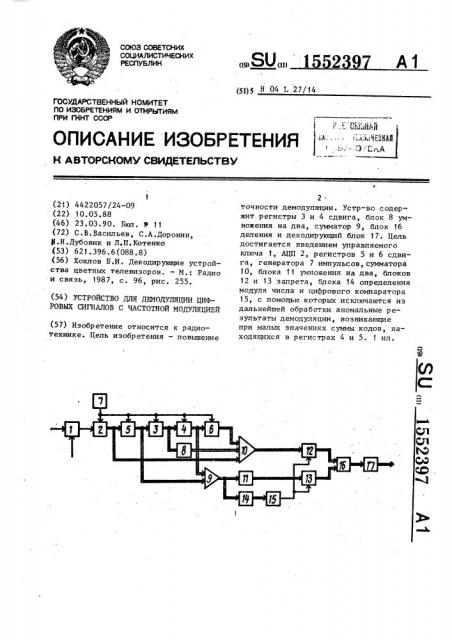

На чертеже изображена структурная электрическая схема предлагаемого устройства.

Устройство для демодуляции цифровых сигналов с частотной модуляцией содержит управляемьпг ключ 1, аналогоцифровой преобразователь 2 (АЦП), первьпг» второй, третий и четвертый регистры 3-6 сдвига, генератор 7 им- 15 пульсов, первый блок 8 умножения на два, первый и второй сумматоры 9 и

10, второй блок 11 умножения на два, первый и второй блоки 12 и 13 запрета, блок 14 определения модуля числа, цифровой компаратор 15» блок 16 деления и декодируюций блок 17.

Устройство работает следующим образом.

Частота опроса устанавливается рав-25 ной 4f„. При наличии на управляющем входе управляемого ключа 1 разрешающего потенциала, выдаваемого устройством синхронизации, входной сигнал

U(t) через открьггый управляемый ключ Зп

1. поступает на вход АЦП 2, которьп" производит с периодом Т преобразование мгновенных значений напряжения входного сигнала U(t.„ ) = v, в параллельный цифровой код. Таким образом, в установившемся режиме в регистре

6 сдвига находится код v<» в регистре 4 сдвига — код ч„, в регистре 3 сдвига — код v, в регистре 5 сдвига код ч4 и на выходе АЦП 2 — код v>, 40 где »» » <2» v) » >4 и vs коды соот

» ветствующие мгновенным значениям входного напряжения U(t) в моменты времени t t<, t>, t< и t s соответствен— но. Содержимое четвертого регистра 45

6 сдвига, содержимое регистра 3 сдвига после умножения на два в блоке 8 умножения и код v с выхода АЦЛ 2 суммируются в сумматоре 10 и резуль— тирующий код через блок 12 запрета 50 поступает на первый вход блока 16 деления, Содержимое регистра 5 сдвига и содержимое регистра 4 сдвига суммируются в сумматоре 9 и результат после умножения на два в блоке 11 55 умножения через блок 13 запрета поступает на второй вход блока 16 деле— ния. Одновременно с этим код, соответствующий v + .», с выхода сумматора 9 поступает в блок l4 определения модуля числа и после него и циф-. ровой компаратор 15, где код (vz+v ) сравнивается с заранее установленным кодом, соответствующим порогу h, Порог h выбираетс.я из условия обеспечения заданной точности демодуляции.

ЕсJIH (vg + vq (ll » To цифровой KOMпаратор 15 выдает высокий потенциал на блоки 12 и 13 запрета, которые в этом случае пропускают коды, соответствующие v< + 2v + v5 и 2(v + v< ) на входы блока 16 деления. Код, соответствующий результату деления, поступает в декодирующий блок 17, на выходе которого появляется код значения частоты демодулируемого сигнала, определяемой в соответствии с алгоритмом

1 v +2v>+vs — — — --arccos

27 Та 2(ч +ч+ )

Если же условие (v + v+ ) h не выполняется, то цифровой компаратор

15 выдает на управляющие вторые входы блоков 12 и 13 запрета низкий потенциал. В этом случае результаты суммирования, соответствующие данному такту опроса, через блоки 12 и 13 запрета не проходят, а на их выходах сохраняется предыдущий код. Следовательно, и на выходе устройства код частоты f не изменится. Такой эффект позволяет исключить из дальнейшей обработки аномальные результаты демодуляции, возникающие при малых значениях (v<+v+);

Поскольку данное устройство является линейной цифровой схемой с суммарной задержкой, определяемой быстродействием элементной базы, то объем информации с выхода устройства необходимо осуществлять в моменты времени, сдвинутые относительно тактовых импульсов на время, не меньшее суммарной задержки.

Процесс съема выходной информации в алгоритм фунционирования предлагаемого устройства не входит.

Формула изобретения

Устройство .для демодуляции цифровых сигналов с частотной модуляцией, содержащее первый регистр сдвига, выход которого соединен с входом первого блока умножения на два и с сиг1552397 6 дом четвертого регистра сдвига и с вторым входом второго регистра сдви— га, выход которого подключен к первому входу четвертого регистра сдвига, выход которого подключен к первому входу четвертого регистра сдвига, выход котброго подключен к третьему входу второго сумматора, выход которого соединен с первым входом первого блока запрета, выход которого подключен к первому входу блока деления, второй вход которого подключен к выходу второго блока запрета, первь i вход которого соединен с выходом второго блока умножения на два. вход которого подключен к выходу первого сумматора и к входу блока определения модуля числа, выход которого соединен с входом цифрового компаратора, выход которого соединен с вторыми входами первого и второго блоков запрета, при этом первый вход управляемого ключа является информационным входом устройства, синхрони.зирующим входом которого является второй вход управляемого ключа, а выход декодирующего блока является выходом устройства.

/ нальным входом второго регистра сдвига, выход которого соединен с первым входом первого сумматора, второй вход которого подключен к первому входу

5 первого регистра сдвига, блок деления, выход которого подключен к входу декодирующего блока, о т л и ч а ю— щ е е с я тем, что, с целью повышения точности демодуляции, введены 10 два блока запрета, цифровой компаратор, блок определения модуля числа, второй блок умножения на два, второй сумматор, третий и четвертый регистры сдвига, аналого- цифровой преобразова- 1g тель, генератор импульсов и управляемый ключ, выход которого соединен с первым входом аналого-цифрового преобразователя, выход которого соединен с первым входом третьего регистра 20 сдвига и с первым входом второго сумматора, второй вход которого подключен к выходу первого блока умножения на два, выход третьего регистра сдвига соединен с первым входом первого 25 регистра сдвига, второй вход которого соединен с выходом генератора импульсов, с вторым входом аналого-цифрового преобразователя, с вторым входом третьего регистра сдвига, с вторым вхо- 30

Составитель О. Гелляр

РедактоР Е.Папп ТехРед Л.Сердюкова Корректор С. Черни

Производственно-издательский комбинат "Патент", r Óæroðîä, ул. Гагарина,.01

Заказ 341 Тираж 526 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР >

113035, Москва, Ж-35, Раушская наб., д. 4/5