Устройство для возведения в квадрат

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для интерационного формирования квадратов чисел Фибоначчи в специализированных вычислителях, работающих в 1 коде Фибоначчи. Целью изобретения является расширение области применения за счет возведения в квадрат чисел Фабоначчи. Устройство содержит схему 1 сравнения, счетный триггер 2, регистр 3 сдвига, элемент И 4. На входе 6 устройства задается маркерный код текущего значения аргумента. При запуске устройства по входу 7 импульсами тактовой частоты со входа 8 в регистре 3 формируется простейший равновесный код вида ...101010. Фиксация результата на выходе 9 происходит при достижении старшей единицы равновесного кода маркера аргумента на входе 6. Результат получается в 1 коде Фибоначчи путем прореживания простейшего равновесного кода кодом единицы ...0001. 2 ил., 1 табл.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

ИЕ ИЗОБРЕТЕНИЛ, -: -=

ПРИ ГННТ СССР

ОПИСАН

И А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОЧНРЫТИЯМ (21) 4431443/24-24 (22) 27.05 ° 88 (46) 30.03.90. Бюл. М 12 (71) Специальное конструкторско-технологическое бюро "Модуль" Винницкого политехнического института (72) И.В.Матюшенко (53) 681.325 (088.8) (56) Авторское свидетельство СССР l345190, кл. Г 06 F 7/49, 1986.

Авторское свидетельство СССР

< 607215, кл. С 06 7/552, 1976, (54) УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В

КВАДРАТ (57) Изобретение относится к вычислительной технике и предназначено для итерационного формирования квадратов чисел Фибоначчи в специализированных вычислителях, работающих в 1 коде

Изобретение относится к вычислительной технике и может быть использовано для итерационного формирования квадратов чисел Фибоначчи в специализированных вычислителях, работающих в 1-коде Фибоначчи.

Целью изобретения является расширение области применения за счет возведения в квадрат чисел Фибоначчи.

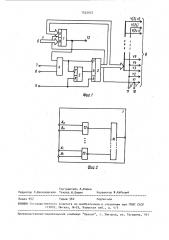

На фиг.1 представлена схема устройства для возведения в квадрат; на фиг.2 — схема схемы сравнения.

Устройство (фиг.1) содержит схему

1 сравнения, счетный триггер 2, регистр 3 сдвига, элемент И 4, вход 5 начальной установки устройства, информационный вход 6 устройства, вход

7 запуска устройства, тактовый вход

„„SU„„1553972 А 1 (g1)S (; 06 1 7/49 7/552

2 фибоначчи. Целью изобретения является расширение области применения эа счет возведения в квадрат чисел Фибоначчи.

Устройство содержит схему 1 сравнения, счетный триггер 2, регистр 3 сдвига, элемент И 4. На входе 6 устройства задается маркерный код текущего значения аргумента. При запуске устройства по входу 7 импульсами тактовой частоты с входа 8 в регистре 3 формируется простейший равновесный код вида ...101010. Фиксация результата на выходе 9 происходит при достижении старшей единицы равновесного кода маркера аргумента на входе 6.

Результат получается в 1 коде Фибоначчи путем прореживания простейшего Ж равновесного кода кодом единицы ...0001. 2 ил., 1 табл.

С::

8 устройства, выход 9 результата устройства, вход 10 логической единицы устройства, вход 11 логического нуля устройства, выход 12 готовности устройства.

Схема 1 сравнения (фиг.2) содеджит группу элементов И-НЕ 13 и элемент

И 14, выход которого является выходом схемы 1 сравнения, его входы подключены к выходам элементов И-НЕ 13, первые и вторые входы которых образуют соответственно первый и второй входы схемы 1 сравнения.

Устройство (фиг.1) выполняет возведения в квадрат чисел Фибоначчи, равных значениям весов 1-кода Фибоначчи.

1553972

Порядковый номер

2345

Вес числа

1235813213455 89144

4

64

169

1 0 0 0 О 0

1 0 1 О 0 0

1 0 1 0 0 0

0 0 0

О 0 0

С 0 О

1 0 О

0 0 1

1. 0 О

0 0

С 0

0 0

С 0 .0 0

О 1

?

5

13

Устройство работает следующим обрс) зом.

В исходном состоянии на входе 7 запуска устройства присутствует уровень логического нуля, блокирующий пОступление импульсов тактовой частоTtil с входа 8 на входы синхронизации триггера 2 и регистра 3. По входу 5 у тройства осуществляется предварит льная установка в нулевое состояние т иггера 2 и регистра 3 одиночным и пульсом положительной полярности.

На входе 6 устройства задается маркерный код текущего значения аргум нта (позиционный код числа Фибоначч ). При этом на выходе схемы 1 сравн ния появляется уровень логической е иницы, сигнализирующий о неготовности результата к считыванию с выход 9 и разрешарв ий запуск устройства.

При подаче уровня логической един цы на вход 7 запуска устройства ч рез элемент И 4 на входы синхрониз ции триггера 2 и регистра 3 поступ.ют импульсы тактовой частоты с входд 8 устройства. При этом в регистре

3 происходит формирование простейшего равновесного кода вида ...101010.

При достижении в процессе сдвига с "аршей единицей равновесного кода а данного на входе 6 маркера аргумент на выходе 12 готовности устройства появляется нулевой потенциал, блокирующий поступление импульсов. тактовой ч стоты, тем самым фиксируя результат н выходе 9 устройства и сигнализируя о готовности его к считыванию.

Указанный алгоритм работы устройс1 ва вытекает из анализа таблицы кодов квадратов чисел Фибоначчи в р=1 кода Фибоначчи.

5 !

О

Фоpмула изобретения

Устройство для возведения в квадрат, содержащее схему сравнения, счетный триггер и элемент И, причем информационный вход устройства соединен с первым входом схемы сравнения, выход которой соединен с первым входом элемента И, вход начальной установки устройства соединен с входом установки в "О счетного триггера, о т л и ч а ю щ ес е с я тем, что, с целью расширения области применения за счет возведения в квадрат чисел

Фибоначчи, оно содержит регистр сдвига, причем вход запуска и тактовый вход. устройства соединены соответственно с вторым и третьим входами элемента И, выход которого соединен со счетным входом счетного триггера и с тактовым входом регистра сдвига, информационный вход и вход установки в 0" которого соединены соответственно с. выходом счетного триггера и с входом начальной установки устройства, выход готовности которого сое" динен с выходом схемы сравнения, вход логической единицы, устройства соединен с входом младшего разряда второго входа схемы сравнения и является выходом младшего разряда выхода результата устройства, выходы разрядов регистра сдвига соединены соответственно с входами старших разрядов второго входа схемы сравнения и являются выходами старших нечетных разрядов выхода результата устройства, выходы четных разрядов выхода результата которого соединены с входом логического нуля устройства.

1553972

7f Ю

Составитель А.Клюев

Редактор Л.Веселовская Техред И.Дидик Корректор В.Кабаций

Тираж 562

Подписное

Заказ 457

ВНИИПИ Государственного комитета по изобретениям и открьггиям при ГКНТ СССР

113035, Mocêâà, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, t 01