Устройство постоянной памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в цифровых вычислительных системах. Цель изобретения - повышение быстродействия за счет сокращения времени выборки информации. Поставленная цель достигается тем, что в устройство введены регистр 5, группу из а ключей 6, где а - максимальное число массивов постоянной памяти, блок 7 импульсного питания, первый дешифратор 8, счетчик 9 и второй дешифратор 10. 1 ил.

СОЮЗ СОВЕТСНИК

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

Рфуыгг уюрайcmй

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЦТИЯМ

ПРИ ГННТ СССР. (21) 4331592/24-24

1 (22) 23 ° 11 ° 87 (46) 30. 03. 90. Бюл. N 12 (72) В.И. Ким, 10.М. Дале цкий, А.Я.Прохоренко, В.В.Кирпиченко и А.И.Мамонько (53) 681.325 (088.8) (56) Шевкопляс Б.B. Микропроцессорные структуры. Инженерные решения. — M.:

Радио и связь, 1986, с. 44.

Патент Великобритании М 201905, кл. Г 06 F 13/00, опублик. 1982.

„.SU,, 1553983 А1

{g1)S С 06 F 13/00, С 11 С 17/00

2 (54) УСТРОЙСТВО ПОСТОЯННОЙ ПАМЯТИ (57) Изобретение относится к автоматике и вычислительной технике и предназначено для использования в цифровых вычислительных системах. Цель изобретения - повышение быстродейст- . вия за счет сокращения времени выборки информации. Поставленная цель достигается тем, что в устройство введены регистр 5, группа из а, где а максимальное число массивов постоянной памяти, ключей 6, блок 7 импульсного питания, первый дешифратор 8, счетчик 9 и второй дешифратор 10. . 1 ил.

1553983

3

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в цифровых

Вычислительных системах.

Целью изобретения является повыше5 ние быстродействия устройства за счет

Сокращения времени выборки информации.

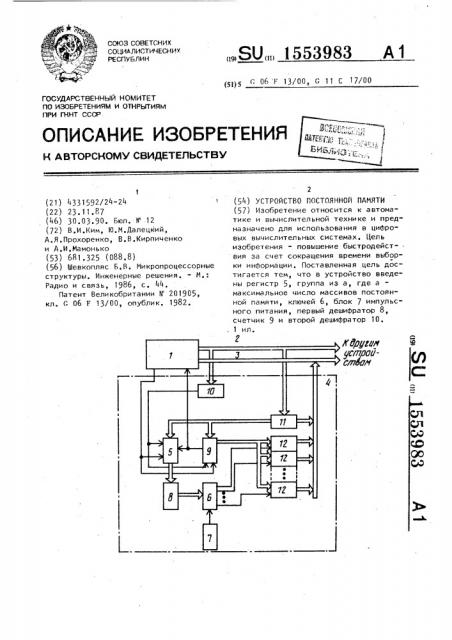

На чертеже приведена схема устройства. !

О

На чертеже обозначены: процессор шина 2.адреса, шина 3 данных и устройство 4 постоянной памяти, котоРое содержит регистр 5„ группу 6

Ключей, блок 7 импульсного питания, Первый дешифратор 8, счетчик 9, втоой дешифратор 10, блок 11 постоянной амяти и группу блоков 12 постоянной

Памяти, Процессор 1 является основным активным устройством вычислительной системы и предназначен для обработки йнформации, поступающей по шине 3

«!анных, и управления пассивными устРойствами с помощью шины 2 адреса и сигналов управления.

Пина 2 адреса предназначена для передачи кода адреса, идентифицирующего устройство или ячейку памяти, к которой обращается процессор 1.

Шина 3 данных предназначена для обмена информацией между процессором 1 и пассивными устройствами °

Регистр 5 предназначен для фиксации адреса блока 12 постоянной памяти

35 группы, к которому произошло обращение.

Ключи 6 группы предназначены для подачи питания на один из блоков 12 постоянной памяти гРуппы, к котоРому 40 произошло обращение.

Блок 7 импульсного питания предназначен для питания одного из блоков

12 постоянной памяти группы °

Дешифратор 8 пРедназначен для де- 4> шифрации адреса блока 12 постоянной памяти группы, к которому произошло обращение.

Счетчик 9 предназначен для формирования текущего адреса внутри адресного пространства блока 12 постоянной памяти группы, а также для формирования сигнала, который приводит s исходное состояние регистр 5 и сообщает процессору 1 об окончании массива.

Дешифратор 10 предназначен для

55 дешифра ции адреса, по которому процессор 1 может извлекать информацию из группы блоков 12 постоянной памяти, Блок 11 постоянной памяти является каталогом постоянной памяти и предназначен для хранения и выдачи на шину 3 данных имени массива, а регистр 5 — кода адреса блока 12 постоянной памяти группы, а в счетчик 9 кода длины массива.

Група блоков 12 постоянной памяти предназначена для хранения и выдачи на шину 3 данных массивов информации.

Устройство работает следующим образом.

В исходн м состоянии на выходе дешифратора 10 сформирован потенциал логического нупя, разрешающий запись в регистр 5 и загрузку счетчика 9.

Питание на блок 11 постоянной памяти подается постоянно. Сигнал "Чтение, поступающий на счетный вход счетчика

9, не влияет на состояние счетчика 9, так как он блокирован сигналом разрешения загрузки, поступающим с выхода дешифратора 10. Вывод дешифратора 8, активиэирующийся нулевым входным кодом, не используется, следовательно, ни один ключ 6 группы ключей не открыт и питание от блока 7 питания не поступает ни на один из блоков 12.

Адреса блока 11 находятся в адресном пространстве процессора 1. Слово, извлекаемое из блока 11 при каждом обращении процессора 1, состоит из двух полей: поля имени массива разрядностью k и поля адреса разрядностью n+m, причем младшие и разрядов адреса определяют размер массива, а старшие m разрядов - адрес блока 12 в группе. Таким образом, максимальное число блоков 12 определяется величиной

Ч = 2 - 1 (так как выход первого дешифратора 8, возбуждаемый нулевым входным кодом, не используется), каждый из блоков

12 имеет максимальный объем, определяемый величиной и 2 — 2 а общий объем памяти группы блоков 12 определяется величиной

V=V +v = (2-1) 2

1 2

Разрядность поля имени блока 11 и выходных слов блоков 12 не может превышать разрядности шины 3 данных.

При необходимости извлечения массива информации под определенным именем процессор 1 последовательно читает слова иэ блока 11, причем поле имени поступает через шину 3 данных

1553983

10 в процессор 1 для анализа, а поле адреса записывается по сигналу "Чтение" в регистр 5 и в счетчик 9. Код, поступивший с выходов регистра 5 на входы дешифратора 8, активизирует один из его выходов. Сигнал с выхода дешифратора 8 включает один из ключей 6 группы и питание от блока 7 питания подается на соответствующий блок 12.

Если анализируемое имя массива не совпадает с требуемым, то процессор 1 переходит к чтению следующего имени из блока 11, а информация второго поля переписывается в регистр 5 и счетчик 9.

Если анализируемое имя совпадает с требуемым, то процесор 1 устанавливает на шине 2 адрес, активизирую" щий выход дешифратора 10. Потенциал логической единицы, сформированный на выходе дешифратора 10, запрещает перезапись в регистр 5 и переводит счетчик 9 в режим счета К этому вре" мени на информационных выходах счетчика будет сформирован адрес начальной ячейки массива информации, а через ключи б группы будет подано питание на соответствующий блок 12 с блока 7 питания. Таким образом, из расчета времени выборки информации можно исключить время задержки схемы импульсного питания и время переходного процесса, так как эти процессы закончились за время выборки и анализа процессором 1 имени массива. Формируя сигналы "Чтение" процессор I последовательно выбирает из соответствующего блока 12 массив, причем по окончании каждого сигнала "Чтение" счетчик 9 меняет свое состояние, формируя адрес следующей ячейки массива (блока 12) ° Таким образом, сокращается время выборки адреса, так как к моменту формирования процессо" ром 1 следующего сигнала "Чтение" адрес выбираемой ячейки блока 12 будет уже сформирован ° . По окончании массива (обнуление счетчика 9) сигнал переноса счетчика

9 поступает на вход сброса регистра

5, выключая тем самым питание выбранного блока 12, и поступает на вход запроса прерывания процессора 1, сообщая тем самым об окончании массива.

В устройстве реализуется опережающая подача питания на выбранный блок постоянной памяти, сокращается время обращения к постоянной памяти, так как время задержки схемы импульсного питания и переходный процесс в блоках постоянной памяти заканчиваются к мо" менту обращения процессора к блокам постоянной памяти.

Формула изобретения

Устройство постоянной памяти, содержащее регистр, группу из ц ключей, где a -. максимальное число массивов постоянной памяти, блок постоянной памяти, группу из а блоков постоянной памяти и блок импульсного питания, причем выход блока импульсного питания подключен к первым входам ключей с первого по ц-й группы, выходы которых подключены соответственно к входам питания блоков постоянной памяти с первого по q-й группы, .адресный вход устройства подключен к адресному входу блока постоянной памяти, выход блока постоянной памяти и выходы блоков постоянной памяти с первого по -й группы объединены и подключены к информационному выходу устройства, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия устройства за счет сокращения времени выборки информации, устройство содержит счетчик, первый и второй дешифраторы, причем управляющий вход устройства подключен к входу считывания регистра и к счетному входу счетчика, информационный выход которого подключен к адресным входам блоков постоянной памяти группы, выходы бло" ка постоянной памяти подключены к информационным входам счетчика и к информационным входам регистра, выходы которого подключены к входам первого дешифратора, выходы с первого по а -й которого подключены соответственно к вторым входам ключей с первого по а-й группы, адресный .вход устройства подключен к входу второго дешифратора,. выход которого подключен к входу записи регистра и к входу режима счетчика, выход переполнения которого подключен к управляющему входу регистра и к выходу признака окончания выборки устройства.