Оперативное запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и наиболее эффективно может быть использовано при создании оперативных запоминающих устройств в интегральном исполнении. Цель изобретения - повышение достоверности контроля схем коррекции ошибок и повышение быстродействия устройства в режиме самоконтроля. Поставленная цель достигается тем, что в состав устройства введены блок элементов И, элемент НЕ, блок тестирования и новые связи. Это позволяет в режиме самоконтроля проводить независимую проверку работоспособности собственно схем коррекции, а также существенно сокращает время контроля. В предлагаемом устройстве предусмотрено отключение схемы коррекции в случае ее неисправности. 2 ил.

СОЮЗ СОНЕТСНИХ

СОЦИАЛИСТИЧЕСНИ Х

РЕСПУБЛИН (51)5 С 11 С 29 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ Н0ММТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4436738/24-24 (22) 06.06.88 (46) 30.03.90. Бюл. h"- l 2 (7!) Московский. инженерно-физический институт (72) А,С. Березин, В.В.Маринчук, Е.М.Онищенко и С.В.Сушко (53) 681.327.6(088.8) (56) Патент США 4335459, кл. 371-38, 1982.

Авторское свидетельство СССР

N- 1332386, кл. G 11 С 29/00, 1986. (54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ (57) Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и наиболее эффективно может быть использовано

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано при создании оперативных запоминающих устройств в интеrральном исполнении.

Цель изобретения — повышение достоверности контроля схем коррекции ошибок и повышение быстродействия, устройства в режиме самоконтроля.

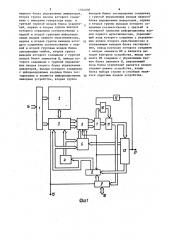

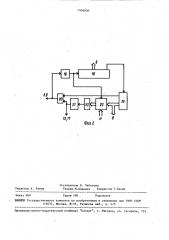

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 — структурная схема блока тестирования для запоминающих устройств со встроенной коррекцией кодом Хемминга.

Устройство содержит блок 1 выборки строки и столбцов, накопитель 2, „„SU„„1554030 А 1 при создании оперативных запоминающих устройств в интегральном исполнении. Цель изобретения — повьппение достоверности контроля схем коррекции ошибок и повьппение быстродействия устройства в режиме самоконтроля.

Поставленная цель достигается тем, что в состав устройства введены блок элементов И, элемент НЕ, блок тестирования и новые связи. Это позволяет в режиме самоконтроля проводить независимую проверку работоспособности собственно схем коррекции, а также существенно сокращает время контроля. В предлагаемом устройстве предусмотрено отключение схемы коррекции в случае ее неисправности.

2 ил.. блок усилителей 3, генератор 4 кода, первый мультиплексор 5, первый блок управляемых инверторов 6, блок 7 локализации ошибок, второй мультиплек,сор 8, блок 9 ввода, вывода, блок элементов И 10, второй блок управляемых инверторов 11, элемент НЕ 12, 4ю блок 13 тестирования, внешние адресные входы 14; вход 1 5 задания режима, информационные входы-выходы 1 6 и выход 17 контроля и отключения схе- мы коррекции 17.

Блок 1 3 тестирования содержит re- - 4 нератор 1 8 тактовых импульсов, тринадцатиразрядный кольцевой регистр

19, элементы ИЛИ 20, триггер 21, элемент ИЛИ 22, схему 23 сравнения и счетчик 24.

l 554030

Устройство работает следующим образом.

Перед началом цикла самоконтроля с помощью внешнего управлявшего сиг5 нала или через специальную схему регистрации включения питания в начальные состояния устанавливаются триггер 21 и счетчик 24 и запускается генератор 18 блока 13 тестирования (схе.10 мы начальной установки не показаны).

Кроме того, в начальное состояние устанавливается и кольцевой регистр

19, причем его первый разряд устанавливается в 1", а остальные двенадцать разрядов (для кода Хемминга (12,8) — ° в "0 . При самоконтроле устройство работает в режиме постоянной выборки. Сигнал уровня "0 на управляющих входах мультиплексоров 5 и 8 обеспечивает прохождение на входы блока 7 локализации ошибок сигналов с инверторов 6, а на входы генератора 4 кода — сигналов тестовой последовательности с восьми младших разря- 25 дов счетчика 24. Таким- образом, в режиме самоконтроля исключается операция записи — считывания в накопитель, что позволяет выделить неисправности собственно схем коррекции и существенно сократить время самоконтроля.

Формирование одиночной ошибки в информационном и контрольном разрядах слова, поступающего в блок 7 локализации ошибки, обеспечивают инверторы 6 при поступлении управляющего сигнала уровня 1 с выхода соответствующего разряда регистра 19.

Исправление этой ошибки осуществляют инверторы 11. Факт восстановления исходного слова регистрирует схема

23 сравнения во время действия импульса генератора 18, в результате чего по заднему фронту этого импуль- 45 са осуществляется сдвиг "1 " в следующий разряд регистра 19.

Переход к новому информационному слову, т.е. переключение счетчика

24, происходит по заднему фронту им50 пульса положитегп ной полярности с выхода тринадцатого разряда регистра

19, т.е. после формирования ошибок последовательно во всех разрядах сло- . ва. Переключение триггера 21 защелки в состояние 1 происходит при обнаев и 55 ружении сохранения ошибки в слове на выходе схем коррекции, а это приводиТ к блокировке в состоянии "0" генератора 18, к формированию сигнала на выходе 17 и к прямому пропусканию (без инвертирования) сигналов блоком инверторов ll, Останов генератора тактовых импульсов генератора

18 происходит также после полного перебора возможных комбинаций информационных слов счетчиком 24, т.е. после появления "1" в его старшем девятом разряде, Цикл самоконтроля при этом завершается и устройство переходит в режим внешних обращений.

В этом случае в режиме считывания информационные сигналы с выходов блока управляемых инверторов передаются через блок ввода-вывода на информационные выходы устройства, а в режиме записи — с информационных входов на входы мультиплексора.

Формула изобретения

Оперативное запоминающее устройство с самоконтролем, содержащее накопитель, блок усилителей, блок выборки строки и столбцов, генератор кода, первый и .второй блоки управляемых инверторов, блок локализации ошибок, первый и второй мультиплексоры, причем первая группа выходов блока выборки строки и столбцов соединена с адресными входами накопителя, информационные входы-выходы которого соединены с информационными входами-выходами блока усилителей, первая группа входов которого соединена с второй группой выходов блока выборки строки и столбцов, первая группа выходов блока локализации ошибок соединена с группой входов второго блока управляемых инверторов, информационные входы первой группы второго мультиплексора являются информационными входами устройства, выходы второго мультиплексора соединены с входами генератора кода, о тл и ч а ю щ е е с я тем, что, с целью повышения доствеорности контроля схем коррекции ошибок, и повышения быстродействия з режиме самоконтроля в устройство введены блок элементов

И, элемент НЕ, блок тестирования, причем первая группа выходов блока тестирования соединена с информационными входами второй группы второго мультиплексора, выходы которого соединены с второй группой входов блока усилителей и с первой группой входов

5 l 554030 6 первого блока управляемых инверторов, выходов блока тестирования соединена вторая группа входов которого соеди- с группой управляющих входов первого иена с выходами генератора кода и блока управляемых инверторов, первая третьей группой входов блока усилите- и вторая группы выходов которого со9 5 лей, первая и вторая группы выходов единены соответственно с третьей и которого соединены соответственно с четвертой группами информационных вхопервой и второй группами информаци- дов первого мультиплексора, управляюонных входов первого мультиплексора, щий вход которого соединен с управляюпервая и вторая группы выходов кото- ip щим входом второго мультиплексора и ррго соединены соответственно с пер- управляющим выходом блока тестирова вой и второй .группами входов блока ния, выход контроля которого соединен локализации ошибок, вторая группа с входом элемента НЕ и является вывыходов которого соединена с группой ходом контроля устройства, выход элевходов блока элементов И, выходы ко- 15 мента НЕ соединен с управляющим вхоторого соединены с группой управляю- жом блока элемента И, управляющий щих входов второго блока управляемых вход блока усилителей является входом инверторов, выходы которого соединены задания режима устройства, входы с информационными входами блока тес- блока выбора строки и столбцов являтирования и являются информационными gp ются адресным входом устройства. выходами устройства, вторая группа! 554030

Составитель В. Чеботова

Техред М.Ходанич Корректор Т.Палий

Редактор A. Ревин

Тирая 484 .Подписное

Заказ 460

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101