Цифровой фильтр

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для фильтрации результатов измерения физического параметра. Цель изобретения - повышение точности фильтрации путем учета при обработке априорно известного математического ожидания - достигается введением сумматора 10, синусных преобразователей 11, 18, интегратора 12, двух дополнительных косинусных преобразователей 24, 20 и весового множителя 25. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

-EI, 0I3 H!

ОПИСЛНИК ИЗОБРКТКНиЯ

Н АBTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTHPblTHRM

ПРИ ГКНТ СССР (21) 4407221/24-09 (22) 08.04.88 (46) 07.04.90. Бюл. и 13 (72) А.С.Бурый, В.В.Васильев и В.В.Ушаков (53) 621.396.6 (088.8) (56) Авторское свидетельство СССР

Ф 1385265, кл. Н 03 Н 21/00, 1987. (54) ЦИФРОВОЙ ФИЛЬТР (57) Изобретение относится к вычисÄÄSUÄÄ 1555 8 А1 (51) 5 Н 03 Н 21/00

2 лительной технике и может быть использовано для фильтрации результатов измерения физического параметра. Цель изобретения — повышение-точности фильтрации путем учета при обработке априорно известного математического ожидания — достигается введением сумматора 10, синусных преобразователей

11, 18, интегратора 12, двух дополнительных косинусных преобразователей 24, 20 и весового множителя 25.

1 ил.

1555828

Э < (8„)

+—

2 Ге „ (3) (4) где В

w = )((Z) 32K(g

- () + — — — -6 т Я 82 (5) 3q (я+) — — -" — = mcos(g ) .

Яg»( (6) Учитывая выражения (1) — (4), цифровой фильтр работает следуюцим образом.

На первый вход вычитателя 1 поступает входной сигнал Z(t) в виде параллельного двоичного кода, а на второй вход - сигнал (g(g) с выхода второго синусного преобразователя 9, на вход которого сигнал mg подается с входа второго весового множителя 8, »»оэффициент умножения и на которы»» как и на весовые множители 6, 23 и

25, поступает с третьего выхода блока где g — - вектор состояния системы размерности (r)(1);

: 45

y(t). - вектор наблюдений (измерений) .

Измерения сопровождаются погрешностями п(), которые аддитивны по отношению к y(t): 50 (2) Z(t) = у() + n(t), Изобретение относится к вычислительной технике и может быть использовано для Фильтрации результатов измерения физического параметра.

Цель изобретения — повышение точности фильтрации.

Поставленная цель достигается за счет использования при обработке априорно известного математического ожидания значения входного сигнала.

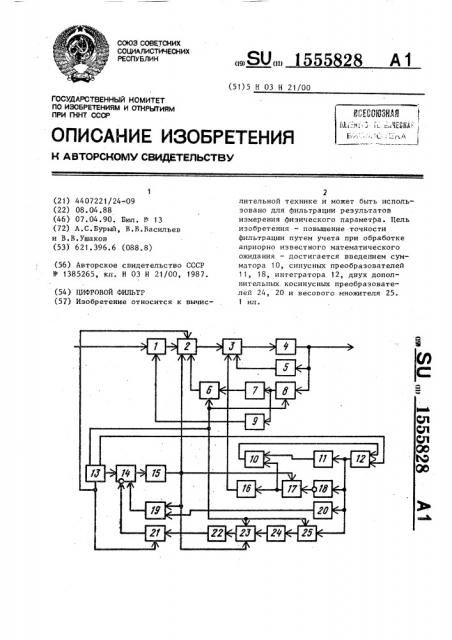

На чертеже приведена электрическая структурная схема цифрового фильтра.

Цифровой фильтр содержит вычита- 15 тель 1, первый весовой множитель 2, первый сумматор 3, первь»й интегратор

4, первый синусный преобразОватель 5, третий весовой множитель 6, косинусный преобразователь 7, второй весо- 20 вой множитель 8, второй синусный преобразователь 9, третий сумматор 10, третий синусный преобразователь 11 третий интегратор 12, блок 13 памяти, второй сумматор 14, второй интегратор 15, четвертый весовой множитель

16 (делитель на два), пятый весовой множитель 17, четвертый синусный преобразователь 18, восьмой весовой множитель 19, второй дополнительный 30 косипусный преобразователь 20, шестой весовой» множитель 21, квадратор

22, седьмой весовой мнояс»тель 23, первый дополнительный косинусный преобразователь 24 и девятый весовой множитель 25.

Для получения алгоритма работы предлагаемого фильтра используется следующий математический аппарат.

Оцениваемый процесс нели»»еен: 40

6 " <(g)

yet) q(g) (1) где Z(t) — входной сигнал фильтра;

Выходной сигнал фильтра определяется выражением 55

dq{g ) д = f(g) + 0 "— — — к (2(с)- (f(g)j+

3 g корреляционная матрица погрешностей оценок; корреляционная матрица винеровского стохастического процесса; диагональная матрица дисперсий измерений; оценка вектора состояния системы; математическое ожидание вектора состояния системы, которое является решением уравнения

В качестве нелинейных функций взяты f(я ) = sin(g ) s q (g ) = si»»(mg)

m = 1,2,3 .. Соответственно частные производнь е их имеют вид (я+) Д2f (@%)

- -- -- (.»)s(g ) ††" — = -si»1(g )

Я 2. »» g%

13 памяти. На выходе вычитателя 1 формируется сигнал ошибки Z(t) - (p(g ), который действует на первьй» вход множителя 2, на четвертый вход которог поступает коэффициент умножения И с второго выхода блока 13 паа(„) 10

25

35

50

5 155 мяти, а на третий вход — 8 с выхода второго интегратора 15.

B первом сумматоре 3 происходит суммирование величин в соответствии с (3), а сами оценки вырабатываются на выходе первого интегратора 4, с выхода которого сигнал поступает в весовой множитель 8 и первьп» синус-. ный преобразователь 5, в котором вырабатывается сигнал f(g ) в соот»». ветствии с (6), поступающии на второй вход первого сумматора 3. В це-. почке весовой множитель 8, косинусный преобразователь 7, весовой мпо-! а () житель 6 вырабатывается сигнал — -"— а,+ в соответствии (6), поступающий на второй вход весового множителя 2.

В третьем и четвертом синусных преобразователях 11 и 18, весовом множителе 17, третьем сумматоре 10 и интеграторе"12 вычисляется текущее значение математического ожидания вектора состояния системы в соответствии с (5), начальное значение которого поступает с четвертого выхода блока 13 памяти. С выхода весового

B f (g ) множителя 17 составляющая — — — — О а . через делитель на два (весовой множитель 16) поступает на третий вход первого сумматора 3. Во вторых сумматоре 14, интеграторе 15, весовых множителях 19 и 21 вычисляется текущее значение О в соответствии с (4), .которое с выхода второго интегратора

15 поступает на первые входы весовых множителей 17, 19, 23 и третий вход весового множителя 2 соответственно.

Второй дополнительный косинусньш преобразователь 20 обеспечивает формиBf(g ) рование сигнала — — — — в соответстЗя вии с (6), действующего на первый вход весового множителя 19, а в цепочке весовой множитель 25, первьгй» дополнительный косинусньш преобразователь 24, весовой множитель 23, квадратор 22 вырабатывается сигнал v(g )

8 — — — —, поступающий на первьш gr вход весового множителя 21, на второй вход которого поступает коэффициент аг умножения N . Выход весового множи5828 6 теля 21 подключен к инверсному входу второго суг»матора 14, на второй вход которого поступает значение W с первого выхода блока 13, а на первь»»»

5 вход-сигнал 2 — — — »":» с выхода весо »8 вого множителя 19. Во втором интеграторе 15 вычисляется значение»:» в соответствии с (4).

Длительность импульсов входного кода такова, что быстродействие элементов не влияет на работоспособность устройства.

Таким образом, предлагаемь»»» цифровой фильтр позволяет повысить точность оценок измерений за счет учета при обработке априорно известного математического ожидания.

Формула изобретения

Цифровой фильтр, содержащий последовательно соединенные вычитате»»ь, первые весовой множитель, сумматор и интегратор, выход которого является выходом цифрового фильтра, входом которого является первый вход вычитателя, первый синусньп» преобразователь, выход которого соединен с вторым входом первого сумматора, последовательно соединенные второй весовой множитель и синусньп» преобразователь, выход которого подключен к второму входу вычитателя, последова— тельно соединенные косинусный преобраэователь и третий весовый множитель, выход которого соединен с вторым входом первого весового г»но>кителя, пятый весовой множитель,- четвертьш весовой множитель, вторые сумматор и интегратор, последовательно соединенные седьмой весовой множитель, квадратор и шестой весовой множитель, выход которого соединен с инверсныгл входом второго сумматора, восьмой весовой множитель, выход которого соединен с первым входом второго сумматора, выход которого соединен через второй интегратор с третьим входом первого весового множителя и первыми входами пятого, седьмого и восьмого весовых множителей, и блок памяти, первый» выход которого соединен . с вторым входом второго сул»матора, второй выход — с четвертым входом первого и вторым входом шестого ве1555828

Составитель С.Иузычук

Техред А, Кравчук - Корректор H. Король

Редактор И.Имакова

Заказ 561 Тираж 650 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГKHT СССР

113035, Москва, Ж-35, Раушскаи наб., д. 4/5

Производственно-издательский комбинат "Патент", г.Ужгород, ул. Гагарина, 101 совых множителей, а третий выход подключен к второму входу третьего весового множителя и первому входу второго весового множителя, второй вход которого соединен с входом первого синусного преобразователя и выходом первого интегратора, о т л ич а ю шийся тем, что, с целью повышения точности фильтрации, введены последовательно соединенные третьи синусный преобразователь, сумматор, интегратор, девятый весовой множитель и первый дополнительный косинусный преобразователь, выход которого соединен с вторым входом седьмого весового множителя, а также четвертый синусный и второй дополнительный косинусный преобразователи, входы которых соединены с входом третьего синусного преобразователя и выходом третьего интегратора, выход второго дополнительного косинусного преобразователя подключен к второму входу восьмого весового множителя, а выход четвертого синусного преобразователя соединен с вторым входом пятого весового множителя, выход которого соединен с вторым входом третьего сумматора и через четвертый весовой множитель с третьим входом первого сумматора, причем вход косинусного преобразователя соединен с выходом второго. весового множителя, а вторые входы седьмого и девятого весовых множителей соединены с третьим выходом блока памяти, четвертый выход которого подключен к второму входу третьего интегратора.