Корректор с обратной связью по решению

Иллюстрации

Показать всеРеферат

Изобретение относится к технике связи. Цель изобретения - повышение точности коррекции. Корректор с обратной связью по решению содержит сумматоры 1 и 5, пороговые блоки 2 и 7, сумматоры 3 и 8 по модулю два, многоотводные линии 4 и 9 задержки, перемножители 6, анализатор 10 и эл-т 11 задержки. Цель достигается путем обеспечения компенсации межсимвольной помехи. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„«SU„„1555 7 А1 (g1)g H 04 В 3/04

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНЯТИЯМ

ПРИ ГКНТ GvvCP (21) 4373021/24-09 (22) 01 ° 02.88 (46) 07.04.90. Бюл. N 13 (71) Ленинградский электротехнический институт связи им. проф. М.А.БончБруевича (72) А.В.Тюкаев (53) 681.372.8 (088.8) (56)Спилкер Дж. Цифровая спутниковая связь. / Под ред. В.В.Маркова. М.:

Связь, 1979, с.382.

2 (54) КОРРЕКТОР С ОБРАТНОЙ СВЯЗЬЮ ПО

РЕШЕНИЮ (57) Изобретение относится к технике связи. Цель изобретения - повышение точности коррекции. Корректор с обратной связью по решению содержит сумматоры 1 и 5, пороговые блоки 2 и

7, сумматоры 3 и 8 по модулю два, многоотводные линии 4 и 9 задержки, перемножители 6, анализатор 10 и зл-т 11 задержки. Цель достигается путем обеспечения компенсации межсимвольной помехи. 1 ил.

1555870

Изобретение относится к технике связи и может быть использовано в качестве компенсатора межсимвольных помех в каналах с высокой удельной скоростью передачи цифровой информации.

Целью изобретения является повышение точности коррекции путем обеспечения компенсации межсимвольной помехи.

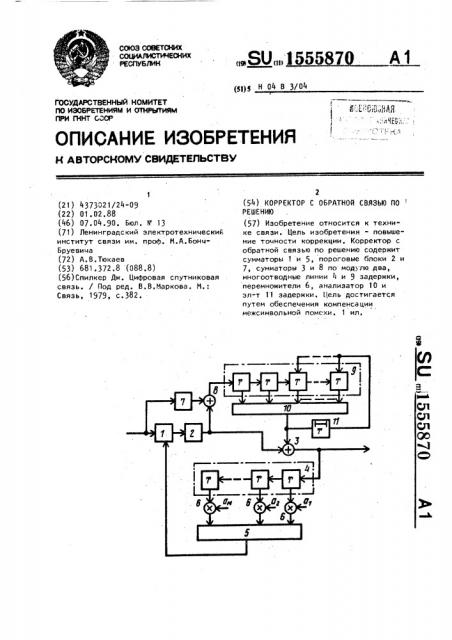

На чертеже приведена схема предлагаемого корректора.

Корректор с обратной связью по решению содержит первый сумматор 1, первый пороговый блок 2, первый сумматор 3 по модулю два и первую многоотводную линию 4 задержки, а также второй сумматор 5, М перемножителей 6 - 6.М, второй пороговый блок

7, второй сумматор 8 по модулю два, вторую многоотводную линию 9 задерж" ки, анализатор 10 и элемент 11 задержки.

Корректор с обратной связью по 25 решению работает следующим образом.

При безошибочном приеме в. установившемся режиме на выходе порогового блока 2 формируется правильная последовательность оценок передаваемых двоичных символов. Линейная комбинация этих оценок образуется на выходе сумматора 5 и представляет из себя значение межсимвольной помехи, присутствующей в очередном элементе сигнала, поступающем на суммирующий вход сумматора 1. Правильность вычислении межсимвольной помехи обеспечивает соответствующий выбор коэффициентов усиления а,- а„на 40 основе априорной определенности ха- 40 рактеристик канала. Таким образом, на выходе сумматора 1 образуется сигнал, лишенный межсимвольной помехи в отсчетных точках, что повышает достоверность его оценки при наличии ад45 дитивных шумов.

В случае ошибочного принятия решения пороговым блоком 2, которое вызвано наличием шума, ошибочный символ поступает на вход линии 4 задерж" ки, приводя к неправильному вычислению очередного значения межсимвольной помехи на выходе сумматора 5.

Таким образом, начиная с этого момента, вероятность ошибки на выходе порогового блока 2 становится выше, чем на выходе блока 7, где решение всегда принимается при отсутствии компенсации межсимвольных помех..

Повышенная вероятность ошибки на выходе блока 2 сохраняется до тех пор, пока ранее принятый ошибочный символ находится в линии 4 задержки.

Если за это время и вследствие повышенной вероятности ошибки вновь принято ошибочное решение пороговым блоком 2, то на выходе сумматора 8 формируется единичный потенциал. Это объясняется тем, .что вероятность ошибочного решения, принимаемого пороговым блоком 7, ниже, чем вероятность ошибки на выходе блока 2 при том условии, что принятый ранее ошибочный элемент находится в линии

4 задержки. Таким образом на вход линии 9 задержки поступает единичный сигнал, при этом ошибочный символ, принятый блоком 2, поступает в линию 4 задержки и создает аналогичные ухудшенные условия приема очередных элементов блока 2.

Если в этих условиях блок 2 вновь примет ошибочное решение (в отличие от блока 7), то в линию 9 задержки поступает второй единичный сигнал.

При этом линия 9 содержит уже два единичных элемента, один из которых находится в первой ячейке этой линии. Логический анализатор 10 вырабатывает единичный уровень всякий раз, когда линия 9 задержки содержит более одного единичного элемента. Этот единичный уровень поступает на второй вход сумматора 3 по модулю два и инвертирует ошибочно принятый блоком 2 элемент. На следующем такте работы единичный уровень с выхода анализатора 10 появляется на выходе элемента 11 задержки и поступает на установочные входы, всех ячеек линии

9 задержки, кроме первых двух. Таким образом в линии 9 стираются единичные элементы, вызванные предыдущей ошибкой. Далее процесс повторяется.

Таким образом, на выходах -коррек" тора проходят только две ошибки, вызванные, влиянием шума при правильI ной коррекции межсимвольных искажений. При этом вероятность появления в линии 9 задержки двух единиц, вызванных ошибками на выходе блока 7, является величиной второго порядка малости, которую можно не учитывать.

Распознают ошибки порогового блока 2 и ошибки, допускаемые блоком 7, путем

Формула изобретения

Составитель Л.Тимошина

Техред М.Дндык Корректор Т,Малец

Редактор М.бланар

Тираж 524

Заказ 563 Подписное

ВНЙИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, M-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101

5 -l 5 сравнения сигналов на их выходах и анализа полученного сигнала на протяжении М тактовых интервалов.

Предлагаемый корректор подвергнут моделированию на ЭВМ, которое полностью подтверждает наличие положительного эффекта, т.е. повышение помехоустойчивости.

Перемножители 6 могут быть выпол- нены на двоичных элементах цифровой схемотехники, сумматоры обычно выполняются на резистивных элементах, а также на операционных усилителях, меющих суммирующий и вычитающий вхоы. Логический анализатор является огической схемой, выполненной на ифровых логических элементах. Правило функционирования анализатора заключается в том, что на его выходе присутствует единичный потенциал, если на входах присутствует более одного единичного сигнала.

Корректор с обратной связью по ренению, содержащиЙ последовательно соединенные первый сумматор и первый пороговый блок, первую многоотводную

55070 6 линию задержки, отводы которой подключены к первым входам t1 умножителей, выходы которых подключены к входам второго сумматора, выход кото-1 рого подключен к вычитающему входу первого сумматора, суммирующий вход которого является входом корректора с обратной связью по решению, о тл и ч а ю шийся тем, что, с целью повышения. точности коррекции путем обеспечения компенсации межсимвольной помехи, введены последовательно соединенные второй пороговый блок, вход которого подключен к суммирующему входу первого сумматора, второй сумматор по модулю два, к вто» рому входу которого подключен выход первого порогового блока, вторая

20 многоотводная линия задержки, анализатор и первый сумматор по модулю два, к второму входу которого подключен выход первого порогового блока, . выход первого сумматора по модулю

25 два подключен к входу первой многоотводной линии задержки, а также элемент задержки, к входу которого подключен выход анализатора, а выход подключен к установочным входам М-2

30 .ОтвОДОв ВТОРОи мнОГООтВОДной линии задержки.