Цифровая система коммутации с распределенным управлением

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи. Цель изобретения - повышение пропускной способности. Цифровая система коммутации с распределенным управлением содержит блок 1 коммутации, оконечные блоки 2, каждый из которых состоит из блока 3 сопряжения, блока 4 управления, блока 5 памяти, шины 6 адреса и данных, шины 7 управления и блока 8 занятия магистрали, а также содержит блок 9 синхронизации, системный блок 10 памяти, системную шину 11 данных, системную шину 12 адреса, системную шину 13 управления, шину 14 синхронизации, шины 15 коммутации и группы 16 входящих линий связи. Цель достигается путем уменьшения времени установления соединения. Дана ил. выполнения блока 8 занятия. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (19),(11) (51)5 Н 04 М 3 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н Д ВТОРСНОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4430685/24-09 (22) 27.05.88 (46) 07.04..90. Бюл. 11 -13 (71) Московский электротехнический институт связи (72) В .А Буланов, Т.А.Буланова и В.А.Горохов (53) 621 .395.55(088.8) (56) Electricol Communication.—

The Technical Journal of ITT,1985, .Vol.59, И- 1/2.

2 (54) ЦИФРОВАЯ СИСТЕМА К01п(УНЦИИ С

РАСПРЕДЕЛЕННЬ)М УПРАВЛЕНИЕМ (57) Изобретение относится к электросвязи. Цель изобретения - повышение пропускной способности. Цифровая система коммутации с распределенным уп, равлением содержит блок 1 коммутации, оконечные блоки 2, каждый из кбторых состоит из блока 3 сопряжения, блока 4 управления, блока 5 памяти, шины 6 адреса и данных, шины 7 управ1555904 ления и блока 8 занятия магистрали, а также содержит блок 9 синхронизации, системный блок 10 памяти, системную шину ! 1 данных, системную шину 12 адреса, 5 системную шину 13 управления, шину

Изобретение о гносится к технике электрической связи и может использоваться в системах автоматической коммутации.

Целью изобретения является повыше-, !5 ние пропускной способности путем уменьшения времени установления соединения.

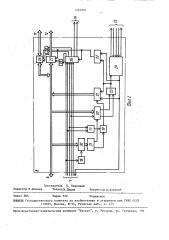

На Фиг.1 приведена структурная схема цифровой системы коммутации с 20 распределенным управлением; на Фиг.2блок занятия магистрали. !

Система (фиг.1) содержит блок 1 коммутации, N+1 оконечных блоков 2, каждый из которых включает в себя блок 3 сопряжения, блок 4 управления, блок 5 памяти, шину 6 адреса и данных, шину 7 управления, блок 8 занятия магистрали (кроме N+1),.а также блок 9 синхронизации, системный блок

10 памяти, системную шину 11 данных, системную шину 1 2 адреса, системную шину 1 3 управления, шину 1 4 синхронизации, шины 15 коммутации, группы

16 входящих линий связи. Блок 8 заня- 35 тия магистрали (фиг.2) содержит первый элемент ИЛИ 17, первый инвертор

18 второй элемент ИЛИ 19, первый шинный формирователь (ШФ) 20, второй

ШФ 21, элемент И-НЕ 22, триггер 23, контроллер 24, третий 25, четвертый

26 ШФ, регистр 27 адреса системного блока 10 памяти, третий элемент ИЛИ

28, второй инвертор 29, регистр 30 адреса блока 8, дешифратор 31 адре45 са.

Цифровая система коммутации работает следующим Ьбразоь!.

На выходе блока 9 синхронизации имеется последовательность прямоугольных импульсов, которая поступает на входы контроллеров 24 блоков

8 занятия магистрали, образукщих циклический распределенный регистр сдвига. При поступлении первого импульса. на выходе первого контроллера 24 появляется сигнал прерывания, поступающий на блок 4 управления.

14 синхронизации, шины !5 коммутации и группы 1 6 входящих линий связи.

Цель достигается путем уменьшения времени установления соединения. Дана ил.выполнения блока 8 занятия. 2 ил.

Здесь возможны два случая. В первом случае блок 4 должен обратиться к системному блоку 10 памяти. При этом можно выделить несколько этапов.

На первом этапе обеспечивается захват системного блока 1 0 памяти.

Блок 4 выдает на шину 6 адреса блока

8 сигнал, который записывается в регистр 30 адреса по отрицательному

Фронту управляющего импульса, поступающего на управляющий вход регистра

30 адреса из блока 4 через шину 7 управления и первый инвертор 18. Адрес с выходов регистра 30 адреса посту— пает на дешифратор 31 адреса, на первом выходе которого появляется управляющий сигнал, разрешающий прохождение сигналов через первый ШФ 20.Блок

4 выдает на шину 6 сигнал, который по положительному фронту сигнала записи заносится в тригтер 23. Выходной сигнал триггера 23 поступает на блок 9 синхронизации, блокируя выдачу очередного импульса. Одновременно этот сигнал. поступает на первый вход элемента И-HE 22, на второй вход которого поступает разрешающий потенциал с выхода контроллера 24, при этом выходной сигнал элемента

И вЂ” НЕ Z2 разрешает прохождение инфор

| мации через четвертый ШФ 26, а также переводит выходы регистра 27 адреса из состояния высокого импеданса в рабочий режим, подготавливая прохождение разрешающего сигнала низкого уровня с выхода четвертого ШФ 26 через третий элемент ИЛИ 28 на управляющий вход третьего ШФ 25.

На втором этаге осуществляется проверка захвата системного блока 10 памяти. Аналогично первому этапу блок 4, используя регистр 30 адреса, дешифратор адреса 31, первый 17 и второй 1 9 элементы ИЛИ, открывает второй ШФ 21 и считывает выходные сигналы триггера- 23 и контроллера 24.

Если при анализе данных. сигналов их значение соответствует высокому уровню, то захват системного блока 10

1555 осуществлен, в противном случае необходимо сбросить триггер 23 и ожидать поступления следующего сигнала прерывания.

В случае захвата системного блока !

О работа с ним осуществляется посредством выбора соответствующего сегмента памяти. При этом выполняются режимы чтения и записи. Чтение инфор- 10 мации из соответствулцего сегмента памяти и запись информации осуществляются по командам блока 4, захватившего в данный момент времени системный блок 10. 15

Для освобождения системного блока

10 необходимо сбросить триггер 23 посредством записи в него сигнала низкого уровня. Во втором случае блок

4 управления не нуждается в работе 20 с системным блоком 10 памяти. Дпя этого блок 4 маскирует прерывание по соответствующему выводу.

Формула и з о б р е т е н и я

Цифровая система коммутации с распределенным управлением, содержащая

904

И+1 оконечных блоков, соединенных соответствующими шинами коммутации с блоком коммутации, N групп входящих линий связи, подключенных к соответствующим оконечным блокам, кроме N+1 причем каждый из них содержит блок сопряжения, соединенный с соответствующей группой входящих линий связи и шиной коммутации, блок управления и блок памяти, Соединенные шиной адреса и дайных и шиной управления с блоком сопряжения, о т л и ч а ю— щ а я с я тем, что, с целью повышения-,пропускной способности путем уменьшения времени установления cQ единения, введены блок синхронизации, подключенный к шине синхронизации, системный блок памяти, соединенный с системными шинами адреса, данных и управления, а в каждый оконечный блок, кроме N+1, введен блок занятия магистрали, подключенный к соответствующим шине адреса и данных и шине управления, причем каждый блок заня,тия магистрали соединен с системными шинами адреса, данных и управления, а также шиной синхронизации.

1555904

Составитель В. Паницкий

Редактор М.Бланар Техред М.Дидык Корректор В,Кабаний

Заказ 565 Тираж 522 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r Ужгород, ул. Гагарина, 101