Накапливающий сумматор

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств отображения информации. Целью изобретения является расширение функциональных возможностей путем обеспечения предварительной записи кода двоичного числа. Поставленная цель достигается тем, что накапливающий сумматор дополнительно содержит счетчик, два элемента НЕ, блок элементов сравнения, триггер, два элемента И с соответствующими связями. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

75 1 А1 (19) (111 (51) 5 G 06 F 7/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

tlO ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4436807/24-24 (22) 07,06.88 (46) 15.04.90. Бюл, М 14 (72) Н.И.Луканов, А.В.Низовой и К.K ° Костров (53) 681.325 (088,8) (56) Авторское свидетельство СССР

1(- 1251069, кл, G 06 F 7/50, 1985.

Справочник по интегральным микросхемам. /Под ред. Б,В.Тарабрина, И.: Энергия, 1981, с. 741, рис.5-250. (54) НАКАПЛИВАЮЩИЙ СУИМАТОР (57) Изобретение относится к автомаИзобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств отображения информации.

Цель изобретения — расширение функциональных возможностей накапливающего сумматора путем обеспечения предварительной записи кода двоичного числа.

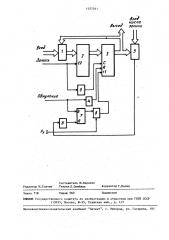

На чертеже изображена структурная схема накапливающего сумматора.

Накапливающий сумматор содержит сумматор 1, регистр памяти 2, счетчик

3, первый элемент НЕ 4, блок элементов сравнения 5, второй элемент НЕ

6, триггер 7, первый элемент И 8, второй элемент И 9.

На накапливающий сумматор поступает следующая информация и сигналы: на второй вход сумматора 1 — двоичный код суммируемого числа; на входы С2 регистра памяти 2 и вход второго элемента И 9 — сигнал "Запись"; на входы первого элемента НЕ 4 и S вход триггера 7 - сигнал "Обнуление"; на

2 тике и вычислительной технике и может быть использовано при построении устройств отображения информации.

Целью изобретения является расширение функциональных возможностей путем обеспечения предварительной записи кода двоичного числа. Поставленная цель достигается тем, что накапливающий сумматор дополнительно содержит счетчик, два элемента НЕ, блок элементов сравнения, триггер, два элемента И с соответствующими связями.

1 ил..второй вход элемента И 8 — тактовая частота (Р ); на второй вход блока элементов сравнения 5 — двоичный код числа предварительной записи.

Выход счетчика 3 является выходом Д накапливающего сумматора.

Накапливающий сумматор работает р следующим образом.

Рассмотрим работу схемы с приходом сигнала "Обнуление", под действием которого триггер 7 переключается и © с его выхода на первый вход элемента ©1

И 8 снимается "1".

Одновременно сигнал "Обнуление" инвертируется элементом НЕ 4, поступает на вход установки нуля R счетчика 3 и обнуляет его.

На выходе счетчика 3 по всем разрядам устанавливается значение "0", которое поступает на сумматор 1 и блок. элементов сравнения 5.

Значение "0" на выходе счетчика 3 сохраняется в течение действия сигнала Обнуление".

1557561 а

С окончанием сигнала "Обнуление" импульсы тактовой частоты Г через элемент И 8 поступают на вход "прямого счета " (+1) реверсивного счетчика

3, где импульсы тактовой частоты Г суммируются. Когда код двоичного числа счетчика 3 станет равным коду двоичного числа предварительндй записи, поступающего на блок. элементов сравнения 5, тогда с выхода (А=В) блока элементов сравнения 5 снимается сигнал "1". Этот сигнал инвертируется . элементом НЕ 6 и поступает на вход триггера 7.

Триггер 7 переключается. Прохождение тактовых импульсов через элемент

И 8 на счетчик 3 прекращается, так как с переключением триггера 7 с его выхода на первый вход элемента И 8 поступает напряжение "О", Так перед началом суммирования осуществляется запись счетчик 3 кода заданного двоичного числа.

Далее на вход сумматора 1 поступа- 5 ет код двоичного числа, который складывается с содержимым счетчика 3.

Полученная сумма записывается в регистр памяти 2 в момент спада сигнала "Запись" на его входе С2. Этим же импульсом, но с задержкой на эле30 менте И 9, по потенциалу "О", поступающего на вход предварительной записи С счетчика 3, двоичный код числа из регистра памяти 2 переписывается в счетчик 3. 35

С приходом следующего сигнала "Запись" цикл суммирования повторяется.

В результате суммирования на выходе накапливающего сумматора получаем значение двоичного кода S

Sиз + в nit где S — значение двоичного кода чисI ла на выходе накапливающего сумматора;

S — предварительно записанное п,з число в счетчик перед суммированием;

Я, — код двоичного числа, посту- пающего на сумматор 1; п - количество сигналов "Запись". 50

С приходом сигнала "Обнуление" весь цикл повторяется.

Формула и з обретения

Накапливающий сумматор, содержащий сумматор и регистр памяти, при этом выход сумматора соединен с информационным входом регистра памяти, а второй вход сумматора — с входом суммируемо- го числа накапливающего сумматора, отличающийся тем, что, с целью расширения функциональных возможностей устройства путем обеспечения предварительной записи кода двоичного числа, в накапливающий сумматор введены счетчик, два элемента НЕ, блок элементов сравнения, триггер, два элемента И, при этом выход регистра памяти соединен с информационным входом счетчика, выход которого соединен с первыми входами сумматора и блока элементов сравнения, выход первого элемента НЕ соединен с входом установки нуля счетчика, вход Прямой счет" которого соединен с выходом первого элемента И, первый вход кото« рого соединен с выходом триггера, вход установки в нулевое состояние триггера соединен с выходом второго элемента НЕ, вход которого соединен с выходом блока элементов сравнения, выход второго элемента И соединен с управляющим входом предварительной записи счетчика, вход управления предварительной записи регистра памяти и вход второго элемента И соединены с входом сигнала "Запись" накапливающего сумматора, вход первого элемента

НЕ и вход установки в единичное состояние триггера соединены со входом сигнала "Обнуление" накапливающего сумматора, второй вход первого элемента И соединен с входом тактовой частоты накапливающего сумматора, второй вход блока элементов сравнения соединен с входом кода числа предварительной записи накапливающего сумматора, а выход счетчика соединен с выходом накапливающего сумматора.

1557561 ь/ циси

Р4/А ы,ы лгал

Составитель Ю.Варакин

Редактор И.Товтин,Техред Л.Олийнык Корректор Т,Малец

Тираж 560

Подписное

Заказ 718

Ф

ВНИИПИ Государственного комитета по изобретениям и открь:тиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r ° Ужгород, ул. Гагарина, 101