Универсальный регистр

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для параллельного приема и хранения информации в цифровых системах, а также для последовательного сдвига, свертки информации и генерации псевдослучайных последовательностей сигналов. Целью изобретения является повышение быстродействия в режимах параллельного приема и начальной установки. Для достижения цели в каждом разряде регистра мультиплексоры 6 включены между D-триггерами первой 5 и второй 7 ступеней, а входы 12 и 13 начальной установки первого разряда выделены в отдельную группу. 1 ил., 2 табл.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУ!-ЛИК (51)5 G 11 С 19 00

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,К СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ (21) 4410095/24-24 (22) 15.02.88 (46) 15.04.90. Бюл. Р 14 (71) Ленинградский электротехнический институт им. В.И:Ульянова (Ленина) (72) А.И.Водяхо, В.В.Грушин, А.С.Календарев, И.Е.Новиков, В.В,НовосеJIoB ° В.У.IIJIlocHHH и Д.В.Лузанков (53) 681.327.66(088.8) (56) Авторское свидетельство СССР

Р 1239722, кл. G 06 F ii/26, 1985.

Электроника, 1983, Ф 5, с.30, рис.4 ° (54) УНИВЕРСАЛЬНЫЙ РЕГИСТР (57) Изобретение относится к вычис„„Su„„> 557588 А 1

2 лительной технике и может быть использовано для параллельного приема и хранения информации в цифровых системах, а также для последовательного сдвига, свертки информации и генерации псевдослучайных последовательностей сигналов. Целью изобретения является повышение быстродействия в режимах параллельного приема и начальной установки, Для достижения цели в каждом разряде регистра мультиплексоры 6 включены между D-триггерами первой 5 и второй 7 ступеней, а входы !2 и 13 начальной установки первого разряда выделены в отдельную группу. 1 нл., 2 табл.!

557588

10 !

30

40

50

Изобретение относится к вычислительной технике и может быть использовано в качестве регистра для параллельного приема и хранения информации в цифровых системах, а также для последовательного сдвига, свертки информации и генерации псевдослучайных последовательностей сигналов (ПСП)."

Целью изобретения является повышение быстродействия регистра в режимах параллельного приема информации и начальной установки.

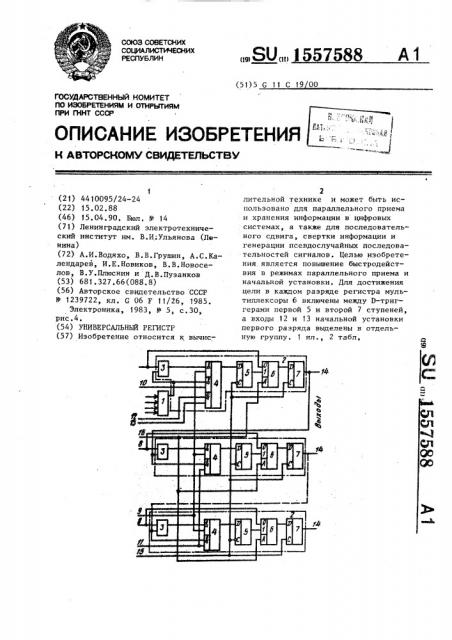

На чертеже приведена схема регистра.

Регистр содержит блок свертки и в каждом разряде 2 сумматор 3 но модулю два, элемент И-ИЛИ 4, первыйD-триггер 5, мультиплексор 6 и второй D-триггер 7.

На чертеже также изображены параллельные информационные входы 8, вход 9 разрешения свертки, вход 10 разрешения генерации ПСП, вход 11 разрешения сдвига, информационный последовательный вход 12, вход 13 начальной установки первого разряда, информационные выходы 14, синхровход 15, вход 16 разрешения параллельного приема информации.

Входы блока 1 свертки соединены с выходами вторых D-триггеров 7 раз рядов регистра, При построении конкретного регистра эти соединения зависят от полиномов свертки и разрядности регистра. Некоторые примеры связей приведены в табл.1.

Работа универсального регистра происходит следующим образом. Режимы работы прйведены в табл.2.

Режим параллельного приема.

На входы 9-13 подаются произвольные сигналы, на вход 16 подается "0", на синхровход 15 поступают синхроимпульсы. Мультиплексоры 6 по "0" на управляющем входе обеспечивают прохождение сигналов с информационных входов 8 на информационные входы Dтриггеров 7. По синхросигналам на синхровходе 15 осуществляется запись информации в D-триггеры 7.

Режим начальной установки.

На входы 9-11.устанавливаются "0", на вход 13 — "!". На входе 12 установлено значение начальной установки для первого разряда ("0" или 1 1).

При поступлении синхроимпульса в

D-триггеры всех разрядов кроме первого записываются нули. B D-триггер первого разряда устанавливается требуемое значение.с входа 12 ° Таким образом, за один такт в регистре ус-; танавливается начальное значение

000...0 или 100...0.

Режим сдвига .информации.

На входы 9 и 10 подается "0", на входы 11, 13, 16 подается "1", на вход 12 — последовательность сигналов для сдвига в регистр, на синхровходе 15 присутствует серия синхросигналов. Сдвиг информации и запись ее в D-триггреы осуществляется по синхросигналам. Информация снимается с регистра параллельно с разрядных выходов 14 либо последовательно с выхода 14 последнего разряда регистра.

Режим генерации ПСП.

На входы 9 и 13 подается "0", на входы 10, 11, 16 подается "1", на синхровход 15 подается серия синхроимпульсов.

Информация, формируемая в D-триг-. герах, сдвигается через сумматоры

3 по модулю два и элемент И-ИЛИ 4.

Генерация ПСП осуществляется согласно реализованному в регистре полиному обратных связей.

Режим параллельной свертки.

В этом режиме на входы 10, 11, 13 подается "0", на входы 9, 16 — "1", на синхровход 15 - последовательность синхросигналов. На информационные входы 8 подаются рабочие последовательности сигналов, сигнатура которых формируется в регистре.

Информация через сумматоры 3 по модулю два со входов 8 и по обратным связям через блок 1 свертки поступает на D-триггеры 5, а затем через мультиплексоры 6 íà D-триггеры

7 в виде сформированной сигнатуры.

Формула изобретения

Универсальный регистр, содержащий блок свертки и в каждом разряде первый и второй D-триггеры, сумматор по модулю два, мультиплексор и элемент И-ИЛИ, причем в каждом раз ряде первый вход сумматора по модулю два соединен с первым информационным входом мультиплексора и является соответствующим параллельным

Таблица

Выходы разрядов, от которых отведены связи

Разрядность регистра

04, 01 или 04, 03

08, 04, 03, 02 или 08, 06, 03, 02 или 08, 07, 05, 03

016, Oi4s 013,011 или 016, 012, 09, 07

16

Таблица 2

Синхровход Инф.послед. Режимы

f5 вход 12

Входы управления (Информ. входы (8) 13 16

9 10 11

Параллельный прием

Нач установка первого разряда

Сдвиг

Генерация ПСП

Параллель.ная свертка

Х Х Х Х 0

ПК

0 0 0

1/О

ОС

X 0 0 1

Х 0 1 1

ПК f 0 0

0

ПК х

СС

СС

СС

П р и м е ч а н и е. СС вЂ” серия синхроимпульсов, ОС вЂ” одиночный синхроимпульс, Х вЂ” безразличное состояние входа, HK — произвольньп1 код.

5 15575 информационным входом регистра, выход сумматора по модулю два соединен с первым входом первой группы элемента И-ИЛИ, второй вход которой является входом разрешения свертки устройства, а выход соединен с D-входом первого D-триггера, С-вход которого соединен с С-входом второго

D-триггера и является синхровходом устройства, в каждом разряде, кроме первого, первый вход второй группы элемента И-ИЛИ соединен с вторым входом сумматора по модулю два данного разряда и выходом второго D-тригге5 ра предыдущего разряда, второй вход второй группы элемента И-ИЛИ является входом разрешения сдвига регистра, первые входы второй и третьей групп элемента И-ИЛИ первого разряда 20 являются соответственно информационным последовательным входом и входом разрешения генерации псевдослучайных последовательностей регистра, 88 6 второй вход третьей группы элемента И-ИЛИ первого разряда соединен с вторым входом сумматора по модулю два данного разряда и выходом блока свертки, входы которого соединены с выходами вторых D-триггеров разрядов регистра в соответствии с полиномом свертки, о т л и ч а ю щ и й— ., с я тем, что, с целью повышения быстродействия регистра в режимах па.раллельного приема информации и начальной установки, в каждом разряде второй информационный вход мультиплексора соединен с выходом первого

D-триггера, выход мультиплексора соединен с D-входом второго D-триггера, а управляющий вход является входом разрешения параллельного приема информации в регистр, второй вход второй группы элемента И-ИЛИ первого разряда является входом начальной установки первого разряда.