Устройство для буферизации информации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства буферной памяти в системах сбора и обработки информации. Целью изобретения является повышение производительности вычислительной системы за счет аппаратной отбраковки "сбойных пачек" данных. Устройство содержит блок памяти, дешифратор, счетчик, триггер, два элемента И, два элемента ИЛИ, элемент НЕ и элемент задержки. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИМИСТИЧЕСНИХ

РЕСПУБЛИК

А1 (19) (И) ($))$ С 06 F 13/00 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К A BTOPCHQMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

IlO ИЗОБРЕТЕНИЯМ И (ЛНРЬ)ТИЯМ

ПРИ ГКНТ СССР (21) 4408154/24-24 (22) 11.04.88 (46) 23.04.90, Бюл. Е - 15 (72) В.И,Юдин (53) 681.325(088.8) (56) Авторское свидетельство СССР

Р 1278861, кл. С 06 Р 13/00, 1986.

Авторское свидетельство СССР

У1236491, кл. G 06 F 13/00, 1986.

Изобретение отнбсится к вычислительной технике и может быть использовано в качестве буферной памяти в системах сбора и обработки информации.

Цель изобретение — повышение достоверенности передачи информации и производительности вычислительной системы за счет аппаратной отбраковки "сбойных пачек" данных.

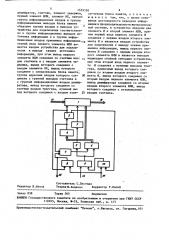

На чертеже представлена структур- ная схема устройства.

Устройство содержит блок 1 памяти, триггер 2, элемент HE 3, дешифратор 4, элемент 5 задержки, счетчик 6, элемент ИЛИ 7, элемент И 8, элемент ИЛИ

9, элемент И 10, входы и выходы 1 l-15.

Устройство работает следующим образом.

В исходном состоянии триггер 2 и счетчик 6 находятся в нулевом состо2 (54) УСТРОЙСТВО ДЛЯ БУФЕРИЗАЦИИ

ИНФОРИАЦИИ (57) Изобретение относится к вычислительной технике и может быть использовано в качестве устройства буферной памяти в системах сбора и обработки информации. Целью изобретения является повышение производительности вычислительной системы за счет аппаратной отбраковки "сбойных пачек данных. Устройство содержит блок памяти, дешифратор, счетчик, триггер, два элемента И, два элемента ИЛИ, элемент НК, элемент задержки. 1 ил. янин (цепь начальной установки не показана), выход блока 1 памяти находится в третьем состоянии, т.е. отключен, от абонента (приемника) за счет высокого уровня на выходе элемента HE 3.

На вхоц записи-считывания блока 1 памяти с нулевого выхода триггера 2 подается высокий уровень, который настраивает блок 1 памяти на прием информации, т.е, на режим "запись".

Источник информации выдает на информационный вход 11 устройства и вход блока 1 памяти. первое слово данных, после чего на вход 14 синхронизации записи поступает первый импульс записи. Проходя через элемент ИЛИ 9, импульс записи воздействует на счетный вход счетчика 6, формируя на адрес.ном входе блока 1 памяти первый адрес.

Мчпульс записи с выхода элемента ИЛИ

9, задержанный на элементе 5 задерж1559350 ки, проходя через элемент НЕ 3, поступает на вход синхронизации блока 1 памяти, производя запись первого информационного слова в первый адрес блока. 1 памяти.

После этого на вход 11 устройства поступает второе информационное слово, а на вход 14 приходит второй импульс записи. Счетчик 6 модифицирует (увеличивает на единицу) адрес и по новому значению адреса приходит запись второго информационного слова и т.д.

На выходе дешифратора 4 сигнал высокого уровня появляется лишь при одном определенном (нужном) значении счетчика 6, при всех остальных значениях счетчика 6 на выходе дешифратора 4 удерживается сигнал низкого 20 уровня. Если в процессе записи очередной пачки информации в тракте синхронизации записи отсутствует пропадание импульсов, то счетчик 6 досчи;,тывает до нужного значения, и на 25 выходе дешифратора 4 вырабатывается сигнал, который устанавливает триггер 2 в "1", а проходя через элемент

ИЛИ 7, сбрасывает счетчик 6 в "0", Если же в процессе записи пачки информации в тракте синхронизации изза действия помех наблюдается пропадание импульсов, то по окончании записи пачки счетчик 6 не досчитывает до нужного значения, на выходе дешиф- 35 ратора 4 сохраняется низкий уровень и триггер 2 остается в состоянии "0".

В режиме чтения блокируется выда- ча в устройство информационных слов (вход 11) и синхроимпульсов записи 40 (вход 14), а абонент (приемник) выдает в устройство (на вход 15) синхроимпульсы считывания.

Если в процессе записи отсутствует 45 пропадание синхроимпульсов записи, то низкий уровень с первого выходе триггера 2, поступая на вход элемента И 8, запрещает прохождение через него синхроимпульсов чтения..Низкий уровень 5<> .с нулевого выхода триггера 2, поступая на вход записи- чтения блока 1 памяти, переводит его в режим "Чтение". Высокий уровень с единичного

- выхода триггера 2, поступая на вход элемента И 10, разрешает прохождение синхроимпульсов считывания с входа 15 через элемент И 10 на вход элемента

ИЛИ 9. С выхода элемента ИЛИ 9 синхроимпульс считывания поступает на счетный вход счетчика 6 (он сброшен и "0"), устанавливая первый адрес, и элемент 5 задержки.

После установки первого адреса первый импульс считывания с выхода элемента 5 задержки через элемент НЕ

3 поступает на вход синхронизации блока 1 памяти, снимает с его выхода третье состояние и выдает информационное слово на выход 12. После этого на вход 15 поступает второй синхроимнульс считывания, проходя через элементы И 10 и ИЛИ 9, он поступает на счетчик 6, увеличивая адрес на единицу, и осуществляет считывание второго информационного слова. После того, как весь массив информационных слов выдан абоненту, на дешифраторе

4 вырабатывается импульс, устанавливающий триггер 2 в "0". Этот же импульс, проходя через элемент ИЛИ 7, устанавливает в "0" счетчик 6, Устройство готово к приему новой пачки информационных слов.

Если в процессе наблюдается пропадание синхроимпульсов записи, то высокий уровень с нулевого выхода триггера 2, поступая на вход элемента И 8, разрешает прохождение через него синхроимпульсов считывания. Низ- кий уровень r единичного выхода триггера 2, поступая на вход элемента

И 10, запрещает прохождение синхроимпульсов считывания с входа 15 через элемент И 10 и элемент ИЛИ 9 на вход элемента 5 задержки и счетный вход счетчика 6. Синхроимпульсы считывания с входа .15 через элемент И 8 и элемент ИЛИ 7 поступают на установочный вход счетчика 6, устанавливая его в "0". Синхроимпульсы считывания не проходят на вход синхронизации бло.ка 1 памяти, считывания информации не происходит. Синхроимпульсы считывания с выхода элемента И 8 поступают на управляющий выход 13 устройства и могут быть использованы для инди1 кации сбойной ситуации. По окончании цикла считывания триггер 2 и счетчик

6 оказываются установленными в "0", т.е. -устройство готово к приему новой пачки информационных слов. Выдачи"сбойной пачки" информации не происходит

Формула изобретения

Устройство для буферизации информации, содержащее блок памяти, триггер, Составитель С.Пестмал

Техред М.Ходапич Корректор Т.Палий

Редактор И.Шулла

Заказ 838 Тирах 565 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.уагород, ул. Гагарина, 101

155935 дешифратор, счетчик, элемент эадерхки, первый элемент ИЛИ, элемент НЕ, причем группа информационных входов и группа информационных выходов блока памяти образуют группы входов и выходов ус5 тройства для подключения соответственно к группе информационных выходов источника информации и к группе .информационных входов приемника информации,10 первый вход первого элемента ИЛИ является входом устройства для подключения к выходу записи источника

I информации, при этом выход первого элемента ИЛИ соединен со счетным входом счетчика и с входом элемента задержки, выход которого соединен с входом элемента НЕ, выход которого соединен с синхровходом блока памяти, группа адресных входов которого сое- 20 динена с группой выходов счетчика и с группой информационных входов дешифратора, выход которого соединен со счетным входом триггера, нулевой выход которого соединен с входом запи- 25

0 6 си-чтения блока памяти, о т л и ч а -. ю щ е е с я там, что, с целью повышения достоверности передачи информации ипроизводительности вычислительной системы, в устройство введены два элемента И и второй элемент ИЛИ, причем первый вход первого элемента И соединен с первым входом второго элемента И и является входом устройства для подключения к выходу чтения при- емника информации, выход первого элемента И соединен с первым входом второго элемента ИЛИ и является выходом индикации сбойной ситуации устройства, при этом второй вход первого элемента И соединен с нулевым выходом триггера, единичный выход которого соединен со вторым входом второго элемента И, выход которого соединен со вторыя входом первого элемента ИЛИ, выход дешифратора соединен со вторым входом второго элемента ИЛИ, выход которого соединен с установочным входом счетчика.