Устройство для сопряжения двух эвм

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для сопряжения двух разноскоростных ЭВМ или других устройств обработки данных. С целью сокращения аппаратурных затрат устройства и предотвращения потери информации в устройство, содержащее сумматор, коммутатор вывода информации, блок буферной памяти, дешифратор управляющих сигналов, счетчики записи и считывания, группу элементов НЕ, дешифраторы максимального и минимального кодов, введены два шинных формирователя, три селектора импульсов, коммутатор ввода информации. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (1)5 G 06.F 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTGPCHGMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4421 724/24-24 (22) 05.05.88 (46) 23.04.90. Бюп. Р 15 (71) Центральное конструкторское бюро с опытным производством АН БССР (72) A.Ë.Øàéêîâ (53) 681.325(088.8) (56) Авторское свидетельство СССР

Р 881722, кл. С 06 F 13/00, 1979.

Авторское свидетельство СССР

) - 1290339, кл . G 06 F 13/00, 1985.

Изобретение относится к автомати-е и вычислительной технике и может быть использовано для сопряжения двух разноскоростных устройств обработки данных. . Целью изобретения является сокращение аппаратурных затрат устройства.

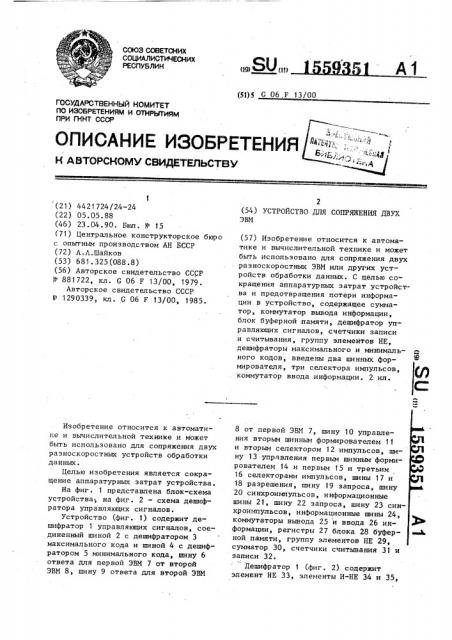

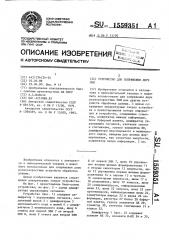

На фиг. 1 представлена блок-схема устройства; на фиг. 2 — схема дешифратора управляющих сигналов °

Устройство (фиг. 1) содержит дешифратор 1 управляющих сигналов, соединенный шиной 2 с дешифратором 3 максимального кода и шиной 4 с дешифратором 5 минимального кода, шину 6 ответа для первой 3ВМ 7 от второй

ЭВМ 8, шину 9 ответа для второй 3ВМ

2 (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ДВУХ

3ВМ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано для сопряжения двух разноскоростных ЭВМ или других устройств обработки данных. С целью сокращения аппаратурных затрат устройства и предотвращения потери информации в устройство, содержащее сумматор, коммутатор вывода информации, блок буферной -памяти, дешифратор управляющих сигналов, счетчики записи и считывания, группу элементов НЕ, дешифраторы максимального и минимального кодов, введены два шинных формирователя, три селектора импульсов, коммутатор ввода информации. 2 ил.

8 от первой ЭВМ 7, шину 10 управления вторым шинным формирователем 11 и вторым селектором 12 импульсов, шину 13 управления первым шинным формирователем 14 и первым 15 и третьим

16 селекторами импульсов, шины 17 и

18 разрешения, шину 19 запроса, шину

20 синхроимпульсов, информационные шины 21, шину 22 запроса, шину 23 синхроимпульсов, информационные шины 24, коммутаторы вывода 25 и ввода 26 информации, регистры 27 блока 28 буфер" ной памяти, группу элементов НЕ 29, сумматор 30, счетчики считывания 31 и записи 32. дешифратор 1 (фиг. 2) содержит элемент НЕ 33, элементы И-НЕ 34 и 35, 1559351 элемент HE 36, элементы И-HE 37 и 38, элемент НЕ 39, элементы И-НЕ 40-42 и элемент HE 43.

Устройство работает следующим об5 разом.

В исходном состоянии счетчики считывания 31 и записи 32 установлены в исходное положение, например нулевое.

Передача информации ЭВМ 7 начинается выдачей сигнала запроса по шине 22.

Если ЭВМ 8 готова к приему информации, то она выдает с задержкой по шине 6 сигнал "Готово" ЭВМ 7. Дешифратор 1 под управлением шин 10 и 13 подключа- 15 ет шинный формирователь 14 к приему информации по шине 24 от ЭВМ 7 и далее через селектор 15 на входы коммутатора 26, шинный формирователь 11 подключает выход коммутатора 25 че- 20 рез шинный формирователь 11 по шине

21 ЭВМ 8 и выдает сигналы на шины 17 и 18, разрешающие ЭВМ 7 и 8 выдавать синхроимпульсы по шинам 23 и 20.

После этого ЭВМ генерирует после- 25 довательность кодов, поступаняцих через шину 24, шинный формирователь 14, селектор 15 на информационные входы коммутатора 26. Одновременно каждая кодовая посылка сопровождается снн- 30 хроимпульсом, которым она записывается в соответствующий регистр 27, определяемый кодом коммутатора 26, и одновременно синхроимпульс . своим задним фронтом формирует на выходе счетчика

32 код нового адреса на входе коммутатора 26, по которому записывается следующая кодовая посылка информации в блок 28.

Приходящим синхроимпульсом по шине 40

20 из ЭВМ 8 информация с соответствующего регистра 27 блока 28 буферной памяти, определяемого кодом коммутатора 25, через шинный формирователь 11, шину 21 считывается ЭВМ 8. Одновре- 45 менно этот же синхроимпульс своим задним фронтом формирует на выходе счетчика 31 считывания новый код адреса на входе коммутатора 25, по которому считывается следующая кодовая посылка 50 информации из блока 28 буферной памя— ти ЭВМ 8.

При этом код адреса с, выхода счетчика 32 записи поступает на вторые

55 входы слагаемого сумматора 30, на первые входы слагаемого которого поступа- ет код адреса с выхода счетчика 31 считывания через элементы НЕ 29. На сумматоре 30 происходит вычитание из величины кода с выхода счетчика 32 записи величины кода с выхода счетчика

31 считывания в дополнительном коде.

В результате этого на выходе сумматора 30 формируется код, равный разности его входных кодов. При этом результат на выходе сумматора получается верным и в случае одновременного прихода синхроимпульсов на выходы счетчиков 31 и 32, так как эти счетчики работают по входу независимо одын от другого, а сравнение их выходных кодов происходит на чисто ком-. бинационной схеме сумматора.

В исходном состоянии, когда коды адресов на выходах счетчиков 31 и 32 равны нулю, на выходе сумматора 30 код также равен нулю, и дешифратор

5 минимального кода выдает сигнал по шине 4 в дешифратор 1, который запрещает по шине 18 (логический нуль). выдачу синхроимпульсов из ЭВМ 8 для считывания информации из блока 28 буферной памяти, а по шине 17 (логическая единица) разрешает ЭВМ 7 выдачу синхроимпульсов для записи информации в блок 28 буферной памяти. Первый же синхроимпульс по шине 23 изменяет на выходе счетчика 32 записи код, одновременно на выходе сумматора 30 появляется код, отличный от нуля, что изменяет состояние выхода дешифратора 5 минимального кода на нулевое, в результате дешифратор 1 выдает,на шину 18 разрешение на считывание информации из блока 28 буферной памяти.

Если запись информации в блок 28 буферной памяти происходит быстрее считывания из нее, то запись происходит до тех пор, пока разность кодов на выходе сумматора 30 не станет равной максимальному коду, тогда дешифратор 3 максимального кода формирует логическую единицу по шине 2,адеши фратор 1 по шине 17 выдает логический нуль, запрещающий подачу синхроимпульсов по шине 23 на запись следующих .информационных кодов в блок

28 буферной памяти до тех пор, пока не освободится хотя бы один из регистров 27.

Если считывание информации происходит быстрее записи, то считывание с блока 28 буферной памяти происходит до тех пор, пока коды записи и считывания на выходе сумматора 30 не

155935 сравняются, тогда дешифратор 5 минимального кода формирует логическую единицу по шине 4, которой дешифратор

1 вьщает по шине 18 логический нуль, запрещающий считывающему устройству выдачу синхроимпульсов на считывание из блока 28 буферной памяти до тех пор, пока не заполнится новой информацией хотя бы еще один регистр 27 блока 28 буферной памяти.

ЭВИ 7 информирует ЭВМ 8 о том, что она закончила передачу информации в блок 28 снятием сигнала запроса на шине 22. После этого ЭВМ 8 выдает синхроимпульсы по шине 20 на считывание информации из блока 28 буферной памяти до тех пор, пока не сравняются коды адресов на входе сумматора 30, после чего на выходах сум- 20 матора 30 и дешифратора 5 минимального кода образуется лЬгический нуль, в результате дешифратор 1 по шине 18 вьщает логический нуль, оповещая ЭВМ

8 об окончании считывания информации 25 с блока 28 буферной памяти и прекращая выдачу синхроимпульсов по шине

20. После этого ЭВМ 8 снимает с шины

6 сигнал ответа и освобождает устройство для обмена для работы по обмену новой информацией между двумя ЭВИ.

Если, например, ЭВМ 8 выставила запрос на шине 19 о начале обмена информацией, то ЭВИ 7 после подготовки выставляет с задержкой сигнал "Готово" на шине 9, дешифратор 1 вырабаты35 вает сигналы на шины 10 и 13, переключающие селектор 12 на прием синхроимпульсов от ЭВМ 8 по шине 20, а селектор 16 — на прием сиихроимпуль40 сов по шине 23, на прием информации через шину 21 и далее через двунаправленные шины (В) приема и выдачи шинного формирователя 11 и его шины (С) выдачи, через селектор 15 на информа- 45 ционные входы коммутатора 26, а выхо-, ды коммутатора 25 подключает через шины (А) приема шинного формирователя 14 (информации) и через его двунаправленные шины (В) приема и вьща-: 50

- чи, через шины 24 на информационные входы ЭВМ 7. Дальше работа устройства для обмена протекает аналогично.

Формула изобретения

Устройство для сопряжения двух ЭВМ, содержащее счетчик записи и счетчик считывания, группы выходов которых соецинены соответственно с первой группой информационных входов сумма-.6ра и группой адресных входов коммутатора вывода информации, бпок буферной памяти, дешифратор управляющих сигналов, первьвг, второй информационные входы которого подключены соответственно к выходам дешифратора максимального кода и дешифратора минимального кода, группы входов которых соединены с группой выходов сумматора, второй группой информационных входов подключенного через группу элементов НЕ к группе выходов счетчика считывания, о т л и ч а ю ц е е с я тем, что,с целью сокращения аппаратурных затрат устройства, в него введеньг три селектора импульсов, коммутатор ввода информации и два шинных формирователя, рричем группа информационных входов и группа выходов коммутатора вывода информации соединены соответственно с группой выходов блока буферной памяти и группами информационных входов первого и второго шинных формирователей, управляюцие входы которых соединены соответственно с первым и вторым выходами дешифратора управляющих сигналов, а группы выходов — соответственно с первой и второй группами информационных входов первого селектора импульсов, группой выходов подключенного к группе информационных входов коммутатора ввода информации, группа адресных входов и группа выходов которого соедичены соответственно с группой выходов счетчика записи и группой информационных входов блока буферной памяти, счетные входы счетчика записи и счетчика считывания подключены соответственно к выходам второго и третьего селекторов импульсов, первые и вторые информационные входы которых являются соответствующими входами устройства для подключения к выходам синхроимпульсов первой и второй ЭВИ, а управляюцие входы соответственно соединены с вторым и первым выходами дешифратора управляющих сигналов, третий и четвертый выходы которого являются соответствующими выходами устройства для подключения к входам разрешения первой и второй ЭВМ, а третий и четвертый информационные входы являются соответствующими входами устройства для подключения к выходам ответа второй и первой ЭВМ, первый выход дешифрато1559351

4 ®8. 1

Корректор Т.Палий

Заказ 838 Тираж 561 Подпис кое

ВНИИПИ Государственного комщ ета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101 ра управляющих сигналов соединен с управляющим входом первого селектора импульсов, группы входов-выходов первого и второго шинных формирователей

Составитель В.Вертлиб

Редактор И.Цулла Техред M.Õîäàíè÷ являются соответствующими группами входов-выходов устройства для подключения к информационным шинам первой и второй ЭВМ.