Устройство для регистрации однократных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике, в частности к регистрации на экранах ЭЛТ импульсных сигналов, и может быть использовано для индикации различных сигналов, например, при проведении испытаний на одиночные удары. Целью изобретения является повышение точности регистрации. Поставленная цель достигается тем, что в устройство содержащее блок 1 нормирования по амплитуде и длительности, состоящий из двух масштабирующих усилителей 2 и 4, программируемого делителя 8 частоты, а также аналого-цифровой преобразователь 9, тактовый генератор 12, счетчик 10 адреса, блок 11 памяти, индикатор 15 на ЭЛТ, дополнительно введены две шины сведения, генератор 16 действительного максимума, триггер 20 разрешения счета, двоичный счетчик 21, элемент НЕ 19, элемент ИЛИ 18 и триггер 22 готовности. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

Щ)5 G 09 С /08

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЬГГИЯМ

ПРИ ГКНТ СССР опиодние изоеретени1, """

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4342422/24-21 (22) 14. 12.87 (46) 23,04.90. Бюл. У 15 (72) И.А.Коченов и Б.А.Максимов (53) 621.317(088.8) г (56) Авторское свидетельство СССР

У 1275519, кл. G 09 С 1/08, 1986. (54) УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ОДНОКРАТНЬ)Х СИГНАЛОВ (57) Изобретение относится к изме- . рительной технике, в частности к регистрации на экранах ЭЛТ импульсных сигналов, и может быть использовано для индикации различных сигналов, .например, при проведении испытаний на. ЯУ, 155 7 А1

2 одиночные удары. Целью изобретения является повышение точности регчстрации. Поставленная цель достигается тем, что в устройство, содержащее блок 1 нормирования по амплитуде и длительности, состоящий из двух масштабирующих усилителей 2 и 4, программируемого делителя 8 частоты, а также аналого-цифровой преобразователь 9, тактовый генера-ор 12, счетчик 10 адреса, блок 11 памяти, индикатор 15 на ЭЛТ, дополнительно введены две шины сведения, генератор

16 действительного максимума, триггер 20 разрешения счета, двоичный счетчик 21, элемент НЕ 19, элемент

ИЛИ 18 и триггер 22 готовности. ил.

1559373

Изобретение относится к измерительной технике, а именно к регистрации на экране электронно-лучевой трубки (ЭЛТ) импульсных сигналов, и может быть использовано для индикации различных сигналов, преобразуемых в электрический вид, например, при проведении испытаний на одиночные удары.

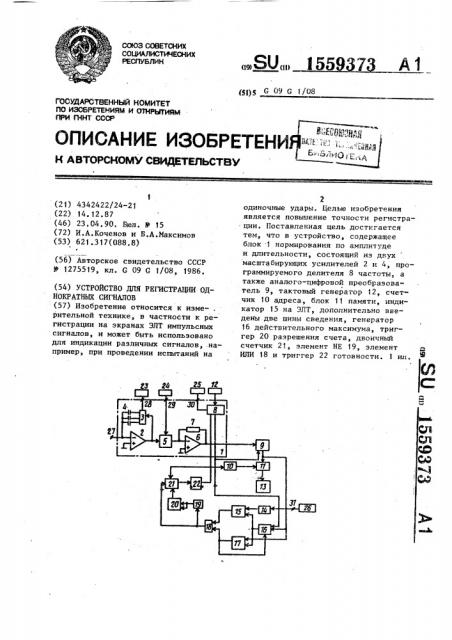

Цель изобретения — повышение точности регистрации, На чертеже изображена структурная схема предлагаемого устройства.

Поставленная цель достигается за счет того, что в устройство, содержащее блок нормирования по амплитуде и длительности, состоящий из двух масштабирующих усилителей и программируемого делителя частоты, аналого-цифровой преобразователь (АЦП), 20 тактовый генератор, счетчик адреса, блок памяти и индикатор на ЭЛТ, введены две шины сравнения, регистр дей-, ствительного максимума, регистр

0,5 А, где А — максимальное значение 25 амплитуды, которое может быть получено -с АЦП, триггер разрешения сче" та,двоичный счетчик на И разрядов,где

N — выбирается из общей емкости памяти (емкость блока памяти 2 слов), ЗО

34+1 элемент HE элемент ИЛИ и триггер готовности.

Выход элемента HE соединен с выходом элемента ИЛИ и вторым входом счетчика .N первый вход которого 35 соединен с выходом триггера разрешения счета, третий вход — с выходом программируемого делителя частоты, а выход — с входом триггера готовности, выход которого соединен с вто- 40 рым входом программируемого делителя частоты. Первый вход элемента ИЛИ соединен с выходом первой схемы сравнения, первый вход которой соединен с выходом регистра 0,5 А, а вто- 45 рой вход с выходом регистра действительного максимума и вторым входом второй схемы сравнения, первый вход которой соединей с выходом АЦП и первым входом регистра действительного 50 максимума, а выход с вторым входом элемента ИЛИ и третьим входом регистра действительной амплитуды, второй вход которого соединен с выходом программируемого делителя частоты; 55 !

В результате введения блоков .и новых связей осуществляется регистрация максимума импульсного сигнала и запись в блок памяти информации о самом импульсном сигнале, его предыстории и последейстний. Определение максимума позволяет устранить ложные срабатывания, чем повышается точность регистрации, а запись всей информации в одну память позволяет отказаться от памяти предыстории импульсного сигнала, что приводит к уменьшению элементных затрат.

Известный регистратор параметров ударных ускорений 15ИЭУ-906 содержит специальную память предыстории импульсного = игнала и определяет начало регистрации по превышению сигналом уровня О, 1 А, что приводит к снижению точности работы и увеличению элементных затрат.

Устройство содержит блок 1 нормирования входного сигнала по амплитуде и длительности, состоящий из первого масштабирующего усилителя 2, ключа 3, масштабирующих конденсаторов 4, аттенюатора 5, второго масштабирующего усилителя 6, резистора 7 обратной связи и программируемого делителя 8 частоты, АЦП 9, счетчик

i0 адреса, блок 11 памяти, генератор

12 тактовых импульсов (ГТИ), индикатор 13 на ЭЛТ, регистр 14 0 5 А, первый блок 15 сравнения, регистр 16 действительного максимума, второй блок 17 сравнения, элемент ИЛИ 18, элемент НЕ 19, триггер 20 разрешения счета, счетчик 21, триггер 22 готовности, задатчик 23 порядка, задатчик 24 числа, задатчик 25 длительности, задатчик 26 0 5 амплитуды, информационный вход 27, входы "Порядок масштаба" 28, "Число масштабов"

29, 11Длительность повторных отсчетов

30, "0 5 амплитуды" 31.

При этом блок 1 нормирования входного сигнала по амплитуде и длительности содержит последовательно соединенные первый масштабирующий усилитель 2 .с ключом 3 и блоком масштабирующих конденсаторов 4 в цепи его обратной связи, аттенюатор 5 и второй масштабирующий усилитель 6 с резистором 7 в цепи обратной связи, а также программируемый делитель 8 частоты. Второй масштабирующий усилитель 6 блока 1 соединен с АЦП 9, а программируемый делитель 8 частоты блока 1 соединен с ГТИ !2, с триггером 22 готовности, с АЦП 9, со счетчиком 21 и со счетчиком 10 адре5 са и с входом регистра 16 действительного максимума, выход АЦП 9 через блок 11 памяти соединен с индикатором 13 на ЭЛТ, с вторым входом регистра 16 действительного максг ума и с входом второго блока 17 сравнения, выход регистра 14 0,5 А соединен с одним иэ входов первого блока

15 сравнения, второй вход которого объединен с вторым входом второго, блока сравнения и подсоединен к выходу регистра 16 действительного максимума, а выходы блоков 15 и 17 сравнения подключены к входам элемента ИЛИ 18. Кроме того, вьгход второго блока l7 сравнения соединен также с входом регистра 16 действительного максимума, выход элемента ИЛИ

18 подключен к входам элемента НЕ 19 и счетчика 21, выход элемента НЕ 19 соединен с входами триггера 20 разре= шения счета, выход которого соединен со счетчиком 21, выход которого соединен с входом триггера 22 готовности и через счетчик 10 адреса с блоком 11 памяти. Вход 27 блока 1 является информационным входом устройства, вход 28 подключен к задатчику

23 порядка, который переключает ключ

3 блока 1, вход 29 подключен к задатчику числа, т.е, задатчику амплитуды входного сигнала и управляет переключением аттенюатора 5, вход 30 соединен с задатчиком длительности повторения отсчета входного сигнала и соединен с входом программируемого делителя 8 частоты блока 1. Вход

31 является входом задания счета регистру 14 0,5 А и соединен с задатчиком 26 °

Устройство работает следующим образом.

При отсутствии информационного сигнала в блок 11 памяти по адресу, задаваемому счетчиком 10 адреса, записывается код нуля, получаемый с АЦП 9.

Максимальное значение импульсного сигнала определяется вторым блоком 17 сравнения, который сравнивает текущий код, полученный из АЦП 9, с максимальным кодом, полученным ранее и записанным в регистр 16 действительного максимума. Если текущее значение больше предыдущего, второй блок 17 сравнения вырабатывает сигнал,разрешающий запись нового значения в регистр 16 действительного

Информация иэ блока 1 1 памяти выводится на индикатор 13 ЭЛТ, на котором высвечивается регистрируемый процесс.

Масштабирование по длительности осуществляется путем изменения квантования АЦП 9, счетчика 10 адреса с

9373

6 максимума. Если текущее значение меньше предыдущего, то второй блок сравнения выдает сигнал на элемент

ИЛИ 18. Парвллелг..но с вторым блоком

17 сравнения первый блок 15 сравнения сравнивает значение, записанное в регистре 16 действительного максимума с 0,5 А (половиной амплитуды входного сигнала), записанным в регистре !4 0,5 А, и выдает сигнал на элемент ИЛИ 18, если значение действительного максимума превысило 0,5 A. Как только на элементе ИЛИ

i8 появляются оба сигнала, он вырабатывает сигнал, который проходит через элемент НЕ 19 и устанавливает триггер 20 разрешения счета, сигнал с триггера 20 разрешения счета по20 ступает на счетчик N 21. Счетчик N 21

N отсчитывает 2 тактов, которые приходят с программируемого делителя

8 частоты и вырабатывает сигнал,. который устанавливает триггер 22 готовности. Последний запрещает про-. .хождение тактовых импульсов с программируемого делителя 8 частоты и сигнализирует об окончании процесса регистрации.

Вся схема построена таким образом, что если максимум оказался локальным, на счетчик N 21 приходит сигнал сброса и схема ожидает прихода действительного максимума.

Запись в блок 11 памяти происходит циклично, т.е. после записи значения в последнюю ячейку памяти, запись следующего значения происходит в первую ячейку. Так как емкость блока 11 памяти равна 2 или и (2.2, не трудно увидеть, что после

М записи максимального кода и начала работы счетчика N в блок 11 памяти запишется еще 2 значений . Таким обЯ

4 разом, ровно половина емкости блоI ка 11 памяти занята предысторией и началом импульсного сигнала до максимального значения, а вторая половина памяти занята значением импульсного сигнала после максимального значения и последействием.

1559373 помощью программируемого счетчика делителя 8.

Задатчик 23 порядка осуществляет управление ключом 3, который заменяет емкость в цепи обратной связи масштабирующего усилителя 2.!

Нормирование. чувствительности дат чика осуществляется аттенюатором 5, который управляется задатчиком 24 числа.

Формула изобретения

Составитель Л.Сорокина

Редактор Н.Тупица Техред Л.Сердюкова Корректор Л.Патай

Заказ 839 Тираж 387 Подписное

ВНЙИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.Ужгород, ул. Гагарина, 101

Устройство для регистрации однократных сигналов, содержащее блок нормирования по амплитуде и длительности, первый выход которого соединен с информационным входом аналого-цифрового преобразователя, последовательно соединенные счетчик адреса„ блок памяти и индикатор, а также первый триггер, первый блок сравне ния, элементы ИЛИ и НЕ, о т л ич а ю щ е е с я тем, что, с целью повьнпения точности регистрации, в него введены второй блок сравнения, второй триггер, счетчик и. два регистра, причем второй выход блока нор5 мирования соединен с тактовым входом аналого-цифрового преобразователя, с входами счетчика адреса и счетчика и с выходом записи второго регистра, вход первого триггера соединен с выходом счетчика, к входу сброса которого подключены выход элемента ИЛИ и вход элемента НЕ, к разрешающему входу — выход второго триггера, вход которого соединен с выходом.элемента НЕ, входы элемента ИЛИ соединены с выходами двух блоков сравнения и с разрешающим входом второго регистра, первый вход первого блока сравнения соединен с выходом первого регистра, а второй объединен с входом второго блока сравнения и соединен с выходом второго регистра, второй вход второго блока сравнения соединен с информационным входом второго

25 регистра, с выходом аналого-цифрового преобразователя и с входом блока памяти.