Устройство для обнаружения ошибок

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике, а именно к устройствам обнаружения адреса ошибок в запоминающих устройствах с последовательным доступом повышенного быстродействия. Цель изобретения - повышение быстродействия и расширение области применения устройства за счет возможности обработки различных кодов. Устройство для обнаружения ошибок содержит преобразователь 1 кодов, коммутатор 2, блок 3 синхронизации, регистр 4, блок 5 сравнения, счетчик 6, вычислитель 7 адреса пакета ошибки и блок 8 формирования типа ошибки. 6 ил.

СО)ОЗ COBETCHHX

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) . Я,, {51)5 H 03 1"1 13/00, G 06 F 11/00

")ПИ(АНИЕ ИЗОБРЕТЕНИЯ

У ? Г.-)ТИФМЪ СаЗМДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTHPHTHRM

ПРИ ГКНТ СССР ;;: ) 4336929,«24-"", 1 I,87. « .:. «-1 . - .!"1 л «««" -) «е„ ." «т" -. :.ккй ин".Тн 72) И.Н. Андреева, =....- ..:.o куков

С.А, Лескова (53) 681.325{088.8) (56) Авторское свидетельство СССР

1249593, кл. С 11 С 29/00, 1986.

Adi N. Fast burst error-correction

soneme vith fire са).е. - EE). Trans.

o.. Computer, 1984, vol. С-ЗЗ,N- 7, 613-618, fig. 3. с

{57) Изобргтение относится к а::то."1а " ..кг н T»! ) -., пит«»явной т(е»п«т(«;е а $ «,«ен.-.! е-;-п.ото быс;:. „,;с "»пя. 11ел;- soáp:— тения — повьп»ение бк стродействия и расширение облас пн применения устройcTBG s c P.. sos. :.ожностн oбработкн разлн-п«ых -;одев. Устройство для обнар.,«же-:ия оы:бок содержит преобразователь 1 кодов, комм гатор,. блок 3.

; ;.нхрон.-задки,, регистр 4, б,.ток ",: сравi«, вычисли i .:.") . «»;:»ре опт; . ;и и бло ", 8 .: . ::. оо«!« нпя тнп;-. о и б и, 6 ил.

1559414

Изобретение относится к автоматике и вычислительной технике, а именно к устройствам обнаружения адреса ошибок в запоминающих устройствах, и может быть использовано в запоминающих устройствах с последовательным доступом повышенного быстродействия. t Q

Цель изобретечия — повышение быстродействия и расширение области применения устройства за счет возмажиос:-.и обработки различных кодов.

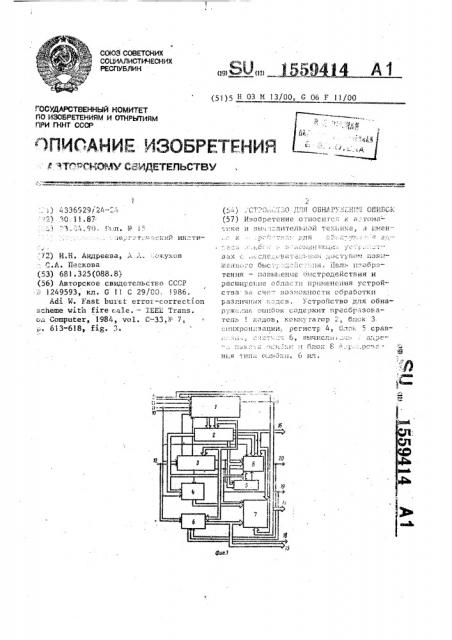

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 функциональная схема коммутатора; на фиг. 3 — функциональная схема блока синхронизации; на фиг. 4 — функциональная схема преобразователя кодов; >,. на фиг. 5 — функциональная схема счечика; на фиг. б — функциональна;. схема блока формирования типа ошибки.

Устройство для обнаружения ошибок (фиг. 1} содержит преобразова- 25 тель 1 кодов, коммутатор 2, блск 3 синхронизации, регистр 4, блок 5 сравнения, счетчик 6, вычислитель 7 адреса пакета ошибок и блок 8,формирования типа ошибки, а также вход 9 выЗЙ бора кода,"информационный вход 10, вход 11 начальной установки, первый 12 и второй 13 управляющие входы, первый 14 — четвертый )7 информационные .выходы и первый 18 — третий 20 управляющие выходы.

Коммутатор (фиг. 2) содержит элементы И-ИЛИ .21-38.

Блок синхронизации (фиг. 3) содер-: жит счетчик 39, дешифраторы 40- 42, элементы .И-ИЛИ 43 и 44, RS-триггеры 45 и 46, элемент НЕ 47 и элемент И 48.

Преобразователь кодов (фиг. 4) содержит дешифратор 49, элементы И-ИЛИ

50-52, элементы ИЛИ 53-55, элементы НЕ 56 и 57, элементы И 58-72, сумматоры 73-84 по мсдулю два, триггеры 85-100.

Счетчик (фиг. 5) содержит элемент НЕ 101, элемент И 102, счетчик 103, элемент И-ИЛИ 104 и триггер 105.

Блок формирования типа ошибки (фиг. 6) содержит элемент ИЛИ-НЕ 106, блок 107 элементов КРИ элементы И 108 "5 и 109 и RS-триггеры 110 и 111.

Устройство работает следующим образом а

Преобразователь 1 кодов в данном конкретном случае реализует кодирование и декодирование кодов Файра, задаваемых полиномами

Р,(х) - (х +1) (х +х+1);

Р (х) = (х +1) (х +х+1);

Р (х) = (х"+1) (х +х +) ).

Количество триггеров соответствует числу контрольных разрядов кода максимальной длины. Сумматоры расположены после триггеров в соответствии нолинамами. Дешифратор 49 испэль:— з..reòñ÷ для переключения преабразовг=

":.àëë на реализацию порэждающего полинома одно" î из трех кодов в соответ..;-нии с входной управляющей информа;:;..ый. Элементы 58-65 и 51 используются для включения обратной связи со" iBcHQ заданному палиному кодав Зле "

;;,";нты 56 н 50 используются дгя пере..:;.;-»чения режимов ксдирава †;:,.-я и декс:,.ьронания .:. х.Вменты t 9-. -„.3 -, и s2 используются для псдачи и";-.форма,;.ии на вход и снятия с выхода сдвигового регистра.

Содержимое сдвигового регистра с выходов триггеров может подаваться на вход коммутатора 2, в котором происходит его деление на части в ссо=-ветствии с кодом.

Таким образом кодир ванина дирование инфср ь:: Bü з уст .ойе не изводится на основе к-да, задавае": -э полинамом с, 1

Р / 1, 4-„Д1 1 (х) .vгпаHноyг". л .=тепени;в.

Г»= :во -"э зьг с и, х - эв- дэ r - +m Кгт ч пранляет ошибк pBs чаностью Ь ж: а

В основе работы устр йства лежь:; разбиение информационной последовательности на сектора по с-разрядов, Ф

При обнаружении места расположения ошибки вычисляется не номер первого из пакета ошибочного разряда, а номер

J сектора, содержащего ошибку и номер первого ошибочнога разряда j s сек= "Оре, Положение пакета аллбки В сек Gре и номер Ошибачиага сектора Оп ределяются не более, чем за (с-1)тактов сдвига регистра в преабразана- теле 1 при помощи математических преобразований в вычислителе 7.

Перед приемом информации при кодировании и декодировании па входу 11 начальной уста .звки происходит абну;уение ъ"-, =Р-- - 4 .=-7дъ а Р" Ф ъбразФър"" "

К Ц:1Ю я»

: mcdP (х), rye Р< (х) — непрнводимый полином çàданного кода (выбор Р,(х) происходи пр.: подаче уп30 равляющего кода на вход вычислителя 7 с входа 9 устройства);

8,(х) — содержимое регнстга 4; о х) картина пакеT a . ): 1 "ç l

3 — содержимое сч 1 ч1 ;-. I l

Функция SP;(x) определ. --:т с;..нбо н;»й сектор кодового словa, В лхоь-а

В;»числителя 7 код ошнб.- .н" . с. K «ра ,подается на информационн= — .=ы:.i дь1

"-.: —: гьей груп11ь1 устройс .-а, -;др".с .. и-.—

40 кета с шибок внутри сек тup : op ае1 ся на информационные выходы 15 стрсйства. Картина пакета ошибок 5 к) подается на информационные Выходы !6 устройства.

Таким образом, обнаружение пакета сшибок и определение его расположения происходит не более чем за (с-1)тактов вместо и тактов, что создает

50 положительный эффект.

5 15 ля I, сбрасываются блок 3 синхрони:зации, регистр 4, счетчик 6, блок 8 формирования типа ошибки. На входы 9 подается информация для управления переключением преобразователя I на определенный код.

При кодировании информация по входу 10 поступает в преобразователь I, который осуществляет формирование избыточных разрядов кода путем деления принимаемой информации на полинам

P(x). При этом блок 3 синхронизации

::::.-:;абгтывает синхросерию которая с.:ест;ечивает сдвиг информации в течение и тактов. Первые k тактов (k число информационных разрядов) ипет прием информационных разрядов В сдвиговый регистр при замкнутой обратной связи. По окончании приема сигнал с соответствующего разряда счетчика 39

-, ->е. один из чешнфраторов 40-42, эле. !.-."..-три ер 46 закры » = f l" Элеме11» ." ь;11 50.,- Обр":ная сВЯзь

1.ьзмыкается и получен ::..1е избыточные разряды кода по выходу 17 устройства поступают на запись в накопитель внешней памяти. При декодировании информация от накопителя внешней памяти поступает в преобразователь 1, где снова производится деление на порождающий полином. После того, как будут приняты все п бит, содержимое сдвиго.. >ro регистра {ос:;:аток от -1es ения) ..одается через коммутатор 2 на блок 8

;ормирования типа ошибки. Если все

-."spHpb1 остатка — нулевые, на выходе .;.и1"гера 111 — "О", это означает, что ошибки не произошло. Если хотя бы

:;дин разряд содержит " ", триггер уси» Ф) .:,:=,ae7ãÿ в 1, т.е. В принимаемой информации содержится ошибка. Со,:»жнмое триггеров 96-100 преобразователя через коммутатор 2, образуя первую часть бстатка, подается в ре-гистр 4. Эта передача обеспечивается по истечении и тактов импульсом с выхода элемента И-ИЛИ 43 на регистр 4.

Далее начинается второй этап де1од::.рования - обнаружение места ошиб-..1 и получ ние ее кар ины. С момента ,11...:учения сигнала ошибки идет подсчет синхроимпульсов в счетчике 6. Он продолжается до тех пор, пока не появится следующая ситуация: блок 5 сравнения выработает сигнал совпадения содержимого первой и четвертой частей содержимого регистра сдвига иэ преобразователя 1, а элемент ИЛИ-НЕ эа594!4 6 фиксирует нулевое содержимое третьей части сдвигового регистра. Если этот сигнал не будет получен за с-тактов, где с — степень двучлена в полиноме

Р(х), то на триггере 105 появится сигнал некорректируемой ошибки по выходу 18 устройства. Сигналы с элемента ИЛИ-НЕ I06 и от блока 5 сравнения устанавливают триггер 110 в "!". По этому сигналу: прекращается подсчет синхроимпульсов в счетчике 6; содержимое счетчика 6, определяющее положе.1ие пакета ошибки вну-.рН с=ктс ра, передается в Вычислитель 7; содержимое второй части сдвигового регистра преобразователя 1, которое апределякартнну 11aKe1 a ошибок Ь(x! a TGK жэ содерж мое регистра . с.:гналу

20 корректируемой ошибки псда "тся на вход вычислителя 7, реas нэуюшего фунФ о р м у л а н з о б р е 1 ения

Устройство для обнаружения ошибок, содержащее преобразователь кодов, первый вход которого является информационным входом устройства, блок сравнения, счетчик, первый вход которого является первым управляющим Входом

1559414 устройства, первый выход — первым управляющим выходом устройства, вычислитель адреса пакета ошибки, выходы которого являются первыми информаци- онными выходами устройства, о т л и " ч а ю щ е е с я тем, что, с целью повышения быстродействия и расширения области применения устройства за счет возможности обработки различных кодов, в него введены коммутатор, блок синхронизации, блок формирования типа ошибки и регистр, выходы разрядов котарога соединены с первыми входалм; вы. числителя адреса пакета ошибки, первые выходы преобразователя кодов саЕдинены с первыми входами коммутатора первые выходы которого соединены с первыми входами блока формирования типа ошибки и блока сравнения, выход

20 которого соединен с вторым входом блока формирования типа ошибки„ первый выход которого соединен с первым входом блока синхронизации, вторыми входами счетчика и вычислителя адре- 2 са пакета ошибки и является вторым управляющим выходом устройства, вторые выходы преобразователя кодов соединень1 с вторыми входами коммутатора и блока синхронизации и с третьими входами счетчика, вторые выходы которого соединены с третьими входами вычислителя адреса пакета ошибки и являются вторыми информационными выходами устройства, первый выход блока синхронизации соединен с первым входом регистра, второй выход блока синхронизации - с вторыми входами блока сравнения и третьим входом блока формирования типа ошибки, третий и четвертый выходы блока синхронизации соединены соответственно с вторым и третьим входами преобразователя кодов, вторые выходы коммутатора соединены с вторыми входами регистра, с четвертыми входами блока формирования типа ошибки и с третьими входами блока сравнения, третьи выходы коммутатора соединены с пятыми входами блока формирования типа ошибки., четвертые вы:::ады коммутатора — с щестыл.и входами блока форл:-.,ра,".ания т,- .::.а ош, ::бки-, с "=,,— зертыми входами вычислителя адреса пакета ошибки и являются третьими ин«- pMàöèîííüìè выходами устройства, -:.етвертый вход преобразователя кодов и пятый вход вычислителя адреса паке" та ошибки объединены и являются вхо ;,àìè выбора кода, пятый вход преобразователя кодов является вторым управляющим входом устройства, шестой вход преобразователя кодов и седьмой вход блока формирования типа ошибки, третьи входы блока синхронизации и регистра и четвертый вход счетчика объединены и являются входом начальной установки устройства, второй выход блока формирования типа ошибки соединен с пятым входом счетчика и является третьим управляющим выхода" у. трай:. -в :. третий выход преобразователя кодов я : ляется четвертым информационным вьг:одам устройства, четвер-;ый зход бло:..а

=-инхранизации объеди -.= я с зрв..; дом счетчика.

1 559414 у&. /г

a &48

1559414

1(ra г:.ь г

17

ФиР. 4

1559414

6ФР45 I )

Li Ji»»»»»

Составитель С. Берестевич

Редактор Б. Рогулич Техред А.Кравчук Корректор Л.Патай

Заказ 841 Тираж б62 Подписное

В. ИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб °, д. 4/5

«:м:.: "..-,- ;-.".,=- -;:-д;",гель"и.-" комбинат "Патек", .". Ужгораг, ул, Гага ина, 101

»»