Цифровой групповой приемник многочастотного кода

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике. Цель изобретения - повышение помехоустойчивости и упрощение цифрового группового приемника многочастотного кода. Он содержит блок задающих генераторов 1, коммутатор 2 адресов, блок оперативной памяти 3, формирователь 4 огибающей сигнала, элемент Исключающее ИЛИ 5, элемент ИЛИ 6, счетчик-дешифратор 7 длины пачки, формирователь 8 знака пачки, формирователь 9 сигнала смены знака, блок задержки 10, счетчик-дешифратор 11 интервала между пачками, блоки элементов И 12 и 17, блок счетчиков 13 среднего интервала, блок счетчиков 14 разноса частот, обнаружитель 15 кода и шифратор 16 кода. Цель достигается за счет осуществления одноканального приема многоканального сигнала. 2 ил.

СО1ОЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 04 (1 1 7

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСИОМ,К СВИДЕТЕЛЬСВ ВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

fl0 ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (2l) 4418361/24-09 (22) 04.04.88 (46) 23.04.90. Бюл, Ф 15 (71) Куйбышевский электротехнический институт связи (72) И,С,Брайнина и В,Н.Стрельников (53) 621.395.44 (088 ° 8) (56) Патент ГДР М 214272, кл. Н 04 Q 1/457, 1985. (54) ЦИФРОВОЙ ГРУППОВОЙ ПРИЕМНИК МНОГОЧАСТОТНОГО КОДА (57) Изобретение относится к радиотехнике. Цель изобретения — повышение помехоустойчивости и упрощение цифрового группового приемника мно„„SU„„1559431 А 1

2 гочастотного кода. Он содержит блок задающих г-ров 1, коммутатор 2 адресов, блок оперативной памяти 3 формирователь 4 огибающей сигнала,эл-т

ИСКЛЮЧАЮЩЕЕ ИЛИ .5, эл-т ИЛИ б,счетчик-дешифратор 7 длины пачки,формирователь 8 знака пачки, формирователь 9 сигнала смены знака, блок задержки 10, счетчик-дешифратор 11 интервала между пачками, блоки 12 и 17 эл-тов И,блок счетчиков 13 среднего интервала, блок счетчиков 14 разноса частот, обнаружитель 15 кода и шифратор 16 кода, Цель достигается за счет осуществления одноканального приема многоканального сигнала,2 ил.

1559431

Изобретение относится к радиотехнике и связи и может быть использовано в устройствах приема сигналов набора номера в спектре тональных частот, например, кодом "2 из 6",передаваемых s составе группового 32-канального цифрового потока со скоростью 1024 к бит/с с дельта-модуляцией и слоговым компандированием.

Целью изобретения является повышение помехоустойчивости и упрощение устройства за счет осуществления одноканального приема многоканального сигнала, . 15

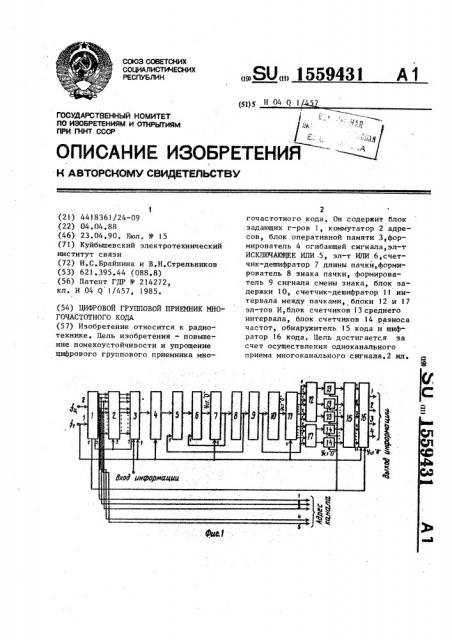

На фиг,l представлена структур-. ная электрическая схема цифрового группового приемника многочастотного кода; на фиг ° 2 — эпюры напряжений, поясняющие работу приемника. 20

Приемник содержит блок 1 задаю" щих генераторов, коммутатор 2 адресов, блок 3 оперативной памяти,формирователь 4 огибающей сигнала,элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5, элемент ИЛИ 6,25 счетчик-дешифратор 7 длины пачки, формирователь 8 знака пачки, формирователь 9 сигнала смены знака, блок

l0 задержки, счетчик-дешифратор il интервала между пачками, первый блок 3р

12 элементов И, блок 13 счетчиков среднего интервала, блок 14 счетчиков разноса частот, обнаружитель 15 кода, шифратор 16 кода и второй блок

17 элементов И.

Приемник работает следующим образом.

На вход приемника, а именно на вход данных блока 3, поступает групповой цифровой поток с тактовой час- 40 тотой 1024 кГц, сформированный путем уплотнения 32 дельта-модулированных сигналов многочастотного кода со скоростью передачи 32к бит/с на канал, Сигналы многочастотного кода "2 из 45

6" передаются при наборе номера комбинациями из двух частот ряда 700, 900, 1100, 1300, 1500 и 1700 Гц в диапазоне уровней порядка 30 дБ с возможным "перекосом" уровней близко отстоящих частот до 3 дБ и далеко отстоящих частот до 10 дБ. Всего может существовать 15 различных комбинаций кода, Дельта-отсчеты каждого из 32-каналов передаются в групповом цифровом потоке последовательно.

Последовательность отсчетов группового цифрового дельта-потока запи" сывается в блок 3 по мере поступления в соответствующие каждому каналу адреса, .Для формирования адресов используются сетки частот 512, 256, 128, 64, 32, 16, 8, 4, 2, 1, 0 5, 0 25 и О, 125 кГц, вырабатываемые в блоке 1 из тактовой частоты 1024 кГц, Для цикловой синхронизации блока 1 на его второй вход поступает импульсная последовательность цикЛовой частоты 8 кГц.

Время обработки отрезка двухчастотного сигнала не должно превышать

10 мс.

Поскольку за время 8 мс должен завершиться полный цикл записи и считывания из блока 3 всей ранее записанной информации, каждый тактовый отрезок времени делится пополам. В первую половину времени происходит запись в блок 3 отсчета сигнала по мере его поступления в реальном масштабе времени по адресу очередного канала, а во вторую половину времени — считывание из блока 3 другого отсчета сигнала по адресу другого канала, который в данный отрезок времени подлежит обработке.

Для формирования нужных адресов блока 3 в режимах записи и считывания информации в приемнике используется коммутатор 2, управляемый по своему второму входу импульсами записи/считывания, В режиме считывания на выходе блока 3 появляется информация, записанная ранее по данному каналу, в виде пачек 1 (импульсов длительностью

0,5 мкс) с частотой 1024 кГц,либо в виде. пачек 0 (отсутствия импуль,сов). либо в виде чередующихся импульсов и пауз (фиг,2б) °

Как следует из фиг.2а, б, области нарастания сигнала (положительной производной) соответствует пачка 1, области убывания сигнала (отрицательной производной) — пачка О, области экстремумов сигнала (малой производительности) - режим молчания - чередующихся последовательность импульсов и пауз, Величина ступеньки квантования (фиг;2а) в дельта-кодере с адаптивным слоговым компандированием устанавливается за время адаптации 10 мс, равное периоду основного тона речи.

Адаптивный шаг определяется средним модулем производной сигнала, которая в свою очередь пропорциональна про-

5 155 изведению амплитуды сигнала на его частоту. В промежутках между длинны/ ми пачками располагаются более короткие пачки 1 или О, а также знакочередующаяся последовательность 1 и О (фиг.2б), В случае двухчастотного сигнала фиг.2в) сигнал промодулирован как по амплитуде, так и по частоте. В области максимумов амплитуды частотная модуляция минимальная и соседние интервалы между нулями следуют со среднеарифметической частотой.Амплитудная и частотная модуляпии сигнала происходят с разностной частотой биений двух частот. Зная среднюю частоту и частоту биений, можнО определить неизвестные частоты кода и распознать одну из 13-ти возможных комбинаций многочастотного кода.

Из-за большого пик-фактора двухчастотного сигнала в области минимумов огибающей шаг квантования оказывается завышенным,, что приводит к потере информации ("провалу"), т,е, в этой области наблюдается режим молчания (фиг.2г).

В результате области максимумов огибающей соответствуют длинные пачки 1 или О, средней области — более короткие пачки 1 или О, прерываемые чередующейся последовательностью 1и

О, области минимумов огибающей— практически полное отсутствие пачек

1 или О и наблюдается только знакочередование (фиг,2д).

Таким образом, вьделяя пачки, 1 или О не короче заданной длины и измеряя интервалы времени между соседними длинными пачками, можно оценить период высокочастотного заполнения сигнала в области максимумов огибающей, т.е. найти среднеарифметическую частоту. Кроме того, измеряя интервалы времени между соседними "провалами" сигнала в области минимумов огибающей, можно найти период разиост1 ной частоты биений, В приемнике счетчик-дешифратор 7 длины пачки настроен на дешифрацию пачек длиной, не меньше 8.

Выделение длинных пачек эквивалентно выделению максимальных значений огибающей. Напротив, выделение областей знакочередования 1 и О,где пачки отсутствуют, равноценно вьделению минимальных значений огибающей, Обработка сигнала в области максиму9431 мов огибающей способствует повышению помехоустойчивости приема,так как отношение сигнал/помеха в этой области максимально, В области минимумов сигнал практически отсутствует иобработке не подвергается, однако информация о периодичности минимумов ("провалов") позволяет найти разнос частот.

С выхода блока 3 в режиме счнтывания цифровой дельта-поток (фиг.2д), несущий информацию о сигнале данного канала, посту ает на информационньщ вход формирователя 4, на тактовый вход которого подана последовательность тактовых импульсов,Формирователь 4 представляет собой Dтриггер, на выходе которого возникает огибающая "пачек" импульсов (фиг,2е) °

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5 вьделяет на своем выходе пачки разного зна20 ка и не реагирует на пачки одного знака, Прн поступлении на входы разных логических уровней, на выходе возникает высокий уровень логической единицы, который по второму входу элемента ИЛИ 6 сбрасывает счетчикдешифратор 7 в ноль. По первому входу элемента ИЛИ 6 также происходит сброс в ноль счетчика-дешифра30

ИЛИ 5. Как видно из диаграмм фиг,2е,ж, работа счетчика-дешифратора 7 разрешена в моменты времени, когда уровни фиг.2е,ж, одинаковы и по входу установки нуля счетчика-дешифратора 7 держится низкий уровень вплоть до достижения счетчиком кода заданной длины.

В моменты времени, когда логические уровни (фиг.2е,ж) разные, на входе установки нуля счетчика-дешифратора 7 поддерживается запрещающий высокий уровень, счетчик находится

55. в состоянии нуля и счета импульсов не происходит.

Благодаря такому построению схемы, на выходе формирователя 8 длительности импульсов получаются равными тора 7 при достижении на его выходе кода, соответствующего заданной длине пачки. В момент достижения кода заданной длины на выходе счетчика35 дешнфратора 7 возникает импульс,поступающий на тактовый вход формирователя 8, представляющего собой счетчик-делитель на 2. Сигнал с выхода

40 Формирователя 8 (фиг.2ж) поступает на первый вход элемента ИСК3%ЧАЮЯЕЕ

1559431 интервалам между соседними длинными пачками импульсов противоположного знака, При этом длинные пачки импуль-" сов одного и того же знака,прерываемые короткими пачками другого знака, на выходе формирователя, 8 не фиксируются, Формирователь 9 выделяет соответственно передние и задние фронты импульсов с выхода формирователя 8 знака пачки (фиг,2з).8 момент смены зйака пачки открывается один из элементов И первого блока 12, номер Которого К соответствует интервалу между пачками импульсов. Это обеспечивается счетчиком-дешифратором 1), на сМетный вход которого поступают тактовые импульсы, В момент смены знака пачки через открытый К-й элемент

И блока 12 информация со счетчикадешифратора 1) переписывается в одновременный счетчик блока 13,накапливающий число интервалов, содержащих К периодов тактовой частоты.йос- 25 ле этого счетчик-дешифратор 11 обнуляется с выхода блока 10 импульсами (фиг.2и), Одновременно с информацией о среднем интервале между пачками в счетчи- 30 ках блока 14 накапливается информация о разностной частоте. Это достигается путем подсчета счетчиками разноса частот числа провалов той или иной длительности, фиксируемых на выходах того или иного открытого элемента И блока 17. Гаким образом, более длинные интервалы между пачками импульсов должны быть отнесены к провалам в области минимумов 40 двухчастотного сигнала (фиг,2в,г), Фиксируя длительности "провалов", открывающих элемент И блока 17 и подсчитывая их количество счетчиками блока 14, можно оценить разнос частот.

Информация о среднем интервале между пачками с выходов блока 13 и о числе провалов заданной длительности с выходов блока 14 поступает в конце интервала времени анализа на обнаружитель 15. На одном из 15-ти выходов обнаружителя 15 появляется высокий логический уровень, поступающий на шифратор 16, В зависимости от адреса выхода об55 наружителя 15, на котором появился высокий уровень, счетчик

1 ° адреса шифратора 16 останавливается.

При этом на выходе шифратора 16 устанавливается четырехразрядный двоичный код, соответствующий номеру одной из ) 5-ти передаваемых комбинаций.

Формула изобретения

Цифровой групповой приемник многочастотного кода, содержащий блок задающих генераторов, блок счетчиков среднего интервала и блок счетчиков разноса частот, о т л и ч а ю щ .и йс я тем, что, с целью повышения помехоустойчивости и упрощения приемника за счет осуществления одноканального приема многоканального сигнала, введены коммутатор адресов, блок оперативной памяти, первый и второй блоки элементов И, обнаружитель кода, шифратор кода и последовательно соединенные формирователь огибающей сигнала, элемент ИСКЛИИАЮЩЕЕ ИЛИ, элемент ИЛИ, счетчик-дешифратор длины пачки, формирователь знака пачки, формирователь сигналов смены знака, блок задержки и счетчик-дешифратор интервалов между пачками, первые и вторые выходы которого подключены к первым входам соответственно первого и второго блоков элементов И, вторые входы которых объединены и подключены к выходу формирователя сигналов смены знака, вход которого объединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ, а второй вход элемента ИЛИ соединен с выходом счетчика-дешифратора длины пачки, тактовый вход которого объединен с тактовыми входами шифратора кода, счетчика-дешифратора ин" тервалов между пачками, формирователя огибающей сигнала, блока оперативной памяти и блока задающих генераторов, выходы которого через коммутатор адресов подключены к входам блока оперативной памяти, вход записи-считывания которого объединен с управляющим входом коммутатора адресов и подключен к первому управляющему выходу блока задающих генераторов, второй управляющий выход котороFo подключен к объединенным входам сброса блока счетчиков среднего интервала, блока счетчиков разноса частот и шифратора кода, входы которого через обнаружитель кода подключены к соответствующим выходам блока счетчиков среднего интервала и блока счетчиков разноса частот, причем выход блока оперативной памяти подключен к входу формирователя огибающей сигнала.

Составитель В,йевцов

Техред А.Кравчук Корректор А.06ручар

Редактор Н.Рогулич

Заказ 842 Тирах Я9 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

1 13035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101