Функциональный преобразователь полинома третьей степени

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в измерительных устройствах с аппаратурной реализацией функции преобразования. Цель изобретения - повышение быстродействия. Функциональный преобразователь полинома третьей степени содержит три вычислительных блока, блок управления, элементы 2 И-ИЛИ-НЕ, 2 И-ИЛИ, ИЛИ, три формирователя импульсов, счетчик результата, каждый вычислительный блок содержит элементы И-НЕ, И, 2И-ИЛИ-НЕ, два реверсивных счетчика, вычитающий счетчик, два триггера и формирователь импульсов. Цель достигается в основном за счет совмещения реверсивными счетчиками функций преобразователя код-интервал времени и запоминающего устройства, а также параллельного и ускоренного формирования членов полинома и выполнения в счетчике результата операций, эквивалентных умножению опорной частоты. 1 з.п. ф-лы, 2 ил.

СОЮЗ СОВЕТСНИХ

3 ЙЛ

PECAVSЛИН (19) (111 (уцди G 06 У 7J552

ОЛИСАНИЕ ИЗОБРЕТЕНИЯ

Н АSTOPCHÎMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР.1 (21) 4459! 35/24-24 (22) 12.07.88 (46) 07.05.90. Бюл, У 17 (71) Харьковский политехнический институт им. В.И.Ленина (72) И.В.Кривогин (53) 681.325(088.8) (56) Авторское свидетельство СССР !! 851405, кл. G 06 I 7/552, 983.

Смолов В.Б. Функциональные преобразователи информации.- Y. Энергия, 1981, с. 144-145. (54) ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

ПОЛИНОИА ТРЕТЬЕЙ СТЕПЕНИ (57) Изобретение относится к вычислительной. технике и может быть использовано в измерительных устройствах с анпаратурной реализацией функции преобразования. Цель изобретения — повыИзобретение относится к вычислительной технике. и может быть исполь. зовано в измерительных устройствах с аппаратурной линеаризацией Функции преобразования, Целью изобретения является повышение быстродействия.

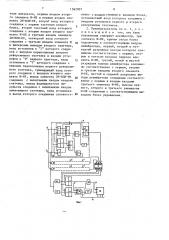

На фиг. l представлена блок-схема преобразователя! на Фиг.2 — схема блока управления.

Преобразователь содержит элементы И-НЕ 1 и 2, элемент 2И-ИЛИ-HE 3, элемент И 4, триггер 5, формирователь 6 импульсов, реверсивные счет чики 7 и 8, триггер 9, вычитающий счетчик 10, блок 11 управления, элемент 2И-ИЛИ-НЕ 1 2, элемент 21 -ИЛИ 13, 2 шение быстродействия. Функциональный преобразователь полинома третьей степени содержит три вычислительных блока, блок управления, элементы 2И-ИПИНЕ, 2И-ИЛИ, ИЛИ, три формирователя импульсов, счетчик результата, каждый вычислительный блок содержит элементы И-НЕ, И, 2И-ИЛИ-НЕ, два реверсивных счетчика, вычитающий счетчик, два триггера и формирователь импульсов.

Цель достигается в основном за счет совмещения реверсивными счетчиками функпий преобразователя код — интервал времени и запоминающего устройства, а также параллельного и ускоренного Формирования членов полинома и выполнения в счетчике результата операций, эквивалентных умножению опорной частоты. 1 з.п.ф-лы, 2 ил.

С: формирователи 14 и 15 импульсов, элемент ИЛИ 16, Формирователь 17 импульсов, счетчик 18 результата, вычислительные блоки 1 9-21. Блок управления (фиг.2) содержит дешифратор 22 и элементы И-НЕ 23-25.

Преобразователь работает следующим образом.

Перед началом преобразований полинома вида N < = Ах + Вх + Сх + D, где х = Т,/Т, в первый и второй реверсивные счетчики заносятся коды коэффициентов А, В, С, в счетчик 18 результата — код коэффициента D, а в вычитающие счетчики I 0 — коды соответствующих степеней.

1 562907

Работу Функционального преобразователя полинома третьей степени рассмотрим иа примере работы вычисли ;ельного блока 1 9 ° Выбирают коэффициенты А>-В С. Периоды следования Т» и Т выбираются иэ соотношения Т,(Т»а УТ

В исходном состоянии первый и второй триггеры находятся в нулевом 10

6остоянии. Единичный потенциал с инерсного выхода первого триггера 5 открывает пб первому входу элемент

Й-НЕ 1, единичный потенциал с инверс ного выхода второго триггера 9 по 15 четвертому входу — элемент 2И-ИЛИ-НЕ

3,а единичный потенциал с третьего выхода блока 11 управления по четвертым входам — элементы 2И-ИЛИ 13 и 2И-ИЛИ-НЕ

12, входные импульсы с периодом сле- 20 ,дования Т» поступают на вычитающий

Эход первого реверсивного счетчика 7, а импульсы с периодом следования Т

isa вычитающий вход второго реверсивного счетчика 8, вход первого (млад- 25 шего) разряда и через элемент ИЛИ 1 6 йа вход второго разряда счетчика 18, что соответствует утроению частоты

По входу первого разряда счетчика 18 результата. 30

Первым переполняется второй реверсивный счетчик 8. В результате переполнения с выхода отрицательного переноса поступает импульс на входы второго 9 (изменяет ".,. его состояние) и первого 5 (подтверждает его состояние)

Триггеров. Нулевой потенциал с инверсного выхода второго триггера 9 закрывает по четвертому входу первый

Элемент 2И-ИЛИ-НЕ 3 и открывает по 40

Третьему входу элемент И 4, импульсы

Тц начинают поступать на суммирующий вход второго реверсивного счетчика 8 до момента отрицательного переполнения первого реверсивного счет- 45 чика 7.

Таким образом, в первом такте работы Функционального преобразователя нз А.импульсов с периодом следования

Т, Формируется временной интервал

АТ», который одновременно квантуется . опорными импульсами с периодом следования Т, в результате чего формируется число-импульсный код

К АТ /То А

Соответственно, в блоке 20 Формируется код В„, в бло»»е 21 - С . Счет

Импульсов утроенной частотой F в с четчике 18 результата продолжается. до момента обнуления реверсивного счетчика 7 третьего вычислителънога блока 21, В резуьтате обнуления вычитающего счетчика 10 блока 21 с его выхода отрицательного переноса поступает импульс на третий вход блока 11 управления. Сигнал с третьего выхода блока 11 управления закрывает по четвертым входам элементы 2И-ИЛИ НЕ 1 2 и 2И-ИЛИ 13, а сигнал с второго выхода блока 11 управления открывает. по первому входу элемент 2И-ИЛИ 13, и им" пульсы с периодом Т через элемент

ИЛИ 16 поступают на старшие разряды счетчика 18 результата, что соответствует удвоению частоты по входу первого разряда счетчика )8 результата.

Во втором такте работы импульс переполнения первого реверсивного счетчика 7 переводит первый триггер

5 в единичное состояние, т.е. нулевой потенциал. инверсного выхода этого ,триггера открывает по первому входу элемент И-HE 2, и на суммирующий вход ервого реверсивного счетчика 7 начинают поступать импульсы опорной частоты, открывается по первому входу первый элемент 2И-ИЛИ-НЕ 3 и на вычи-. тающий вход второго реверсивного счетчика 8 начинают поступать импульсы входной частоты до переполнения второго реверсивного счетчика 8. Во втором такте Формируется временной интервал N»T», который квантуется импульсами опорной частоты, число которых .

Ы Х Т /T+ = N< z z= Ax, Аналогично во втором преобразователе степенной Функции формируется код Вх

Поступление опорных импульсов на старшие разряды счетчика 18 результата продолжается до отрицательного переполнения вычитающего счетчика

10 второго блока 20. В результате обнуления счетчика 10 второго вычислительного блока 20 с его выхода отрицательного переноса поступает импульс на второй вход блока 11 управления. Сигнал с второго выхода блока

11 управления закрывает по первому входу элемент 2И-ИЛИ 13, а сигнал с первого выхода блока 11 управления открывает по первому входу элемент

2И-ИЛИ-НЕ 12 и опорные импульсы по07

5 15629 ступают на в од первого разряда счетчика 1 8 результата. Поступление импульсов на вход первого разряда счетчика 18 результата продолжается до момента переполнения вычитакщего счетчика .1 0 первого блока 9.

В третьем такте работы импульс переполнения второго реверсивного счетчика 8 поступает на вход первого триггера 5 и единичный потенциал с его инверсного выхода открывает по первому входу первый элемент И-НЕ нулевой потенциал на выходе вто >ого триггера 9 открывает по третьему входу элемент И 4.

Таким образом, на вычитающий вход первого реверсивного счетчика 7поступают импульсы входной частоты, на суммирунщий вход второго реверсивно- 20

ro счетчика 8 — импульсы опорной частоты до переполнения первого реверсивного счетчика 7. Импульс отрицательного переполнения проходит через первый Формирователь на вычитакщий 25 вход вычитающего счетчика 10 и на его выходе появляется и;пульс отрицательного переполнения, поступающий на первый вход блока 1! управления.

При этом первый вычислительный блок !9 фиксирует число импульсов

И =Ах

В счетчике !8 результата Фиксирует-, ся число импульсов, равное Ах + Вх + а

+Сх + D. В моменты окончания работы соответствующих вычислительных блоков блок ll управления выдает команду запрета на их работу, например на К-входы реверсивных счетчиков 7 н 8 (не показа- 40 йы) .

Формула изобретения

1 . Функциональный преобразователь 45 полинома третьей степени, содержащий первый вычислительный блок и блок управления, причем вход первой тактовой последовательности преобразователя соединен с первым тактовым входом пер- S0 вого вычислительного блока, второй тактовый вход которого соединен с входом второй тактовой последовательности преобразователя, первый вычислительный блок содержит элемент И, пер- у вый элемент И-НЕ, первый и второй реверсивные счетчики, первый вход элемента И соединен с первым входом первого элемента И-НЕ, второй вход которого соединен с первым тактовым входом первого вычислительного блока, второй тактовый вход которого соединен с вторым входом элемента И, о тл и ч а ю шийся тем, что, с целью повышения быстродействия, в него введены второй и третий вычислительные блоки, с первого.по третий формирователи импульсов,,элемент 2И-ИЛИНЕ и элемент 2И-ИЛИ, элемент ИЛИ и счетчик результата, причем выходы с первого по третий вычислительных блоКоВ соединены с входами соответственно признаков переполнения с первого по третий блока управления, вход первой тактовой последовательности преобразователя соединен с первыми тактовыми входами второго и третьего вычислительных блоков, вторые тактовые входы которых соединены с входом второй тактовой последовательности преобразователя и входами первого и второго Формирователей импульсов, первый и второй выходы блока управления

- соединены с первыми входами соответственно элементов 2И-ИЛИ и 2И-ИЛИ-НЕ, вторые и третьи входы которых соединены с выходами соответственно первого и второго формирователей импульсов, третий выход блока управления соединен с четвертыми входами элементов

2И-ИЛИ и 2И-ИЛИ-НЕ, выходы которых соединены соответственно с первым входом элемента ИЛИ и счетным входом первого разряда счетчика результата, инверсный выход которого соединен с входом третьего Формирователя, выход которого соединен с вторым входом элемента ИЛИ, выход которого соединен со счетным входом второго разряда счетчика результата, входы с третьего по нулевой коэффициентов полинома преобразователей соединены с установочными входами соответственно первого, второго, третьего вычислительных блоков и счетчика результата, выход которого соединен с выходом преобразователя, входы кодов с третьей по первую степеней преобразователя соединены с входами степени соответственно спервого по третий вычислительных блоков, причем в KG blA вычислительный блок введены второй элемент И-НЕ, элемент

2И-ИЛИ-НЕ, первый и второй триггеры, формирователь импульсов и вычитающий счетчик, первый вход первого элемента И вЂ” НЕ соединен с инверсным выходом первого трш гера, входом формирова!

562907 теля импульсов, первым входом второ,го элемента И-НЕ и первым входом элемента 2И-ИЛИ-НЕ, второй вход которого соединен с первым тактовым входом блока„ второй тактовый вход которого . соединен с вторым входом второго элемента И-HE и третьим входом элемента

2И-ИЛИ-HE четвертый вход которого соединен с третьим входом элемента И и инверсным выходом второго триггера, вход установки в ".3" "которого соединен с выходом переполнения второго реверсивного счетчика и нходрм установки и О" первого триггера, вход установки н "J" которого соединен с выходом переполнения первого реверсивного счетчика, суммирукчций вход которого соединен с выходом второго элемента И-НЕ, выход элемента 2И-ИЛИ-НЕ соединен с ньиитакщим входом второго счетчика, выход формирователя импульсов соединен с нычитающим входом нычитавщего счетчика, вход установки и выход которого соединены соответст-.25 ненно с входом степени и выходом блока, установочный .вход которого соединен с входами установки первого и второго ренерсивных счетчиков.

2. Преобразователь по и. l, о т лич аюmий с я тем, что блок управления содержит дешифратор, трн элемента И-НЕ, причем входы блока подключены к соотнетстнукицим входам дешийратора, первый, второй и четвертый разрядные выходы которого соединены соответственно с первым, вторым и третьим вкодамн перного элемента И-НЕ, третий, пятый и шестой разрядные выходы деши4ратора соединены соответственно с первым, вторым и третьим входами второго элемента

И-НЕ, шестой и седьмой разрядные выходы деши4ратора соединены соответственно с первым и вторым входами третьего элемента И-НЕ, выходы первого, второго н третьего элементов

И-HE соединены с соответствующими выходами блока управления, ) 562907

Составитель А. Зорин

Техред Л.Сардюкова . Корректор М.Самборская.

Редактор И. П!улла

Тираж 558

Подписное

Заказ 065

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, !!осква, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101