Устройство для имитации сбоев и неисправностей цифровой вычислительной машины

Иллюстрации

Показать всеРеферат

Изобретение относится к средствам вычислительной техники и может быть использовано при наладке оборудования и отладке программ. Цель изобретения - повышение надежности устройства за счет исключения несанкционированных сигналов на его выходе, а также расширение области применения. Устройство содержит блоки 1 и 2 дешифрации начальных и конечных условий, триггеры 3 - 5 и элемент И 6. Возможно применение устройства в синхронных и асинхронных процессах, поскольку время действия неисправности не определяется заранее числом тактов ЭВМ. 2 ил.

СОЮЗ ОСОЕТСНИХ И

РЕСПУБЛИК (19) (И) (g1)g С 06 F 11/26

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTHPHYHRM

ПРИ ГКНТ СССР

К А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ (21) 4455781/24-24 (22) 1 9.07,88 .(46) 07.05.90. Бюл. Х - 17 (75) A.C.Ïîòàïoâ и Л.Н.Веселова (53) 681.3(088.8) (56) Авторское свидетельство СССР

Р 1016787, кл. G 06 F 11/26, 1 982.

Авторское свидетельство СССР

М 1265779, кл. G 06 F 11/26, 1985. .(54) УСТРОЙСТВО ДЛЯ И 1ИТАЦИИ СБОЕВ И

НЕИСПРАВНОСТЕЙ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ ИАШИНЫ (57) Изобретение относится к.средствам вычислительной техники и может быть использовано при наладке оборудования и отладке программ. Цель изобретения — повышение надежности устройства за счет исключения несанкционированных сигналов на его выходе, а также расширение области применения.

Устройство содержит блоки I и 2 дешифрации начальных и конечных условий, .триггеры 3-5 и элемент И 6. Возможно применение устройства в синхронных и асинхронных процессах, поскольку время действия неисправности не определяется заранее числом тактов

ЭВИ, 2 ил.

156291 9

Изобретение относится к средствам вычислительной техники и может быть использовано при отладке оборудования н программ, а также для обучения перСонала, занятого техническим обслуживанием ЭВМ, приемам диагностирования вычислительной системы при возникнове-! нии сбоев и отказов в процессе работы вычислительной системы, 10

Целью изобретения является повыение надежности работы устройства за чет исключения несанкционированных сигналов на его выходе и расширение

Его области применения за счет возможности имитации сбоев IJBN при асинхронных режимах работы.

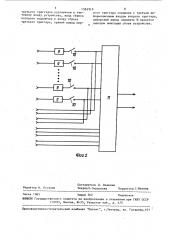

На фиг. 1 приведена общая схема устройства для имитации сбоев и нейсправностей цифровой вычислительной 20 машины, на Фиг . 2 — схема "блока дешифрации конечных условий имитации.

Устройство (фиг.1) содержит блоки дешифрации начальных 1 и конечных 2 условий имитации, первый 3, второй 4, 25 третий 5 триггеры, элемент И 6, тактовый вход 7 и вход 8 сброса устройства.

Блок 2 (фиг.2) содержит элементы НЕ 9, переключатели 1 О и элемент

И 11.

Устройство работает следующим образом, В исходном состоянии переключатель цепи сброса находится в положении "Земля". Все триггеры устройстВа приведены в исходное состояние.

Йа выходе элемента 6 присутствует лоГическая единица. На входе блоков 1 и 2 коммутируются выбранные сигналы

40 из доступных для подключения цепей

ЦВМ. Выход элемента И 6 подключается

К подавляемому сигналу или к другому формирователю сигнала неисправности.

Тактовый вход 7 коммутируется с сигналами неподавляемой тактовой серии, ЦВМ. Переключатель цепи сброса устройства переводится в положение "Обрыв". Таким образом, триггеры могут сработать при поступлении на их входы информационных сигналов. Триггер

5 устанавливается в "1", если во время переключения цепи сброса устройства блок 1 дешифрации начальных условий и блок 2 дешифрации конечных условий не распознают ни начальных, ни конечных условий срабатывания, что предотвращает несанкционированное включение или выключение элемента

И 6. После установки триггера 5 при условии распознавания блоком 1 начальных условий срабатывания триггер

3 устанавливается в "1" и на выходе элемента 6 появляется логический "О", что соответствует началу действия неисправности.

Триггер 4 устанавливается в "1" ("О". — на инверсном выходе) после установления триггеров 3 и 5 при условии, что блок 2 распознает конечные условия срабатывания и переклю-. чает элемент 6 (на выходе элемента

И 6 логическая единица), что соответствует концу действия неисправности. формула и з о б р е т е н и я

Устройство для имитации сбоев и неисправностей цифровой вычислительной машины, содержащее блок дешифрации начальных условий имитации, блок дешифрации конечных условий имитации, первый и второй триггеры, элемент И, причем входы блоков дешифрации начальных и конечных условий имитации являются информационными входами устройства, первый выход блока дешифрации начальных условий имитации соединен с первым информационным входом первого триггера, первый выход блока дешифрации конечных условий имитации соединен с первым информационным входом второго триггера, инверсный выход которого и прямой выход первого триггера соединены соответственно с первым и вторым входами элемента И, « вход сброса ус тройс тв а подключен к входам сброса первого и второго триггеров, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности работы устройства за счет исключения несанкционированных сигналов на его выходе и расширения его .области применения за счет возможности имитации сбоев ЦВМ при асинхронных режимах работы, оно содержит третий триггер, прямой выход которого соединен с вторыми информационными входами первого и второго триггеров, первый и второй информационные входы третьего триггера соединены с вторыми выходами соответственно блока дешифрации начальных условий имитации и блока дешифрации конечных условий имитации, входы синхронизации первого, второго и

QU2 Z

Составитель Д. Ванюхин

ТехредЛ,Сердюкова Корректор С, Шекмар

Редактор Н. Рогулич

Заказ 1065 Тираж 562 Подп ис но е

ВНИИПИ Государственного комитета по изобретениям н открытиям при ГКНТ СССР

113035, Москва, Ж-35 ° Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина, 101

5 1 56291 третьего триггеров подключены к тактовому входу устройства, вход сброса которого подключен к входу сброса третьего триггера, прямой выход перS

9 6 вого триггера соединен с третьим информационным входом второго триггера, инверсный выход элемента И является выходом имитации сбоев устройства, I