Устройство для сопряжения источника и приемника информации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства буферной памяти. Целью изобретения является повышение достоверности за счет аппаратного разделения во времени совпадающих команд записи и чтения. Устройство содержит распределитель импульсов, блок памяти, регистр, реверсивный счетчик, счетчик записи, счетчик чтения, дешифратор заполнения, дешифратор нуля, две группы элементов И, группу элементов ИЛИ, два элемента И, два элемента задержки. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

PECllYEifNH

„„Я0„„1562921

А1 (51)5 G 06 F 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К A ВТОРСКОМ,К СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4457389/24-24 (22) 08.07.88 (46) 07.05.90. Бюл. №- 17 (72) С.С.Игнатьев и В.А.Ионова (53) 681.325(088.8) (56) Авторское свидетельство СССР

¹ 1019428, кл. С 06 F 13/00, 1983.

Авторское свидетельство СССР № 1309032, кл. G 06 F )3/00, 1987. (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ИСТОЧНИКА И ПРИЕМНИКА ИНФОРМАЦИИ (57) Изобретение относится к вычислительной технике и может быть исИзобретение относится к вычислительной технике и может быть использовано в качестве устройства буферной памяти.

Целью изобретения является повышение достоверности за счет аппаратного разделения во времени совпадающих команд записи и чтения.

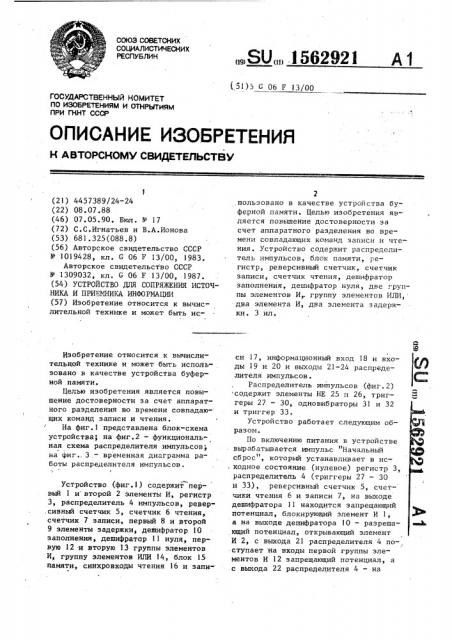

На фиг.1 представлена блок-схема устройства; на 4иг.2 — функциональная схема распределителя импульсов на фиг.. 3 . — временная диаграмма работы распределителя имгульсов.

1 /

Устройство (фиг.1) содержит первый 1 и второй 2 элементы И, регистр

3, распределитель 4 импульсов, ревер.сивный счетчик 5, счетчик 6 чтения, счетчик 7 записи, первый 8 и второй

9 элементы задержки, дешифратор 10 заполнения, дешифратор 11 нуля, первую 12 и вторую 13 группы элементов

И, группу элементов ИЛИ 14, блок 15 памяти, синхровхоцы чтения 16 и запи2 ,пользовано в качестве устройства буферной памяти. Целью изобретения является повышение достоверности за счет аппаратного разделения во времени совпадающих команд записи и чтения. Устройство содержит распределитель импульсов, блок памяти, регистр, реверсивный счетчик, счетчик записи, счетчик чтения, дешифратор заполнения, дешифратор нуля, две группы элементов И„ группу элементов ИЛИ, два элемента И, два элемента задержки 3 ил си 17, информационный вход 18 и входы 19 и 20 и выходы 21-24 распределителя импульсов.

Распределитель импульсов (фиг.2) содержит элементы HE 25 и 26, триггеры 27 — 30, одновибраторы 31 и 32 и триггер 33.

Устройство работает следующим образом.

По включению питания в устройстве . вырабатывается импульс "Начальный сброс", который устанавливает в исходное состояние (нулевое) регистр 3, распределитель 4 (триггеры 27 — 30 и 33), реверсивный счетчик 5, счетчики чтения 6 и записи 7, на выходе дешифратора 11 находится запрещающий потенциал, блокирующий элемент И 1, а на выходе дешифратора 10 — разрешающий потенциал, открывающий элемент

И 2, с выхода 21 распределителя 4 поступает на входы первой группы элементов И 12 запрещающий потенциал, а с выхода 22 распределителя 4 — на

1562921 входы второй группы элементов И 13 разрешающий потенциал, подключая тем самым счетчик 7 записи к адресным входам блока 15 памяти поэтому устУ

5 ройство подготовлено к приему информации от источника.

Синхросигналом записи с входа 17 устройства происходит запись информации, поступающей с входа 18 устройст- . о ва параллельным кодом, в регистр 3 и модифицируется первый адрес на выходе начетчика 7 записи, который поступает йа адресные входы блока 15 памяти через группу элементов И 12, открытые разрешающим потенциалом с выхода 22 распределителя 4, и группу элементов

HJIH 14. Кроме того, синхросигнал записи с входа 17 устройства поступает йа вход 20 распределителя 4, который формирует на выходе 24 импульс записи, который поступает на вход увеличения счета реверсивного счетчика 5, увеличивая его состояние на единицу, а также осуществляет через элемент 9 задержки перезапись информации из регистра 3 в блок 15 памяти. С выхода дешифратора 11 снимается запрещающий

Потенциал, разрешая тем самым прохождение синхросигналов чтения В уст щ фойство

При поступлении следующего кода на вход 18 устройства и синхросигнала записи на вход 17 происходит увеличение на единицу счетчика 7 записи, на адресном входе устанавливается второй адрес, по которому происходит: перезапись информации из регистра 3 в блок 15 памяти с помощью импульса записи с выхода 24 распределителя 4. 40

Этот же импульс записи увеличивает состояние реверсивного счетчика 5 на единицу. Аналогичным образом происходит дальнейшее заполнение информацией блока 15 памяти. При заполнении всех ячеек блока 15 памяти, о чем свидетельствует заполнение реверсивного счетчика 5, дешифратор 10 заполнения формирует сигнал„ блокирующий элемент И 2 и тем самым запрещает дальнейшую запись информации в блок

15 памяти. Первый же синхросигнал чтения, поступивший на вход 16 устрой,ства, производит считывание информа55 чтения, снимает запрещающий потенциал по входу 17 и разрешает дальнейшую запись информации в устройство. Сигнал с выхода дешифратора 10 может быть выдан источнику информации клк сигнал заполнения блока 15 памяти и блокировки выдачи данных на вход 18 устройства, Если на вход 16 приходит синхросигнал считывания до того, как произойдет заполнение блока 15 памяти, счетчика 7 записи и реверсивного счетчика 5 соответственно информацией, синхросигналами записи и импульсами записи, в счетчик 6 записывается единица. С выхода 23 распределителя 4 импульс чтения вычитает из содержимого реверсивного счетчика

5 единицу и через элемент 8 задержки поступает на вход блока 15 памяти, осуществляя считывание информации из блока 15 памяти на выход устройства.

Адрес, по которому происходит считывание информаций, подается с выхода счетчика 6 чтения через группу элементов И 12, открытые разрешающим потенциалом с выхода 21 распределителя

4, и группу элементов ИЛИ 14.

При поступлении следующего синхро. сигнала чтения на вход 16 устройства в счетчик 6 чтения добавляется единица и на адресном входе блока 15 памяти выставляется код второго адреса. С выхода 23 распределителя 4 импульс чтения уменьшает состояние реверсивного счетчика 5 на единицу и осуществляет считывание информации по данному адресу из блока 15 памяти на выход устройства. При завершении считывания всех информационных слов, записанных в блок 15 памяти, реверсивный счетчик 5 устанавливается в нулевое состояние, вследствие чего дешифратор 11 формирует сигнал, блокирующий элемент И 1 и запрещающий изменение состояния устройства по сигналам считывания, поступающим на вход 16. Одновременно сигнал с выхода дешифратора ll может быть подан на приемник информации как сигнал запрета чтения (отсутствия информации для чтения).

В случае, когда на входы 16 и 17 устройства поступают одновременно синхросигналы записи и чтения, распределитель 4 осуществляет разнесение во времени циклов записи и счиФ тывания. При этом информация на входе 18 по синхросигналу на входе 17 записывается в регистр 3. После этого распределитель 4 формирует сигналы, по которым осуществляется запись ин5 1562921 6 формации из Регистра 3 в блок 15 па- гистр, два элемента H pBG элемента мяти, а затем считывание информации задержки две группы элементов И, » т в, групиз него или, наоборот, сначала считы- пу элементов ИЛИ, причем первый вход вание информации из блока 15 памяти, первого элемента И является входом

5 а затем перезапись информации из ре- устройства для подключения к выходу гистра 3 в блок 15 памяти. Порядок чтения приемника инфоРмации, пеовый следования циклов записи и считывания вход второго элемента И соединен с зависит от частоты синхронизации. входом записи регистра и является

При одновременном приходе синхро- 10 входом УстРойства длЯ подключениЯ к сигналов чтения и записи на входы 19 выходу записи источника информации, и 20 распределителя триггеры 27 и 28 группа информационных входов регистустанавливаются в единичное состоя- ра образует группу входов устройства ние, так как входы этих триггеров под- ДлЯ поДключениЯ к гРУппе информаЦионключены к логической "1" . После этого 1g ных выходов источника информации, перезапись состояний триггеров 27 и группа информационных выходов блока

28 в следующую пару триггеров 29 и памяти образует группу информационных

30 осуществляется по переднему фронту выходов длЯ подключениЯ к гРУппе инчастоты синхронизации в триггер 30 и формапионных входов пРиемника инфорпо заднему фронту частоты синхрониза- 20 маЦии, при этом гРУппа выхоДов РевеРции в триггер 29. Одновибраторы 31 и сивного счетчика соединена с группами

32 формируют импульсы необходимой информационных входов дешифратора нуцлительности для надежной работы триг- ля и дешифратора заполнения, выходы гера 33, реверсивного счетчика 5 и которых соединены соответственно с ! ,блока 15 памяти устройства. Импульс 25 вторыми входами первого и второго эле »с одновибратора 31 поступает на вхо- . ментов И, выходы которых соединены ! цы установки в "0" триггеров 27 и 29, соответственно с первым и вторым вховход установки триггера 33 в "1", на дами запуска распределителя имнульвход уменьшения счета реверсивного сов, первый и второй синхровыходы косчетчика 5 и через элемент 8 задерж- 30 торого соединены соответственно с ки на вход чтения блока 15 памяти. первыми входами элементов И первой и

Импульс с одновибратора 32 поступает второй групп, вторые входы которых на входы установки в "0» триггера 33 соединены соответственно с выходами и триггеров 28 и 30, на вход увеличе- счетчика чтения и счетчика записи, I ния счета реверсивного счетчика 5 и 3> счетные входы которых соединены соот»через элемент 9 задержки на вход пе- ветственно с выходами первого и вто резаписи информации блока 15 памяти. рого элементов И, выходы элементов И

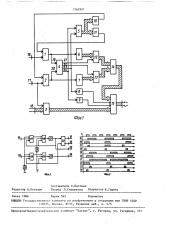

Циклограмма работы распределителя первой и второй групп соединены соимпульсов (фиг.3) приведена для раз- ответственно с первыми и вторыми вхоличных сочетаний входных сигналов от- 40 дами элементов ИЛИ группы, выходы коносительно частоты синхронизации. торых соединены с группой адресных

Таким образом, устройство осущест- входов блока памяти, входы чтения и вляет прием и выдачу информации без записи которого соединены соответстискажений и исключает возможность ее венно с выходами первого и второго потери за счет подключения входов ре- 45 элементов задержки, входы которых соеверсивного счетчика к третьему и чет- динены соответственно с третьим и вертому выходам распределителя управ- четвертым синхровыходами распределиляющих сигналов, что исключает одно- теля импульсов, группа информационвременное появление импульсов записи ных выходов регистра соединена с групи чтения на входах реверсивного счет- 50 пой информационных входов блока памячика. ти,отличающpеся тем, что, с целью повышения достоверности

Ф о р м у л а и з о б р е т е н и я за счет аппаратного разделения во вреУстройство для сопряжения источ- мени совпадающих команд записи и чтеника и приемника информации, содер- >> ния, третий и четвертый синхровыходы жащее блок памяти, распределитель им- распределителя импульсов соединены сопульсов, счетчик записи, счетчик ответственно с входами увеличения и чтения, реверсивный счетчик, дешифра- уменьшения счета реверсивного счеттор заполнения, дешифратор нуля, ре-,чика.

1562921

ЧЬй2

Составитель С.Пестмал

Техред Л. Сердюкова Корректор В. Гирняк Редактор Н.Рогулич

Заказ 1066 Тираж 562 Подписное

ВНИИПИ Государственного комитета по изобретениям и открьггиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101