Устройство для вычисления логарифмов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к устройствам для выполнения математических операций в двоичном представлении, и может быть применено в качестве спецпроцессора в комплексе с вычислительной машиной для вычисления натурального логарифма чисел. Цель изобретения - повышение точности вычисления функции. Поставленная цель достигается тем, что устройство содержит N<SP POS="POST">2</SP>-N/2 (где N - число разрядов аргумента) коммутаторов 1, N-1 элементов И 2, N<SP POS="POST">2</SP>-N/2 сумматоров 3, N<SP POS="POST">2</SP>-N/2 преобразователей кода 4, N<SP POS="POST">2</SP>-3N+2/2 умножителей 5, сумматор результата 6, вход аргумента 7, выход 8. Работа устройства основана на том что для функции Y-LN (1+X) справедливо соотношение Y(I)=X(I) - Σ J/I X(IJ) Y(J), где X(I) - разряды аргумента, Y(I) - разряды функции. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

09) (11)

Ц1)5 С 06 F 7/556

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОИ ЕТЕНИЯМ И Отк) ЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4402248/24-24 (22) 04,04.88 (46) 15.05.90. Бюл. й- 18 (71) Институт проблем моделирования в энергетике AH УССР (72) А.Н.Давыденко, В.В.Литвиненко, В.В.Иохор, К.И.Оленич и К,И.Рогозин (53) 681.325 (088.8)

I (56) Авторское свидетельство СССР

М 849210, кл, G 06 F 7/556, 1979.

Авторское свидетельство СССР

1012251, кл. G 06 F 7/556, 1981. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМОВ (57) Изобретение относится к вычислительной-технике, в частности к устройствам для выполнения математических операций в двоичном представлении, и может быть применено в качестИзобретение относится к вычислительной технике, в частности к устройствам для выполнения математических операций в двоичном представле( нии, и может быть применено в качестве спецпроцессора в комплексе с вычислительной машиной для вычисления натурального логарифма чисел. !

Цель изобретения — повышение точности вычисления функции. г

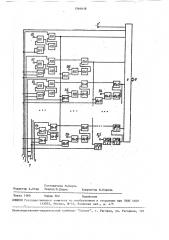

На чертеже представлена структурная схема устройства для вычисления логарифмов.

2 ве спецпроцессора в комплексе с вычислительной машиной для вычисления натурального логарифма чисел. Цель изобретения — повыпение точности вычисления функции. Поставленная цель достигается тем, что устройство соп2-и держит 2 (где и — число разрядов аргумента) коммутаторов 1, и-1 элеп2 -и n2 -Il ментов И 2, сумматоров 3, п2 -Зп+2 преобразователей кода 4, 2 ум- ножителей 5, сумматор результата 6, вход ? аргумента, выход 8, Работа устройства основана на том что для функции Y=ln(1+X) справедливо соотно- 9

i-t шение Y(i)=X:()- 4 Х(Ц )7(д), где

„ =Оi

X(i) — разряды аргумента, Y(i) — разряды функции. 1 ил.

I Ю и- -и

Устройство содержит — — (где n —2 число разрядов аргумента) коммутатоп2 -и ров 1, и-1 элементов И 2, сумп2 маторов 3, 2 преобразователей 4 и -3п+2 кода, †- — — умножителей 5, сумматор

6 результата, вход 7 аргумента и выход 8.

Устройство работает следующим образом.

1564618

Цля функции 1=1п(1+Х) справедливо

1 — » соотношение У(1) =X(i ) — Z 3Х(1-j )Y(j ), =o> при г (0)=О» i=1»2» и, где X(i) разряды аргумента, У(х) — разряды функции.

Рассмотрим работу устройства на конкретном примере вычисления функции

7 1п(1+Х). Ограничимся четырьмя вычи- 1О

l сояемыми разрядами (n=-4), Х=О,4375.

Мантисса аргумента Х -0,0111 подае гся поразрядно на вход 7, Х(1)="0" п ступает на вторые входь; первого, в opGI и третьего элементов И 2.

Н первые входы этих элементов поступают соответственно 1-й„ 2-:,, 3-й разряды мантиссы аргумента, равные

»1«)»! lI 1 1» 11 1 11

» »

Р

В соответствии с этим на выходах 2О первого» второго и третьего элементов

Hl 2 появляются логические сигналы

"«)"» О", О". Эти сигналы подаются соответственно на управляющие входы ( первого» второго H третьего коммутато- 25 ров 1, на информационные входы котор х подаются константы 0,1000, О. 101, О;.0100.

В результате коммутаторы закрьгва- ю ся и на их выходах образуются ком - -»О бйнации 0.0000, О.ОООО, 0.0000. Эти комбинации поступяюч на входы первого, второго и третьего преобразователей 4 кода, На выходах преобразователей кода образуются сигналы в дополнительном

35 к де 0,0000, 0Ä0000, 0,0000, которые п ступают на первые входы первого, в орого и третьего сумматоров 3„ на ! вгорые входы которых поступают 2 — й, З й» 4-й разряды мантиссы аргумента.

На выходе этих сумматоров появляюгся комбинации 1,0000, 1.-0000., 1.0000, С выхода первого сумматора кодовая комбинация подается ня третий вход сумматора результата со сдвигом на д9я разряда — 0,0100, и одновременно комбинация 1.0000 подается на инфор-. мационные входы четвертого и пятого коммутаторов 1, на управляют»е входы которых подаются соответсгвенно 1-й, 2-й разряды мантиссы аргумента, равii 0ii ii 1 ii

Четвертый коммутатор закрывается» а пятый открывается, на вь»одах этих

55 коммутаторов появляются комбинации

0»0000, 1,0000, поступающие далее на первые входы первого и второго умножителей 5, на вторые входы которых подаются константы О. 1010, О. 1000.

На выходах умножителей появляются комбинации 0 „0000, О, 1000, подаваемые далее на входы четвертого и пятого преобразователей 4 кода, на выходах которых образуются комбинации в дополнительном коде 0.0000, 1.1000» которые подаются на первые входы четвертого и пятого сумматоров 3 на вторые входы которых поступают выходные комбинации с второго и третьего сумматоров 3 соответственно.

Результаты суммирования равны соответственно 1.0000, 0.1000. Результат с выхода четвертого сумматора 3 подается на четвертый вход сумматора результата со сдвигом на три разряда—

0.00 10 и одновременно поступает на информационный вход шестого коммутатора 1, на управляющий вход которого поступает первый разряд мантиссы аргумента, коммутатор закрывается, и код 0.0000 с выхода коммутатора поступает на первый вход третьего умножителя 5, на второй вход которого подается константа О, 1100.

Результат умножения, равный 0.0000» подается на вход шестого преобразователя 4 кода, на его выходе образуется кодовая комбинация 0,.0000, которая поступает на первый вход шестсго сум-матора 3, на второй вход которого подается результат с пятого сумматора

3, равный 0.1000„ Результат суммирования, равный 0.1000, подается на пятый вход сумматора результата со сдвигом на четыре разряда — 0.00001, на второй вход сумматора результата поступает первый разряд мантиссы аргумента со сдвигом на один разряд — 0.0000.

На первый вход сумматора результата подается значение логического нуля.

Окончательный результат равен »

=-О, 01101 или» .<0=-0,40625

2.

Формула изобретения

Устройство для вычисления логарифмов, содержащее 2 (и-1) (где н — число разрядов аргумента) сумматоров и п-1 элементов И, о т л и ч а ю щ е е с я тем, что, с целью повышения точности вычисления функции, в него и —.5п+4 дополнительно введены †: — — сумма? п2торов, — — коммутаторов, .-- — — преоб15646 п2-Зп+2 разователей — — — — умножителей и

2 п2 -п вход 1-ГО (1=1, 2„..., 2 ) сумматора соединен с выходом i-го преобразователя кодов, второй вход К-го сумматора соединен с (К+ 1)-м разрядом входа аргумента устройства, вход К-го преобразователя кода соединен с выходом

: -го коммутатора, информационный вход ., которого соединен с входом задания числа 1/(К+1) устройства, управляю Н вход К-го коммутатора соединен с выходом К-го элемента И, первый вход

20 сумматор результата, причем выход устройства соединен с выходом сумматора результата, первый вход которого соединен с входом задания логического нуля устройства, второй вход сумматора результата соединен с первым разрядом входа аргумента устройства, 10

,K+2)-й (K=1,2,...,n-1) вход сУмматора результата соединен с выходом (К-1)(2n-К)+2

) го сумматора, первый

18 6 которого соединен с первым разрядом входа аргумента устройства, второй вход К-го элемента И соединен с К-м разрядом входа аргумента устройства, 2п +2n-1 (1+1) первый вход (— — - - — -)-го преобразователя кодов (j=1 2...,,n-2; р=1..., n-1-j) соединен с выходом

2п (-1 ) — j (+1 )+2 (р+1,))

2 первый вход которого соединен с вхо-!

j+1 дом зацания числа †. — — устройства

1+р+1

2n(j-1) - (j+1)+2(@+1) второй вход (2

) го умножнтеля соединен с выходом

-nj+2 -1(+1) (— -------- — - -го коммутатора упУ равляюг ий вход которого соединен с р-и разрядом входа аргумента уст" ройства, информационный вход

2nJ+2p-J (1+1) (— — — --- — — — ) -го коммутатора соеди2 нен с (3+1)-м входом сумматора результата.

1564618

Составитель M.Êàóëü

Редактор А.Orap Техред N.Äèäûê. Корректор Н.Король

Заказ 1160 Тираж 562 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент", r. Ужгород, ул. Гагарина, 101