Устройство для контроля логических блоков

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и является усовершенствованием изобретения по а.с.N1332322. Цель изобретения - повышение достоверности контроля. Устройство содержит блок синхронизации 1, блок потенциального согласования 2, генератор тестов 4, блок управления 5, мультиплексор 6, узел 7 выделения коротких импульсов, сигнатурный анализатор 8, коммутатор 9, контролируемый блок 13. За счет введения узла 7 обеспечивается возможность фиксировать импульсы разной полярности и длительности. 1 з.п.ф-лы, 4 ил.

СОЮЗ СО8ЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ÄÄSUÄÄ 1564629

Ц1)э С 06 F 11/26

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ

}lO ИЗОБРЕТЕНИЯМ И OTHPblTHRM

ПРИ ГКНТ СССР

1 (61) 1332322 (21) 4394058/24-24 .(22) 19.01.88 (46) 15.05.90. Бюл. М 18 (71) Научно-исследовательский и конструкторско-технологический институт средств контроля электронной аппаратуры и изделий электронной техники Контрольприбор" (72) С.А.Емельянов и E.Â.Ìèxåéêèíà (53) 681.3{088.8) (56) Авторское свидетельство СССР . У 1.332322, кл. G 06 F 1!/26, 1986. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕС: КНХ БЛОКОВ (57) Изобретение относится к автоматике и вычислительной технике и является усовершенствованием изобретения по авт.св. М 1332322. Цель изобретения — повьпнение достоверности контроля. Устройство содержит блок синхронизации 1, блок потенциального согласования 2, генератор тестов 4, блок управления 5, мультиплексор 6, узел 7 выделения коротких импульсов, сигнатурный анализатор 8, коммутатор 9, контролируемый блок 13. За счет введения узла 7 обеспечивается возможность фиксировать импульсы разной полярности и длительности. 1 з.п. ф-лы, 4 ил.

1564629

Изобретение относится к автоматике и вычислительной технике, может быть использовано для контроля логических блоков и схем и является дополнительным к авт.св. М 1332322.

Цель изобретения — повышение достоверности контроля.

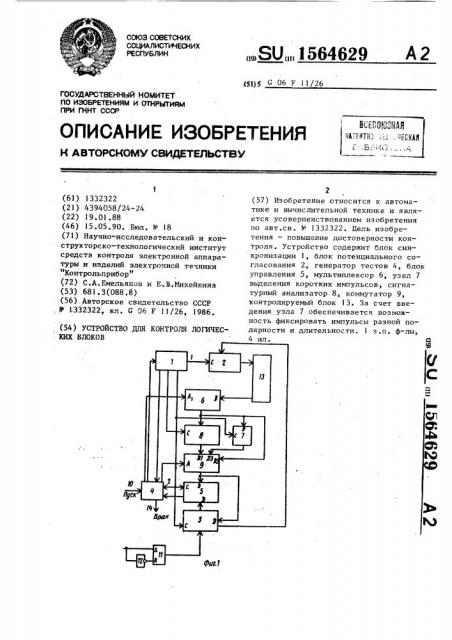

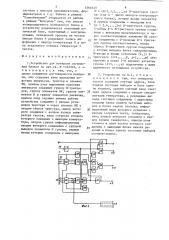

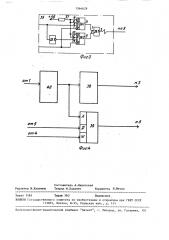

На фиг.l схематически показано устройство для контроля на фиг.2 — схе1

10 ма блока управления; на фиг.3 — схема блока регистрации коротких импульсов; на фиг,4 — схема генератора тестов.

Устройство (фиг.1) соцержит бпок

1 синхронизации, блок 2 потенциального согласования, генератор 3 тестов, блок 4 управления„ блок 5 сравнения, мультиплексор 6, узел 7 выделения коротких импульсов, сигнатурный анализатор 8, коммутатор 9, вход

10 пуска, триггер 11, элемент НЕ 12, контролируемый блок 13, выход 14 брака.

Блок управления (фиг.2) содержит триггеры 15 и 16, формирователь 17 импульса, элемент 18 задержки, элемент ИЛИ 19, счетчик 20, дешифратор

21 нуля, формирователи 22 и 23 импульсов, элемент ИЛИ 24, формирователь 25 импульсов, счетчик, образованный счетчиком 26 и дешифратором 27 нуля, элемент И 28, элемент 29 задержки, элемент ИЛИ 30, также обозначены нины 31 и 32 задания начальных данных.

Узел выделения коротких импульсов (фиг.3, для удобства показана часть, обслуживающая один выход) содержит группу элементов НЕ 33.1 — 33.п груп-40 пу 0-триггеров 34 .1 - 34 .п (где n— число выходов контролируемого блока), пину 35 единичного потенциала, группу элементов И 36.1 — Зб.п, группу элементов развязки 37.1 — 37.п, вы- 45 полненных на резисторах.

Генератор тестов (фиг.4) содержит блок 38 памяти тестовых наборов 38, блок 39 памяти эталона, счетчик 40 адреса.

Устройство работает следующим образом.

Логический уровень на выходе триггера ll определяет один из двух возможных режимов работы устройства:кон55 троль или самообучение.

При работе в режиме "Контроль" по запускающему сигналу, поступающему на вход 10 пуска устройства, блок 4 управления разрешает работу блока 1 синхронизации.

Блок 1 синхронизации обеспечивает необходимую временную диаграмму контроля, формируя сигналы управления работой блока 2 потенциального согласования, сигнатурного анализатора 8, узла 7, генератора 3 тестов и блока

4 управления.

Синхросигнал с выхода блока 1 синхронизации разрешает выбор из генератора 3 тестов очередного тестового набора (выход поля тестов) и эталонной реакции (выход поля эталонного отклика), которые поступают соответственно на входы контролируемого логического блока 13 (через блок 2 потенциального согласования) и на информационный вход блока 5 сравнения.

Одновременно сбрасываются триггеры узла 7.

Реакции контролируемого логического блока 13 поступают на информационный вход мультиплексора 6, который в зависимости от комбинации сигналов на адресном входе, поступающей с выхода блока 4 управления, подключает очередной выход кснтролируемого логического блока 13 к информационным входам сигнатурного анализатора 8 и узла 7, работа которых стробируется синхроимпУльсами, поступающими с выхода блока l синхронизации. Сигнал с выхода блока 4 управления, поступающий на синхровход коммутатора 9, подключает выход сигнатурного анализатора 8 или узел 7 к информационному входу блока 5 равнения, на котором происходят сравнения реакции контролируемого логического блока 13 и эталонного отклика при поступлении синхросигнала с выхода блока 4 управления.

Мультиплексированный отклик контролируемого блока поступает на узел

7 выделения коротких импульсов. По переднему фронту этого импульса срабатывает триггер 34.1, .à по заднему (через элемент НЕ 33.1) - триггер

34.2. На элемент И,36.1 поступят две единицы,и на выходе элемента И 36.1 появится единица, которая поступит на коммутатор 9 для дальнейшей обработки.

Сигналом от блока 1 .синхронизации триггеры 34 переводятся в исходное состояние.

Таким образом, узел 7 позволяет фиксировать кратковременные сбои или

5 1564 сигналы с выходов одновибраторов, формирователей и т.д. Работа в режиме

tt

Самообучение отличается от работы

It в режиме Контроль тем, что вместо

Il tt контролируемого логического блока к устройству подключается эталонный логический блок, однотипный с контролируемым, логический уровень на шестом выходе блока 4 разрешает запись ийформации с выхода коммутатора 9 в поле эталонного отклика генератора 3 тестов.

20 2. Устройство по и.1, о т л и— ч а ю щ е е с я тем, что генератор тестов содержит счетчик адреса, блок памяти тестовых наборов и блок памяти эталона, причем счетный вход счет25 чика адреса соединен с входом синхронизации генератора, а разрядные выходы счетчика соединены с адресными входами блока памяти тестовых наборов и блока памяти эталона, инфор30 мационный вход которого соединен с входом загрузки теста, генератора, вход записи которого соединен с входом записи генератора, выходы поля эталона и поля тестов которого соединены с выходами блока памяти ре35 акций и блока памяти тестовых наборов соответственно. ф о р м у л а изобретения

1.Устройство для контроля логических блоков по авт.св. М 1332322, о тл и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, оно содержит узел выделения коротких импульсов, триггер и элемент

НЕ, причем узел выделения коротких импульсов содержит группу D-триггеров, группу элементов НЕ, группу элементов И и группу элементов развязки, причем вход задания режима работы устройства соединен с входом установки триггера и через элемент НЕ с входом сброса триггера, выход которого соединен с входом записи генератора тестов, вход загрузки эталона которого соединен с выходом коммутатора вторая группа информационных входов которого соединена с группой выходов элементов И группы, первые входы которых соединены с выходами

629 6

К-х (K=1,3,5, ....,n) D-триггеров группы (где n — число выходов контролируемого блока), вторые входы элементов

И группы соединены с выходами m-x (m = 2,4,...,2n) Р-триггеров группы, С-входы К-х D-триггеров группы соединены с выходами мультиплексора и через соответствующие элементы НЕ группы соединены с С вЂ входа m-х триггеров группы соответственно, входы сброса D-триггеров гругпы соединены с вторым выходом блока .синхронизации, D-входы и входы установки (i j) Dтриггеров (i=l К, j=2, т) объединены и через 1-й элемент развязки группы (1=1,...,n) подключены к шине единичного потенциала устройства.

1564629

Составителв А.Сиротская

Техред N.Õîäàíè÷ Корректор И.Куска

Редактор М.Келемеш

Заказ 1161 Тираж 563 Подписное

ВНИИЛИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101