Устройство сопряжения процессоров с разделяемыми ресурсами

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для построения мультипроцессорных систем с разделяемыми ресурсами. Целью изобретения является расширение области применения. Цель достигается за счет возможности наращивания числа процессоров путем простого увеличения числа элементов в схеме синхронизации без дополнительной настройки и обеспечения обслуживания запроса каждого процессора независимо от приоритета, при этом осуществляется сопряжение как с пассивными (память), так и с активными разделяемыми ресурсами. Для этого в устройство введены K-1 блоков сопряжения процессоров с разделяемой памятью и M групп блоков управления доступом, причем 2<SP POS="POST">M</SP>=K, образующих двунаправленное двоичное дерево при арбитраже сигналов запросов доступа к ресурсам от процессоров и активных устройств. 1 ил.

СОЮЗ СОНЬТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК щ) 5 Г Об F 15/16, 13/14

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

H A BTGPCHGMY СВИДЕТЕЛЬСТВУ (21) 4352484/24-24 (22) 30.12.87 (46) 15.05.90. Бюл . ¹ 18 (72) В.В. Харько, С.А.Абаджиди, В.В.Гераськов и Ю.Т;Котов (53) 681.3(088.8) (56) Авторское свидетельство СССР № 1241246, кл. С 06 F 13/00, 1983.

Авторское свидетельство СССР № 1396817, кл. G 06 F 13/00, 1986. (54) УСТРОЙСТВО СОПРЯЖЕНИЯ ПРОЦЕССОРОВ С РАЗДЕЛЯЕМЫМИ РЕСУРСАИИ (57) Изобретение относится к вычислительной технике и может быть использовано для построения мультипроцессорных систем с разделяемыми ресурсами. Целью изобретения является расширение области применения. Цель

Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах для органиэации на его основе многопроцессорных систем, объединяющих в своем составе произвольное количество процессоров.

Цель изобретения — расширение области применения за счет возможности наращивания числа процессоров путем простого увеличения числа элементов в схеме синхронизации без дополнительной настройки и обеспечения обслуживания запроса каждого процессора независимо от приоритета при возможности сопряжения как с пассивными (память), так и с активными разделяемыми ресурсами.

„„SU„„1564640 А 1 достигается за счет возможности наращивания числа процессоров путем простого увеличения числа элементов в схеме синхронизации без дополнительной настройки и обеспечения обслуживания запроса каждого процессора независимо от приоритета, при этом осуществляется сопряжение как с пассивными (память), так и с активными разделяемыми ресурсами. Для этого в устройство введены К-1 блоков сопряжения процессоров с разделяемой памятью и М групп блоков управления доступом, м причем 2 =K образующих двунаправленное двоичное дерево при арбитраже сигналов запросов доступа к ресурсам от процессоров и активных устройств.

1 ил.

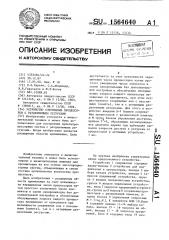

На чертеже изображена структурная схема предложенного устройства.

Устройство 1 сопряжения содержит входы-выходы 2 устройства для подключения к процессорам, выходы 3 выбора канала устройства, выходы 4 запросов прерываний устройства, группу 5 входов синхронизации устройства, группу 6 входов управления устройства, вход 7 запросов прерыванийустройства, руппу из К блоков 8 сопряжения процессоров с разделяемой памятью, М групп блоков 9 управления запросами

М = fin@>K >, К элементов ИЛИ !О.Блок

9 содержит выходы 11-14 выбора канала, выходы !5 — 16 запроса на обмен, выходы 17 — 18 запросов прерываний. Блок 8 содержи-. вход 19 син1564640 хронизации, вход 20 чтения, входы.— выхоцы 21 и 22 данных,, вход 23 выда— чи данных и вход 24 записи, вход 25 адреса, выход 26 адреса, выход ?7 запроса на обмен, вход 28 строба адреса, вход 29 выборки, вход-выход 30 для подключения к магистрали внешних устройств, вход 31 чтения данных. Блок 9, кроме того, содержит первые 32, 33 прямой и инверсный и вторые 34, 35 рдноименные входы запроса на обмен, входы 36, 37 выбора канала, входы 38. — 40 синхронизации, вход 41 запросов прерываний, Устройство сопряжения работает следующим образом.

Иэ процессоров на адресные входы

25 поступает адресная информация. Она сопровождается стробами адресов на ро одноименных входах 28. В случае режима записи на входы-выхоцы данных 21 одновременно с адресом поступает информация, подлежащая записи в ОП или

ПУ. 25

Вся указанная информация поступает на соответствующие входы блоков 8, которые производят анализ адресной информации и в зависимости от его реэультата выдают на выход 27 сигнал запроса (единичный — запрос обмена с

ПУ,, нулевой - запрос обмена с .ОП, в отсутствие сигнала запроса выход 27 находится в состоянии с высоким выходным сопротивлением) и подготавливают соответствующий тракт прохождения информации.

С выхода ?7 запросы от двух соседних а-го и (а+1)-го блоков 8 (а — нечетное число) поступают на входы 32, 4О

33 и 34, 35 соответствующих блоков 9 первой группы. Входы 32 и 34 воспринимают единичные сигналы, а входы 33 и 35 — нулевые. Получив сигналы запроса, блок 9 производит их арбитраж (по времени поступления) и в зависимости от вида поступивших сигналов также вьдает соответствующие сигналы на выходы 15 (нулевой сигнал) и (или)

16 (единичный). Эти сигналы от двух соседних блоков 9 йервой группы поступают на соответствующие входы (32, 34 и 33, 35) блоков 9 второй группы и т.д.

Блок 9 последней М-й группы (на входах 36 и 37 постоянно присутству-. ют единичные сигналы, разрешающие обмен соответственно с ПУ и ОЧ» ) в ответ на сигналы запросов после их арбитража вьдает на соответствующие из выходов 11 — 14 разрешающие сигналы.

Сигналом с выхода 11 нли 13 разрешается обмен с ОП, сигналом с выхода

12 или 14 — с ПУ. Причем разрешающий сигнал поступает только на один из соответствующих выходов, но одновременно может быть разрешен обмен информацией с ОП и ПУ. Разрешение на обмен с соответствующим ресурсом получает только один из двух блоков 9 предыдущей группы, который после его получения, в свою очередь, вьдает раэрешающий сигнал на соответствующий из выходов и т.д.

Блок 9 первой группы, получив сигнал разрешения обмена с ОП и (или)

ПУ, вьдает на соответствующие из выходов разрешающие сигналы (с учетом результатов проведенного в нем арбитража поступивших запрссов). Зти сигналы поступают на выходы выбора каналов устройства 1 и далее в соответствующие из К процессоров для активизации блока управления синхронным каналом (обмен с ОП) и (или) блока управления асинхронной магист- ралью (обмен с ПУ). Одновременно разрешающие сигналы через элементы ИЛИ

10 поступают на входы 19 синхронизации соответствующих блоков 8.

Разрешающими сигналами с выходов выбора канала устройства 1 запускаются в работу соответствующие ресурсы процессоров (блок управления асинхронной магистралью или блок управления синхронным каналом), которые вырабатывают управляющие сигналы в соответствии с временной диаграммой своего функционирования .

Сигналы с выходов. управляющих блоков процессоров поступают на входы управления и синхронизации устройства 1. Со входов управления сигналы (нЧтение»», "Вьдача данных", "Записьн

"Выборка устройства" и "Чтение данных") поступают на входы 20, 23, 24, 29 и 31 блоков 8 для обеспечения обмена информацией процессоров с ОП и

ПУ1функционироюание блока 8 в режимах чтения информации из ОП и ПУ в процессор и записи информации из проиессора в ОП и ПУ, его структурная схема и временная диаграмма работы изве тны).

На два из трех входа синхронизации из блоков управления синхронным каналом и асинхронной ма.гистралью по40

5 15646 ступают сигналы синхронизации обмена информацией по соответствующему из каналов. Они используются для установки блоков 9, выдавших разрешающие обмен информацией сигналы, в исход5 ное состояние. После этого обслуживаются запросы, поступившие в устройство 1 позже.

На входы запросов прерываний устройства 1 от периферийных устройств из магистрали поступают соответствующие сигналы на входы 41 блока 9 последней (М-й) группы. Этот блок 9 с целью уменьшения времени реакции на прерывание направляет запросы прерываний в тот из блоков 9 предыдущей группы (на входы 17 или 18), который не задействован в обмене информацией через магистраль, фиксируя при этом 20 выбранный тракт прохождения информации. Если обмен через магистраль не производится, то запросы направляются в тот из блоков 9, который не задействован в передаче информации через 25 синхронный канал. Таким образом, пройдя через блоки 9 от M-й группы до первой, запросы поступают на соответствующий из выходов запросов прерывания устройства и далее в соответ- ЭО ствующий процессор на обработку.

Обработка прерывания начинается с выдачи блоком управления магистралью соответствующего процессора сигнала разрешения прерывания который поступает на третий из входов синхронизации группы 5 устройства. После окончания обработки прерывания указанный сигнал снимается, в результате чего тракт прохождения сигналов за- 4g просов прерывания через блоки 9 устанавливается в исходное состояние, В предлагаемом устройстве для синхронизации доступа процессоров к разделяемым ресурсам системы использует- 45 ся схема арбитража запросов по времени их поступления. Она построена из однотипных элементов и имеет вид пирамиды, в основание которой поступают запросы на обслуживание от процессо- 5О ров. При этом каждый из элементов производит арбитраж двух запросов доступа к памяти или каналу ввода-вывода (при одновременном поступлении запросов случайным образом выбирается один из них) и, в свою очередь, запрашивает доступ к соответствующему ресурсу у элемента более высокого уровня. Послецний элемент (верши."а пирамиды) выдает разрешение на обмен информацией одному из двух элементов предыдущих уровней сразу же после процедуры арбитража, остальные — после получения разрешающих сигналов от элементов более высокого уровня.

Такая организация доступа к разделяемым ресурсам позволяет увеличи— вать число процессоров в многопроцессорной системе за счет простого наращивания количества элементов в схеме синхронизации без их дополнительчой настройки, Кроме того, каждый из процессоров, независимо от их числа в системе, получит доступ к ресурсам системы по мере обслуживания запросов, поступивших ранее.

Ф о р м у л а и з о б р е т е н и я

Устройство сопряжения процессоров с разделяемыми ресурсами, содержащее блок сопряжения процессоров с разделяемой памятью, о т л и ч а ю щ е ес я тем, что, с целью расширения области применения, оно содержит К-1 блоков сопряжения процессоров (К вЂ” количество сопрягаемьх процессоров) с разделяемой памятью, М групп блоков управления запросами, причем М ==(log К ), К элементов ИЛИ, причем входы адреса, строба адреса и первый вход-выход данных Ь-ro блока сопряжения процессоров с разделяемой па- мятью (Ь -- 1,К) образуют Ъ-й входвыход устройства для подключения к

Ь-му процессору, вторые входы-выходы данных и выходы адреса блоков сопряжения процессоров с разделяемой памятью объединены через магистраль и образуют вход-выход устройства для подключения к разделяемой памяти„входы †выхо для подключения к магистрали внешних устройств блоков сопряжения процессоров с разделяемой па-. мятью объединены и образуют вход-выход устройства для подключения к магистрали внешних устройств, входы чтения, записи, выборки, выдачи данных, чтения данных блоков сопряжения процессоров с разделяемой памятью подключены к одноименным входам устройства н образуют группу входов управления устройства, выход Ь-го элемента ИЛИ подключен к входу си . хронизации Ь-ro блока сопряжения процессоров с разделяемой памятью, выходы запроса на обмен (2р-1)-го и 2р-го

15á4640 и дм&

Ех

2Ре

Brod ад

Запрос рреридан

&родodpc

&род адреса

9алрасы ррерыйж

Диод

odpe

Яирдо -% од

daarron дыдор иа

Входы

У хране сы диод ррйле

fmpo адрес appose дрерыда (дхо адр<са охосЪ -аы

dohVY_#_A йЮориоьо

Cmpod

Ямрасы арерыоа

d nh odpee

Esodwk дсииых

Вь Вор ханил блоков сопряжения процсссораь с разделяемой памятью (р =- К j2, если р - четное и р=1, (К+1)/?, если р— нечетное) подключены к первым прямому H инверсному и вторым прямому и инверсному входам р-го блока управления запросами первой груг,пы, причем первый и второй выходы прерываний которого образуют (2р-!) — и и 2р-й вы- 1Г! ходы прерываний устройства, а выходы выбора канала е первого по четвертый образуют выходы выбора канала устройства с 4р-3 па 4р и соединены с первым и вторым входами (?р-1)-йo и 15

2р-го элементов ИЛИ соответственна,при1 ем с первого по третий входы синхронизации устройства подключены к одноименным входам блоков управления запросами, а вход запросов пре- 2О рываний устройства подключен к одно-именно;му входу блока управления запросами И-й группы, количество блоко8 управления запросами с-й группы (с=1,ll) равна ? (с+1) блоков управления запросами (с+1) -й группы, причем первый и второй выходы запроса на обмен (2а-1)-га блока управления запросами с-Й группы (а=1,с) подключены к первым прямому и инверсному входам, а 2а.-га — к вторым прямому и ину версному входам а-го блока управления запросами (с+1)-й группы, причем его выходы выбора канала с первого по четвертый подключены к первому и второму входам выбора канала (2a-!)-го и первому и второму входам 2а-го блоков управления запросами с-й группы„ кроме того, первый и второй выходы запросов прерываний а-го блока управления запросами (с+!)-й группы подключены соответственно к одноименным входам (2a-1)-ro и 2а-го блоков управления запросами с-й группы.