Устройство для селекции элементов изображений объектов

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и может быть использовано для выделения участков изображения произвольной формы. Цель изобретения - упрощение устройства. Поставленная цель достигается исключением сложных узлов и введением триггера, подключенного к блоку памяти и к сумматору. 2 ил.

СОЮЗ СОНЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (191 (11) (5}}5 G 06 K 9/36

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ФРЕЧ% " 11

ПйПЛ «с 110

Б ЙЬЛ-101. .t А

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4280152/24-24 (22) 07. 07, 87 (+6) 15,05,90. Бюл. 11- )8 (71) Киевский институт автоматики

::. и. XXV съезда КПСС (72) В.С.Ольшанников и И.Н.Остапчук (53) 681.327.12(088,8) (56) Авторское свидетельство СССР

913420, кл. С 06 К 9/46, 1982.

Авторское свидетельство СССР

У 1256054, кл. С 06 К 9/36, 1986.

Изобретение относится к автоматике и вычислительной технике, в ч".стности к устройствам для селекции элементов телевизионного изображения, и может быть использовано для выделения участков изображения произвольной формы с последующей обработкой их на ЭВИ.

Цель изобретения — упрощение устройства.

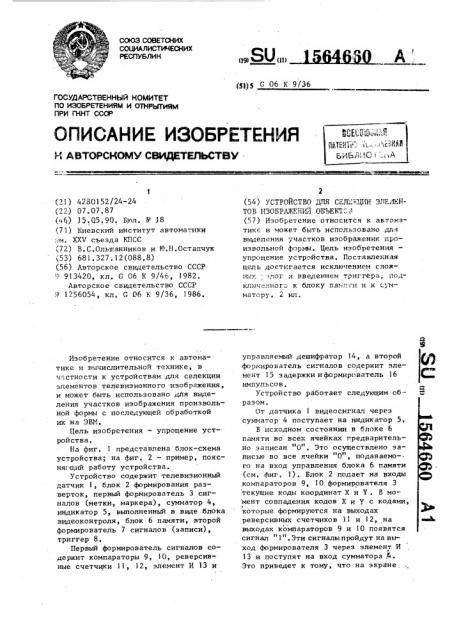

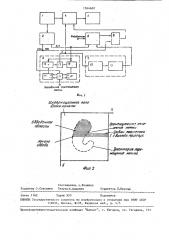

На фиг. 1 представлена блок-схема устройства; на фиг. 2 — пример, поясняг щий работу устройства.

Устройство содержит телевизионный датчик 1, блок 2 формирования разверток, первый формирователь 3 сигналов (метки, маркера), сумматор 4, индикатор 5, выполненный в виде блока видеоконтроля, блок 6 памяти, второй формирователь 7 сигналов (записи), триггер 8.

Первый формирователь сигналов содержит компараторы 9, 10, реверсивные счетчики 11, 12, элемент И 13 и

2 (54) УСТРОЙСТВО ДЛЯ СЕ1ЕЩИИ ЭЛЕЛЕНТОВ ИЗОБРАЖЕИРЛ OBbEKIG3 (57) Изобретение относится к автоматике и может быть использовано для выделения участков изображения произвольной формы. Цель изобретения упрощение устройства, Поставленная цель достигается исключением сложных .лов и введением триггера„ Io, ключенног=-. к блоку паня ги и к сумматору. 2 ил. управляемый дешифратор 14, а второй формирователь сигналов содержит элемент 15 задержки и формирователь 16 импульсов.

Устройство работает следующим об= разом.

От датчика 1 видеосигнал через сумматор 4 поступает на индикатор 5.

В исходном состоянии в блоке 6 памяти во всех ячейках гредварительно записан "О". Это осуществлено записью во все ячейки "0, подаваемо-. го на вход управления блока 6 памяти (см, фиг, 1). Блок 2 подает на входы ,компараторов 9, 10 формирователя 3 текущие коды координат Х и Y . В мо мент совпадения кодов Х и Y с кодами, 1 которые формируются на выходах реверсивных счетчиков 11 и 12, на выходах компараторов 9 и 10 появятся сигнал "1". Эти сигналы пройдут на выход формирователя 3 через элемент И

l3 и поступят на вход сумматора Д .

Это приведет к тому, что на экране

1564660 индикатора 5 сформируется яркое пятно, соответствующее расположению метки на экране. Одновременно на выходе формирователя 7 будет получен импульс, осуществляющий .запись в блоке

6 памяти. Еели к этому моменту времени оператор вывел метку в место начала обвода иэображения объекта (см. фиг. 2), то на вход управления 10 блока 6 памяти будет подана "1". Это

1 приведет к тому, что в ячейке блока памяти, адрес которой < оответствует: координатам метки на экране, в моменты формирования импульс" на выходе 15 формирователя 3 метки, будет записываться "1".

В процессе работы оператор перемещает метку по контуру изображения.

"ледовательно, во всех ячейках блока 20 б памяти, адреса которых соответствовали текущим координатам метки Х...„ и Ум, будут записаны "1" (след перемещения метки по информационному полю изображения). 25

Блок 6 все время, кроме моментов времени, в течение которых на выходе формирователя 3 вырабатывается импульс, работает в режиме считывания информации. Инфс.змация с его ЗО выхода поступает на счетный вход триггера 8 и все время модифицируе (изменяет на противоположное) егс состояние. T.е, первый единичный импульс с выхода блока б переведет триггер 8 в состояние "1", второй— в состояние "О", третий — в состояние "1", четвертый — в состояние

"0" и т.д. Привязка исходного состояния триггера 8 осуществляется подачей 49

ССИ на его вход установки в "0".

Логика формирования сигнала на выходе триггера 8 совпадает с логикой формирования. выходного сигнала блока памяти прототипа. Отличие 45 лишь в том, что в протстипе модификация видеосигнала вдоль строки выполняется записью в блоке памяти,.начиная от координаты Х и до конца э гой строки, информации в соответствии с 50 алгоритмом: считывание — модификация — запись. Такая запись осуществляется каждый раз при очередном изменении координат метки. В предложенном :.устройстве аналогичная модификация выполняется триггером 8 динамически, т,е„ в течение .формирова-, ния телевизионной разверткой изображения текущей строки, B блоке памяти записаны лишь координаты Х начала и конца изображения объекта вдоль каждой телевизионной строки. Результирующий видеосигнал на входе сум а;"ора ч полностью аналогичен соответзчуюшему сигналу на входе сумматора про тотипа.

Таким образом, при сохранении всех выполняемых функций по отношению к ,,вестному устройству достигнуто сокращение аппаратурных затрат за счег исключения из его состава слож- ных формирователей адресов записи

Х и У, блока определения направления перемещения метки, мультиплексора адреса и других элементов.

Фор ула изобретения

Устройство для селекции элементов изображений объектов, содержащее сумматор„ первый и второй информационные входы которого соединены с ин-. формационным выходом телевизионного датчика и выходом первого формирователя сигналов, а выход подключен к информационному входу индикатора, блок формированчя разверток, управляющий вход которого соединен с синхронизирующим выходом телевизионного датчика, а выходы подключены к информационному и синхронизирующему входам первого формирователя сигналов соответственно, и второй формирователь сигналов, выход которого соединен с ьходом управления записью блока памяти, о т л и ч а и щ е— е с я тем„ что, с целью упрощения устройства, оно содержит триггер, счетный вход которого соединен с выходом блока памяти, установочный вход подключен к синхронизирующему выходу блока формирования разверток, а прямой выход соединен с третьим информационным входом сумматора, при этом управляющий вход блока памяти является управляющим входом устройства, адресные входы блока памяти соединены с соответствующими выходами блока формирования разверток, а синхронизирующий вход второго формирователя сигналов подключен к вььходу первого формирователя сигналов.

1564660 у рпй ение аеремеща иж меижи

Фиг 1I

Уиоерм циоииое юаюе

Д Ж7ЯЩ ЮРМФМЖ

Составитель A.Романов

Техред М. Ходанич Корректор Л.Бескид

Редактор О.Спесивых

Ю

Заказ 1162 Тираж 559 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101

РРАЮЬУм®Р

Р&ОЖУ7а рудрщурууцуу.уу o yg

ЯВНУЮ МРЛД/ фЫяю А484- я ж/Х с 3иу666 л РЫРР Цг й