Устройство для программирования микросхем постоянной памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для записи информации с помощью пережигания в логических массивах с памятью. Целью изобретения является упрощение устройства. Устройство содержит формирователь 1 сигналов управления, формирователь 2 импульса запуска, блок 3 управления источником питания, дешифратор 4, блок 5 управления ключами, формирователь 6 импульсов программирования, блок 7 выборки, блок 8 сопряжения, блок 9 ключей, источник 10 питания. Устройство работает под управлением микроЭВМ, с которой соединяется через параллельный интерфейс, который входит в состав микроЭВМ, имеет три программных регистра: состояния, выходной и входной. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) А1 (51)5 (11 С 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

r1O ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4341873/24-24 (22) 10.12.87 (46) 15.05.90. Бюл. № 18 (72) Н.Д. Баранов и Е.Б. Житницкий (53) 681.327.66(088.8) (56) Авторское свидетельство СССР

1285535, кл. G 11 С 17/00, 1985.

Авторское свидетельство СССР № 1134964, кл. G 11 С 7/00, 1982.

I. (54) УСТРОЙСТВО ДПЯ ПРОГРАММИРОВАНИЯ

МИКРОСХКМ ПОСТОЯННОЙ ПАМЯТИ (57) Изобретение относится к вычис-. лительной технике и может быть использовано для записи информации с помощью пережигания в логических массивах

2 с памятью. Цель изобретения — упрощение устройства, Устройство содержит формирователь 1 сигналов управления, содержащий формирователь 2 импульса запуска, блок 3 управления источником питания, дешифратор 4 и блок 5 управления ключами, формирователь 6 импульсов программирования, блок 7 выборки, блок 8 сопряжения, блок 9 ключей, источник 10 питания. Устройство работает под управлением микроЭВМ, с которой соединяется через параллельный интерфейс, который входит в состав микроЭВМ, имеет три программных регистра: состояния, выходной и входной. 3 ил.

1564689

11зобретение относится к вычислительной технике и может быть использовано для записи информации с помо— щью пережигания в логических масси50 вах с памятью, Цель изобретения — упрощение устройства.

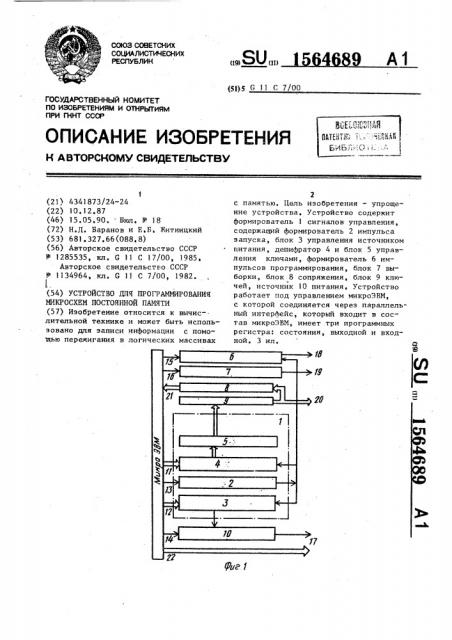

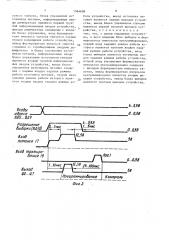

На фиг. 1 изображена блок-схема устройства; на фиг.2 и 3 — временная диаграмма работы устройства °

Устройство содержит формирователь

1 сигналов управления, состоящий иэ формирователя 2 импульса. запуска, 1 блока 3 управления источником питания, дешифратора 4 и блока 5 управ:ления ключами, формирователь 6 импульсов программирования, блок 7 выборки, блок 8 сопряжения, блок 9 клю:чей, источник 10 питания, первую 11 20 и вторую 1? группы информационных входов устройства„ первый 13 и вто рой 14 входы устройства, третий 15 и четвертый 16 входы задания режима работы устройства, первый 17, второй 18 25 и третий 19 выходы устройства, пер20 и вторую 21 устройства, вход 22 устройства.

Устройство работает следующим образом.

ЗО

Адрес ячейки поступает с выхода интерфейса микроЭВИ на вход программируемой микросхемы по входу 22, Устройство имеет следующие режимы работы: программирование бита, программирование бита слова инициализации, чтение данных.

Устройство работает под управлением микроЭВИ, с которой соединяется через параллельный интерфейс, вхо- 40 дящий в состав микроЭВИ и имеющий . три программных регистра: состояния, выходной и входной, при этом разряды 0...15 выходного регистра представлены в устройстве в виде сигна- 45 лов ВДОО...ВД15, разряды О, 1 регистра состояния — в виде сигналов РСО, РСI, а разряды 0...7 входного регистра — в виде сигналов ВВО...ВВ7 соответственно.

В исходном состоянии все разряды интерфейса очищены, Устройство в режиме программирования бита (фиг.2) работает следующим образом.

С устройства последовательного обмена, входящего в состав микроЭВМ, на входы 11-16 устройства (фиг,1) поступает группа сигналов, при этом через вход ?? устройства (фиг. 1) поступает группа сигналов ВЦОО...ВДII (на фиг.l не показаны, которая подается на входы адреса и разрешения. выхода программируемой микросхемы.

Сигнал ВДII поступает также на вход

l6 блока 7 (низкий в случае программирования микросхемы КР556РТ20 и высокий при программировании других микросхем, например KP556PT18j. На вход ll дешифратора 4 поступают сигналы ВД12...ВД14, комбинация которых задает номер программируемого бита.

На вход 14 поступает сигнал PCI, который включает источник 10. С вы— хода 17 напряжение питания +5В поступает на вход программируемой микросхемы.

Через интервал в несколько микросекунд на вход 13 поступает сигнал

РСО, который разрешает работу формирователя (фиг.l и 2), сигнал низкого уровня с выхода формирователя 2 поступает на вход блока 3, который формирует сигнал нулевого уровня на выходе, поступающий на вход источника

l0 питания. В результате на выходе 17 последнего устанавливается напряжение программирования +12,5В.

Сигнал с выхода формирователя 2 поступает низким уровнем на разрешающий вход дешифратора 4, разрешая выработку на одном из выходов АО...А7 последнего сигнала низкого уровня, и на вход блока 3, продолжая поддерживать напряжение питания программируемой микросхемы равным +12,5В, Сигнал с выхода дешифратора 4, пройдя через блок 5, формирует на выходе одного из ключей блока 9 импульс программирования с амплитудой +12,5В. Ло окончании программирования дешифратор 4 выключает блок 9 ключей, а на выходе 17 источника 10 напряжение падает до +58, что означает окончание цикла программирования бита. По окончании цикла программирования может осуществляться проверка правильности программирования, которая производится путем чтения данных с выхода программируемой микросхемы и программной проверки их истинности .

Чтение данных производится следующим образом. Если программируется микросхема КР556РТ20, то низкие уровни сигналов ВДII, ВД15 на входах разрешают формирование импульса на выходе 16, который поступает на тактирую5 ) 5646 щий вход программируемой микросхемы, что приводит к появлению данных на выходах последней. При чтении данных с микросхем другого типа, выход 16 находится в низком состоянии, Данные с выхода программируемой микросхемы поступают на группу выходов 20 блока 9, соединенных с входами блока 8. Группа выходов 21 блока 8 сопряжения (фиг,!) соединяется с разрядами 0...7 выходного регистра интерфейса микроЭВМ, через который производится чтение данных.

Сигналы на входах 11-16 устройст)5 ва (фиг. 1) ВДОО...ВД15, РСО, PC) переводятся в состояние лог. ItPlt в результате чего источник 10 питания выключается, а с входов программируемой микросхемы снимается напряжение пита- 20 ния и сигналы.

Программирование каждого последующего бита производится после паузы, длительность которой задается программно в соответствии с техническими ус- 25 ловиями на программируемую микросхему.

Устройство в режиме программирования бита слова инициализации (микросхема типа KP556PT20) работает следующим образом.

С микроЭВМ на входы )).-16, 22 устройства поступает группа сигналов

ВДОО...ВД15, РСО, РС1, при этом на вход 22 устройства (фиг.l) поступает группа сигналов ВДОО...ВД11, задающая

35 адрес программируемой ячейки и ра.эрешение выхода, и подается на вход программируемой микросхемы, причем вход разрешения выборки ВД10 устанав- 40 ливается в лог. "1", а вход синхронного разрешения выборки ВД11 — в лог. "О". Сигнал ВД11 низкого уровня поступает также на вход блока 7. На вход ll дешифратора 4 поступают сигналы ВД12...ВД14, комбинация которых задает номер программируемого бита.

Сигнал ВД15 высокого уровня поступает на вход 12 блока 3 и устанавливает его выход в высокое состояние, тем самым задавая напряжение питания программируемой микросхемы равным

+53.

На входе 14 источника 10 устанавливается сигнал РС1, который обеспечивает формирование на выходе 17 последнего напряжение питания +5В, ко89 б торое поступает на вход программируемой микросхемы, Через интервал в несколько микросекунд микроЭВМ устанавливает сигнал

РСО, который разрешает работу формирователя 2 и переводит выход 19 блока ? в низкое состояние.

С выхода формирователя 2 сигнал

ИЗП2 поступает низким уровнем на разрешающий вход Е дешифратора 4, разре-. шая выработку на одном иэ выходов

АО...А7 последнего сигнала низкого уровня, соответствующего номеру программируемого бита. Сигнал с выхода дешифратора 4, пройдя через блок 5, формирует на одном из группы выходов блока 9 ключей импульс программиро— вания с амплитудой +12,5В.

По окончании программирования бита на выходе 18 устанавливается лог."О", что означает окончание цикла программирования бита.

Снимается сигнал РСО, запрещая работу формирователя 2 и разрешая формирование на выходе 19 блока 7 импульса, служащего для стробирования данных во внутренний регистр программируемой микросхемы КР556РТ20 при чтении данных с выхода последней. Одновременно снимается сигнал ВД10 и разрешает выход программируемой микросхемы. Сигнал на выходе 19 формируется из сигнала "ВВ ДАННЧХ", поступающего с выхода микроЭВМ в момент чтения данных в память микроЭВМ.

Чтение слова инициализации производится аналогично описанному циклу чтения данных, за исключением того, что при этом сигнал ВД15 установлен в высокое состояние и переводит выход 18 формирователя 6 в низкое состбяние. С выхода последнего сигнал поступает на вход разрешения слова инициализации программируемой микросхемы.

С входов li 16, 22 устройства (фиг.)) снимаются сигналы ВДОО...ВД)5, РСО, РС!, в результате чего снимаются напряжения с входов программируемой микросхемы, и цикл оканчивается, Формула и з о б р е т е н и я

Устройство для программирования микросхем постоянной памяти, содержащее блок ключей, источник питания, формирователь сигналов управления, состоящий из дешифратора, блока управления ключами, формирователя им1564689

Вх0ды д 8CG ...МУ

Разреи ение выборка(ВД Я

8xad пияаниа 17 пульса запуска, блока управления источником питания, информационные входы дениАратора являются первой групПой инАормационных входов устройства, выходы дешиАратора соединены с входаМи блока управления, вход формирователяя импульса запуска является первым входом разрешения работы устройства, выход фор ырователя импульса запуска соединен со стробирующими входами деаифратора и блока управления источником питания, информационные входы блока управления источником питания вляются второй группой инАормационЙых входов устройства, выход блока управления источником питания соединен с первым входом задания режима работы источника питания, второй вход задания режима работы которого является вторым входом задания режима работы, устройства, выход источника питания является первым выходом устройства, выход блока управления ключами является первой группой выходов уст5 ройства, о т л и ч а ю щ е е с я тем, что, с целью упроц ения устройства, в него введены блок выборки и Аормирователь импульсов программирования, первый вход задания режима работы которого является третьим входом задания режима работы устройства, вход блока выборки является четвертым входом задания режима работы устройства, второй вход управления формирователя импульсов программирования соединен с выходом Аормирователя импульса запуска, выход Аормирователя импульсов программирования является вторым выходом : стройства, выход блока выборки является третьим выходом устройства, 1564689

Входы адреса ВЛО... ВЯ9-лог. О

Входы разрешениа

loidoptu(tg fO) Г.О

Вход ваквирооанаа 19

Вход пиааниа 17

Выход И, И...07

Вход разрою инациалцзац

8xud синхронного разрешения бь барки (ВД й)-™лоаО

Фие.У

Составитель Н, Шустов

Редактор И. Петрова Техред М.Дидык Корректор С. Шевкун

Заказ 1164

Тираж 486

Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101