Запоминающее устройство с коррекцией ошибок

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств высоконадежных вычислительных систем. Цель изобретения - упрощение и повышение быстродействия. Устройство содержит регистр 1 адреса, блоки 2 и 3 памяти данных, блоки 4 и 5 памяти контрольной информации, вычислители 6-9 синдрома и корректоры 10-13. 1 з.п. ф-лы, 2 ил., 1 табл.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

091 (11) А1 (51)5 С 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГННТ СССР (21) 4353943/24-24 (22) 06.11 ° 87 (46) 15.05.90. Бюп. М 18 (72) В.К.Габелко, Н.Б.Нифонтов, M.Н.Рогов и В,Л. Сафронов (53) 681. 32 7(088. 8) (56) Авторское свидетельство СССР

Р 1239751, кп, G 11 С 29/00, 1985.

Авторское свидетельство СССР

Ф 1276146, кл. G 11 С 29/00, 1985.

2 (54) . ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ОШИБОК (57) Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств высоконадежных вычислительных систем. Цель изобретения— упрощение и повышение быстродействия.

Устройство содержит регистр 1 адреса, блоки 2 и 3 памяти данных, блоки 4 и 5 памяти контрольной информации, вычислители 6-9 синдрома и корректоры 10-13. 1 з,п.ф-.лы, 2 ил. 1 табл.

1564696

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств высоконадежных вычислитель5 ных систем.

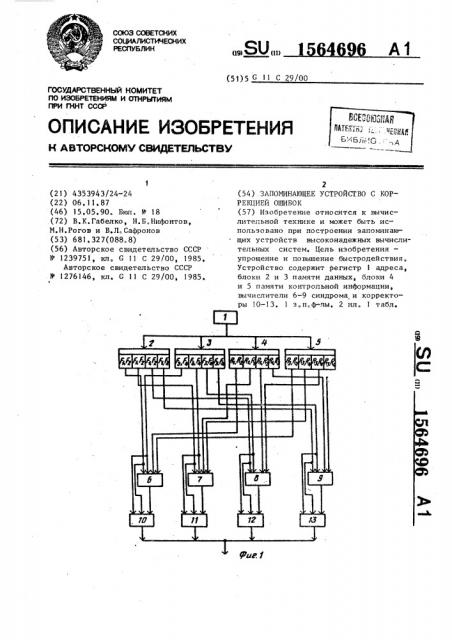

Цель изобретения — упрощение и повышение быстродействия устройства, На фиг,1 изображена функциональная схема запоминающего устройства

;для двубайтового формата данных, в котором применены БИС ЗУ с байтовой органиэацией; на фиг.2 — функциональная схема корректора.

Устройство содержит (фиг.1) регистр 1 адреса, блоки 2 и 3 памяти данных, блоки 4 и 5 памяти контрольной информации, вычислители 6-9 син дрома, корректоры 10-13, Каждый из корректоров 10-13 содер- 2р жит (фиг. 2) элемент И-НЕ 14, первую группу элементов И 15-18, первый 19 и второй 20 элементы И, вторую группу элементов h 21-24, первую и вторую группы элементов ИСКЛЮЧАЮЦ1ЕЕ ИЛИ 25- 25

28 и 29-32 соответственно.

Разрядность каждого из блоков 2 и 3 памяти равна одному байту и равна

;половине разрядности кодов хранимой в устройстве информации. Разрядность 30 каждого из блоков 4 и 5 памяти равна разрядности блоков 2 и 3, Количество входов каждого из вычислителей 6-9 синдрома равно восьми„ Количество входов каждого из корректоров 10-13 рав35 но девяти, а количество выходов— четырем, Устройство работает следующим образом.

При записи на информационный вход 40 устройства 1 (на фиг.1 не показан) поступает 16-разрядная основная информация (данные),разбитая на два байта, и 16 контрольных разрядов (контрольная информация) также разбитые на два байта. При этом основная информация поступает на блоки 2 и 3 памяти, а контрольная — на блоки 4 и 5. Таким образом, в память записываются одновременно 32 разряда. Конт- 50 рольные разряды образуются на информационных по алгоритму известного корректирующего кода для пачек ошибок. Здесь используется вариант этого кода, ориентированный на двухраэрядные пачки.

При считывании считываемое 32-разрядное слово интерпретируется (в со= ответствии с алгоритмом кодирования) как совокупность четырех 8-разрядных слоев. Для их образования разрядная сетка каждого из четырех байтов условно разбивается на четыре группы по два соседних разряда и в качестве любого одного из четырех упомянутых слов рассматривается совокупность таких двуразрядных групп с одинаковым расположением в пределах разрядной сетки каждого байта„ Декодирование и коррекция осуществляются по четырем независимым каналам, соответствующим каждому из слов„

Рассмотрим подробнее работу блоков, изображенных на фиг,l. адрес ячейки, к которой необходимо обратиться, записывается в регистр 1 адреса. По этому адресу происходит обращение к блокам 2-5 памяти одновременно. B блок 2 памяти .записывается первый байт информации, в блок 3 памяти — второй байт информации, B блоки 4 и 5 памяти записываются по этому же адресу контрольные числа, зависящие от информации, поступающей на блоки 2 и 3 памяти, Эти контрольные числа образуются следующим образом.

Условно каждый байт информации, поступающей на блоки 2 и 3 и блоки 4 и 5 памяти, разбивается на четыре группы по два соседних разряда. Содержимое групп блоков 4 и 5 памяти образуется из содержимого одинаково расположенных двухразрядных групп первого и второго байтов. Два разряда данных иэ первой группы первого байта (обозначим их через Р< и Fz) и два разряда данных из первой группы второго байта (обозначим их через F> и Fq) определяют четыре к6нтрольных разряда (две группы), два из которых (обозначим их через К и К ) образуют первую двухраэрядную группу для блока 4 памяти,а два (обозначим их через R > и R<) образуют первую двухразрядную группу для блока 5 памяти. !

Эти первые два разряда контрольных чисел в блоках 4 и 5 (R,,R< и К К ) памяти образуются из первых двух разрядов информационных байтов (Р, Р< и F>,F<) с помощью только операции сложения по модулю два по следующему правилу:

R1- =F О+ Рэ, F2@ Рф в

1564696

R = F,О+ F,O+ F, К, = F,О Е,ЕР,.

Аналогично образуются разряды трех оставшихся групп контрольных чисел для блоков 4 и 5 памяти.

При считывании информации из блоков 2 и 3 памяти поступает на вычислители 6-9 синдрома и корректоры 10-13, а информация, считанная из блоков 4 и 5, поступает только на вычислители 6-9, При этом на вход вычислите- . ля 6 синдрома поступают, разряды, относящиеся.к первым двухразрядным группам блоков 2-5 памяти. На вычислйтель 7 синдрома поступают разряды втор х групп блоков 2-5 и т.д.

Вычисление разрядов каждого синдрома (обовиачим их через S,-SI) ироиаводится также только с помощью опера- 20 ции сложения по модулю два следующим образом:

S = FsG) F О+, р

Еае Е4© Ras

S = F, a+ R,В R, 25

S = Р,Ю К ЯК,, S и = F@ОQ+ +FqO+ R ® R .

В таблице представлены значения одного из синдромов (для остальных трех синдромов получаются аналогичные 30 значения), соответствующие возможным . ошибкам при неисправности одного из блоков 2-5 памяти и при правильной работе.

На вход каждого корректора 10-13 поступают пять разрядов с вычислителей 6-9 соответственно, Кроме того, на другие входы корректоров 10-13 поступает информация, считанная из блоков 2-3 памяти. Значения синдрома при 40 неисправности одного блока памяти и .правильной.,работе приведено в таблице.

Считанная информация (разрядыF<-F< )

: поступает на один из входов элементов 45

ИСКЛЮЧАЮЩЕЕ ИЛИ 25-28 и в случае правильной работы проходит на их выходы беэ инверсии. В случае правильной работы элементы 29- 12 ИСКЛЮЧАЮЩЕЕ ИЛИ также пропускают данные без инверсии.

На.оставшиеся входы элементов 25-28

ИСКЛЮЧАЮЩЕЕ ИЛИ поступают сигналы с выходов элементов И 21-24 соответственно, на оставшиеся вторые входы элементов 29-30 ИС1ПЮЧАЮЩЕЕ ИЛИ по55 ступает сигнал с выхода элемента

И 19, а на оставшиеся вторые входы элементов 31-32 ИСКЛЮЧАЮЩЕЕ ИЛИ вЂ” с выхода элемента И 20.

В случае возникновения одиночной, ошибки в считанной информации F -F на выходе элемента И-НЕ 14 образуется высокий потенциал, и высокий потенциал образуется на одном иэ выходов элементов И 15-18. При этом происходит коррекция (инвертирование) одного из разрядов F -F4, на выходе одного иэ элементов 25-28 ИСКЛЮЧАЮЩЕЕ ИЛИ, причем в элементах 29-32 ИСКПЮЧАЮЩЕЕ ИЛИ инверсии не происходит, так как выходы элементов И 19, 20 имеют низкий потенциал (см.табл.),В случае возникновения одной из парных ошибок в

F -Fq инвертирование считанной информации происходит либо с помощью элементов 29-30 ИСКЛЮЧАЮЩЕЕ ИЛИ, либо с помощью элементов 31-32 ИСКЛЮЧАЮЩЕЕ

ИЛИ в зависимости от уровня напряжения на выходе элементов И 19 и 20. При этом выход элемента И-НЕ 14 имеет низкий потенциал и инвертирования в элементах 25-28 ИСКЛЮЧАЮЩЕЕ ИЛИ не происходит. Не происходит инвертирования в элементах 25-32 ИСКЛЮЧАКЩЕЕ ИЛИ и в тех же случаях, если произошла одиночная или парная ошибка в разрядах

R -В.

Во вссх случаях, возникающих при неисправностях одного из блоков 2-5 памяти, на выходе элементов 29-32

ИСТОЧАЮЩЕЕ ИЛИ получается правильная информация. формула изобретения

1. Запоминающее устройство с коррекцией ошибок, содержащее блоки памяти данных, блоки памяти контрольной информации, вычислители синдрома и корректоры, причем адресные входы блоков памяти поразрядно объединены и являются адресными входами устройства, выходы корректоров являются информационными выходами устройства, о т л и— ч а ю щ е е с я тем, что, с целью упрощения и повышения быстродействия устройства, в нем i-й вход (i--1,2)

j-го вычислителя синдрома и i-й информационный вход j-го корректора (j=1,4) объединены и подключены к

j-w; выходу i-ro блока памяти данных, k-к вход (1с=3,4) j-го вычислителя синдрома подключен к j-му выходу (k-2)-го блока памяти контрольной информации, управляющий вход каждого корректора соединен с выходом соответствукщего вычислителя синдрома.

1564696

2, Устройство по п.1,о т л и ч а ющ е е с я тем, что каждый корректор содержит элемент И-НЕ, первую и вторфю группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первую и вторую группы элементов И, первый и второй элементы И, причем выходы элементов И первой группы подключены к первым входам соответствУющих элементов И второй группы,вто- !0 рЩе входы которых соединены с выходом элемента И-НЕ, выходы элементов И в орой группы подключены к первым в одам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ перв и группы, выходы которых соединены с,первыми входами элементов ИСКЛЮЧАЮЩ Е ИЛИ второй группы, выходы которых

1 я ляются выходами корректора, вторые в)соды первого и второго элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы подклю- 20 чены к выходу первого элемеета И, вторые входы третьего и четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы соединены с выходом второго элемента И, первый и второй входы первого элемента И . подключены соответственно к выходам первого и второго элементов И первой группы, первый и второй входы второго элемента И подключены соответственно к выходам третьего и четвертого элементов И первой группы, вторые входы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы являются первым информационным входом корректора, вторые входы третьего и четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы являются вторым информационным входом корректора, входы элементов И первой группы и элемента И-НЕ являются управляющим входом корректора.

Двоичное значение синдрома ДесятичНеисправные р аз ряды ное значе"! ние синдрома

0 О О

О О 1

1 О О

О 0 О

1 1 О

О 1 О

1 О 1.

О 1 О.

О О. 1

1 О 1

1 О

1 1

О 1 1

Все исправны

Е

Е

Е

Е

К

Вэ

Rg

Г и F

F>v F<

К(и R

R>z R<

О

О

О

О . О

1

0

1

О

О

О

1 !

1

О

О

18 ,9

17

12

3

27

29

1564696 бчет0ииь!6 дань!В С453

p+>P+46I Гиндроиа

Тираж 485

Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул. Гагарина, 101

Редактор А.Долинич

Заказ 1164

Составитель В,Рудаков

Техред М.Дидык Корректор О,Ципле