Устройство для обмена данными между процессорами

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при создании многопроцессорных вычислительных систем. Целью изобретения является повышение надежности системы за счет сокращения объема оборудования. Поставленная цель достигается тем, что в устройстве, содержащем K блоков обмена, каждый блок обмена содержит регистр данных, регистр адреса, блок памяти, коммутатор адреса, коммутатор данных, три триггера, инвертор, элемент И 19 и одновибратор 20. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

1566361 A 1 (19) (11) (51)5 G 06 F 15/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСН0МУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПO ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4459689/24-24 (22) 13.07.88 (46) 23.05.90. Бюл. Р 19 (71) Особое конструкторско-техноло- гическое бюро "Ларсек" при Тольяттинском политехническом институте (72) С.В.Редькин и С.Б.Плешаков (53) 681.325(088.8) (56) Валях Е. Последовательно-парал-лельные вычисления. И.: Иир, 1985, с. 134, рис, ?2, с. 140, рис ?4.

Авторское свидетельство СССР

1"- 1277127, кл. G 06 F 13/00, 1985.

2 (54) У(ЛРО11СТВО Д.1И ОБИДНА ДАННЬ11Я

MLigP Н1 ОЦ1. ССО1 АИИ (57) Изобретение относится к вычислительной технике и может быть использовано при создании многопроцессорных вычислительных систем. Целью изобретения является повышение надежности системы за счет сокращения объема оборудования. Поставленная цель достигается тем, что в устройстве, содержащем k блоков обмена, каждый блок обмена содержит регистр данных, регистр адреса, блок памяти„ коммутатор адреса, коммутатор данных, три триггера, инвертор, элемент И 19 и одновибратор 20. 2 ил.

1566361

Изобретение относится к вычислительной технике и может быть использовано при "оздании многопроцессорных вычислительных систем.

Пель изобретения — повышение надежности систем за счет сокращения объема оборудования.

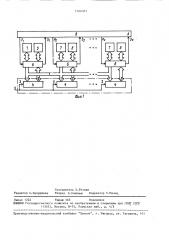

На фиг. 1 изображена блок-схема многопроцессорной системы, частью ко- 1О торой является предлагаемое устройство, на фиг. 2 — схема блока обмена.

Устройство, входящее в состав мно-. гопроцессорной системы (фиг. 1), содержит системную магистраль 1 записи, 1

К локальных магистралей 2 чтения, тактовый вход 3 и К блоков 4 обмена.

Кроме того, на фиг. 1 приведены не входящие в состав устройства процес.оры 5„ блоки 6 шинных формирователей,. блоки 7 основной памяти и арбитр.H.

Блок обмена (фиг. 2) содержит входы/выходы 9 для подключения к системной и локальной магистралям, регистр !0 данных, регистр 11 адреса, блок 12 памяти, коммутатор 13 адреса, коммутатор 14 данных, триггеры 15 - 17, инвертор 18, элемент И 19, одновибратор 20.

ЗО

Устройство работает следующим образом.

Каждый процессор 5(i) (.=1,2,. ° .,К)

1 многопроцессорной системы может обмениваться данными в одном из трех режимов: работа с блоком основной памяти 7 (i), запись информации в устройство обмена данными и чтение информации из соответствующего блока 4, При этом в системе команд процессоров нет специальных команд обмена, блоки 4 являются равноценной памятью процессора и отличаются от основной памяти только диапазоном адресов„ В зависимости от адресной час- 5 ти команды шинный формирователь 6 (i) подключает к процессору 5 (i) либо блок основной памяти 7 (i) либо системную магистраль 1, либо локальную магистраль 2 (i).

При записи информации в блок 4 . процессор 5 (i) устанавливает на своих выходах адрес ячейки блока 4, опеЬанд и выдает сигнал записи. Ыинный формирователь 6 (i) вырабатывает сиг55 нал запроса обмена и выдает его на вход арбитра 8, который в соответствии с заданной дисциплиной обслуживания запросов обеспечивает очередность захвата системной магистрали 1.

Если системная магистраль 1 свободна, арбитр 8 выдает ответный сигнал разрешения обмена. По этому сигналу шинный формирователь 6 (1) выдает на системную магистраль 1 адрес, операнд и сигнал записи, которые поступают одновременно на все блоки обмена 4 (I)4 (К). При этом по одному и тому же адресу во все блоки обмена будет записана одна и та же информация.

При записи информации в блок обмена 4 адрес ячейки памяти и операнд заносятся соответственно в регистр

11 адреса и в регистр 10 данных по сигналу с выхода триггера 15, который взводится по приходу сигнала записи. На этом обмен по системной магистрали 1 заканчивается. Если при этом не выполняется чтение по локальной магистрали 2 (i) то тактовым импульсом с выхода инвертора 18 взводится триггер 16 и посылает сигнал на первый управляющий вход коммутатора 13 адреса, который подключает выход регистра адреса 11 к адресному входу блока 12 памяти. Тем же сигналом блокируется триггер 17 и запускается одновибратор 20. Импульс с его выхода сбрасывает триггер 15 и инициирует запись операнда с выхода регистра 10 данных в блок 12 памяти по адресу, занесенному в регистр 11 адреса. Следующим тактовым импульсом триггер 16 сбрасывается.

Если же в момент записи по системной магистрали выполнялось чтение по локальной магистрали 2 (i), то сигналом с выхода триггера 17 триггер 16 блокируется и процесс переписи операнда в блок 18 памяти задерживается до окончания цикла чтения. Аналогично цикл чтения не может быть выполнен до окончания цикла записи, если триггер 16 был установлен в блоке обмена

4 () раньше сигнала чтения.

В режиме чтения информации из блока обмена 4 (1) процессор 5 () выдает в локальную магистраль 2 (i) адрес и сигнал чтения. Если запись операнда уже закончилась, то сигнал на выходе триггера 16 отсутствует и тактовым импульсом с входа 3 блока 4 (i) обмена взводится триггер 17. Его выходной сигнал блокирует триггер 16 и поступает на второй управляющий вхоц коммутатора 13 адреса, который подключает второй адресный вход к ад5 15663 ресному входу блока 12 памяти. Этот же сигнал проходит через элемент И 19, открывает коммутатор 14 данных и поступает на выход разрешения чтения.

Операнд из выбранной ячейки памяти

5 блока 12 памяти поступает через коммутатор 14 данных на информационный выход блока 4 (i) обмена и далее в локальную магистраль 2 (i) чтения. После приема операнда процессор 5 (i) сбрасывает сигнал чтения. При этом снимается сигнал разрешения чтения и очередным тактовым импульсов сбрасывается триггер 17.

Формулаизобретения

Устройство для обмена данными меж ду процессорами, содержащее К блоков обмена, причем первые адресные входы 20 и вход признака чтения i-го (i=i

К) блока обмена являются одноименными 1-ми входами устройства, выход данных и выход разрешения чтения i-го блока обмена является одноименными 25

i-ми выходами устройства, о т л и— ч а ю щ е е с я тем, что, с целью повышения надежности за счет сокращения объема оборудования, второй адресный вход, вход данных, вход при- 39 знака записи всех блоков обмена через системную магистраль соединены между собой и являются одноименными входами устройства для подключения процессоров, тактовые входы всех бло35 ков обмена соединены между собой и подключены к тактовому входу устройства, а каждый блок обмена содержит регистр данных, регистр адреса, блок памяти, коммутатор адреса, коммутатор данных, три триггера, инвертор, элемент И и одновибратор, выход которого подключен к входу сброса первого

61 6 триггера и к входу записи блока памяI ти, адресный вход которого подключен . к выходу коммутатора адреса, первый и второй информационный входы которого подключены соответс:венно к выходу регистра адреса и первому адресному входу блока обмена, второй адресный вход которого подключен к информационному входу регистра адреса, вход записи которого подключен к входу записи регистра данных, к выходу первого триггера и к информационному входу второго триггера, выход которого подключен к входу одновибратора, к входу сброса третьего триггера и к первому управляющему входу коммутатора адреса, второй управляющий вход которого подключен к входу сброса второго триггера, к выходу третьего триггера, и к первому входу элемента

И, выход которого подключен к входу управления коммутатора данных и является выходом разрешения чтения блока обмена, вход чтения которого подключен к второму входу элемента И и к информационному входу третьего триггера, тактовый вход которого подключен к тактовому входу блока обмена и к входу инвертора, выход которого подключен к тактовому входу второго триггера, информационный вход блока обмена подключен к информационному входу регистра данных, выход которого подключен к информационному входу блока памяти, выход которо" î подключен к информационному входу коммутатора данных, выход которого является информационным выходом блока обмена, вход записи которого подключен к тактовому входу первого триггера, информационный вход которого подключен к уровню логической единицы, 1566361

Составитель Б.Резван

Редактор С.Патрушева Техред Л.Олийнык Корректор T.Ìàëåö

Заказ 1222 Тираж 563 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113033, Москва, И-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r, Ужгород, ул. Гагарина, 101