Устройство для решения систем линейных алгебраических уравнений

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано в качестве процессора для решения систем линейных алгебраических уравнений. Цель изобретения - повышение быстродействия. Поставленная цель достиается тем, что устройство содержит N вычислительных блоков 1, где N - порядок решаемой системы линейных алгебраических уравнений, блок 4 анализа, блок 5 синхронизации и борк 6 формирования импульсов. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51) 5 С 06 F 15/324

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H A BT0PCH0MV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ по изОБРетениям и ОтнРцтиям

ПРИ ГКНТ СССР

1 (21) 4475894/24-24 (22) 23.08,88 (46) 23.05.90. Бюл. l» 9 (71) Физико-механический институт им. Г.В.Карпенко АН УССР (72) А.Е.Батюк, В.B.Грицик, В.Я.Мыхальчишин и И.R.Михальчишин (53) 681.325(088.8) (56) Авторское свидетельство СССР 1 813445, кл. G 06 F 15/324, !981

Авторское свидетельство СССР Ю f462353, кл. G 06 F 15/324, 1987.

„„Я0„„1566366 А 1

2 (54) УСТРОЙСТВО ДЛЯ РЕИЕНИЯ СИСТЕМ

ЛИНЕЙНЫХ АЛГЕБРАИЧЕСКИХ УРАВНЕНИЙ (57) Изобретение относится к циФровой вычислительной технике и может быть использовано в качестве процессора для решения систем линейных алгебраических уравнений. Цель изобретения повышение быстродействия. Поставленная цель достигается тем, что устройство содержит п вычислительных блоков 1. где n — порядок решаемой системы линейных алгебраических уравнений. блок 4 анализа, блок 5 синхронизации и блок 6 Формирования импульсов. 3 ил.

1566366

Изобретение относится к цифровой вычислительной технике и может быть использовано в качестве процессора для решения систем линейных алгебраических уравнений °

Цель изобретения — повышение быстродействия устройства.

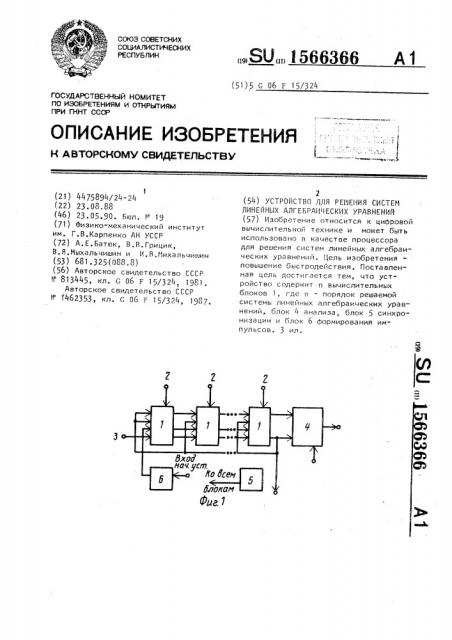

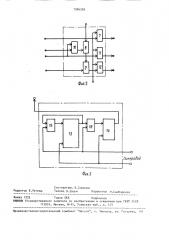

На фиг..l приведена схема устройства для решения систем линейных алгебраических уравнений; на фиг. 2— схема блока вычислений; на фиг. схема блока формирования импульсов.

Устройство содержит и блоков 1. вычислений, где и - порядок решаемой системы линейных алгебраических уравнений, входы 2 матрицы коэффициентов системы линейных алгебраических уравнений устройства, вход 3 свободных членов системы линейных алгебраических уравнений устройства, блок 4 анализа, блок 5 синхронизации и блок

6 формирования импульсов.

Блок 1 вычислений содержит первый регистр 7, умножитель 8, сумматор

g второй регистр 10, триггер 11 и третий регистр 12. Блок 6 формирования импульсов содержит счетчик 13, триггер 14, первый 15 и второй 16 элементы И.

Устройство предназначено для нахождения решения системы линейных алгебраических уравнений

СХ = dt где С - невырожденная матрица размерности и и;

d — заданный вектор размерности и, инерционным методом Якоби

X = Х + i(СХ - d)

k t k c

1с

АХ + В. ,-дз k — номер итерации; с — итерационный параметр;

А Е + С C - матрицы перехода (E - единичная матрица).

Устройство работает:следующим I образом.

Перед началом решения системы линейных алгебраических уравнений в блок 4 анализа записывается код порога, задаюций точность решения системы линейных алгебраических уравнений. В блок б формирования импульсов записывается число и. Блок б формирования импульсов генерирует управляющие импульсы для блоков 1 вычислений через каждые и тактов. За начальные значения компонент вектора неизвестных принимаются значения, зафиксированные в блоках 1 после включения прибора. На каждом такте работы устройства в каждом блоке 1 вычислений реализуется операция умножения числа на первом информационном входе блока 1 и числа, записанного

10 в регистре 10 блока i, и затем выполняется сложение полученного произведения с числом, поступающим на второй информационный вход блока 1 вы15 числений в данном такте. Все блоки

1 через четвертые информационные входы соединены с первым выходом и-ro блока 1 вычислений.

Число в регистр 10 i-co блока 1 записывается через четвертый информационный вход ° Запись осуществляется под воздействием импульса, поступаюц|его с управляющего входа блока 1 вычислений на вход записи/считывания

25 соответствующего регистра 10. Данный импульс появляется на выходе блока

6 формирования импульсов через каждьк и тактов в промежутке между и-м и (n + 1)-м тактами.Под воздействием тактовых импульсов этот импульс передвигается от одного триггера 11 к другому, записывая при этом информацию в регистры 10 соответствующих блоков 1 вычислений. В каждом триггере 11 данный импульс задерживается

35 на один такт. Таким образом считывание информации с первого выхода i-ro блока вычислений, где i = 1,п, осуществляется в каждом такте, а .изменение информации в регистре 10 (i + 1) — ro блока 1 вычислений осуществляется в каждом (i + п)(k — 1)-м, такте, где k = 1,п; m — число цик лов решения задачи.

45 Блок 4 анализа предназначен l» покомпонентной проверки точности решения системы линейных алгебраических уравнений, и в нем осуществляется покомпонентное сравнение текущего вектора решения с предыдущим. Компоненты текущего вектора решения поступают на блок 4 анализа с первого выхода и-го блока 1 вычисления, а компоненты предыдущего вектора решения — с второго выхода и-го блока 1 .вычислений. В каждом такте работы устройства в блоке 4 анализа вычисляется значение 1 Х; — Х, J и происходит сравнение этого значения с

5 15663 порогом, задающим точность решения системы уравнений.

Когда в данном цикле решения системы уравнений, имеющем и тактов, хотя бы одна из компонент вектора решения не удовлетворяет заданной точности, то нулевое состояние на выходе блока 4 сохраняется до конца цикла, обозначая, что определенное решение не удовлетворяет заданной точности и необходимо продолжить итерационный процесс решения.

Формула изобретения

Устройство для решения систем линейных алгебраических уравнений, содержащее с первого по и-й блоки вычислений, где n - порядок решаемой щ системы линейных алгебраических уравнений, блок анализа и блок синхронизации, причем с первого по и-й входы матрицы коэффициентов системы линейных алгебраических уравнений устрой- р5 ства подключены соответственно к первым информационным входам блоков вычислений с первого по п-й, первый выход -го блока вычислений, где

1, ..., n — 1, подключен к второму информационному входу (i+1)-го блока вычислений, вход свободных членов системы линейных алгебраических уравнений устройства подключен к второму информационному входу первого блока вычислений, первый выход и-го блока вычислений подключен к первому информационному входу блока анализа и к выходу результата устройства, вход величины точности решения кото40 рого подключен к второму информацион ному входу блока анализа, выход которого подключен к выходу признака останова устройства, вход запуска которого подключен к входу запуска блока синхронизации, выход которого подключен к входам синхронизации блоков вычислений с первого по и-й и блока анализа, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит блок формирования импульсов, причем второй и третий выходы i-го блока вычислений подключены соответственно к третьему информационному и к управляющему входам (i + 1)-го блока вычислений, первый выход и-го блока вычислений подключен к третьему, четвертому ин66 ь формационным входам первого блока ! вычислений и к четвертым информационным входам блоков вычислений с второго по п-й, второй выход и-го блока вычислений подключен к третьему информационному входу блока анализа, вход начальной установки устройства подключен к информационному входу блока формирования импульсов, выход которого подключен к управляющему входу первого блока вычислений, выход блока синхронизации подключен к входу синхронизации блока формирования импульсов, при этом каждый блок вычислений содержит умножитель, сумматор, с первого по третий регистры и триггер, причем первый. второй, третий и четвертый информационные входы блока вычислений подключены соответственно к первому информационному входу умножителя, к первому информационному входу сумматора, к информационному входу первого регист" ра и к информационному входу второго регистра, выход которого подключен к второму информационному входу умножителя, выход которого подключен к второму информационному входу сумматора, выход которого подключен к информационному входу третьего регистра, управляющий вход блока вычислений подключен к входу записи-считывания второго регистра и к информационному входу триггера, вход синхронизации блока вычислений подключен к синхровходу триггера и к входам записи-считывания первого и третьего регистров, выходы третьего регистра, первого регистра и триггера подключены соответственно к первому, второму и третьему выходам блока вычислений,при этом блок формирования импульсов содержит счетчик, триггер и два элемента И, причем вход синхронизации блока формирования импульсов подключен к счетному входу счетчика и к синхровходу триггера, выход которого подключен к выходу блока формирования импульсов, информационный вход которого подключен к первым входам первого и второго элементов И, выходы которых подключень соответственно к информационным входам счетчика и триггера, выход переполнения счетчика подключен к вторым входам первого и второго элементов И.

1566366 иг.

Составитель В.Смирнов

Техред M.Äèäûê Корректор М.Самборская

Редактор В.Петраш

Заказ 1223 Тираж 565 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101