Устройство экранной памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в растровых дисплеях персональных ЭВМ и графических терминалах. Цель изобретения - повышение быстродействия устройства за счет увеличения скорости модификации битовой карты изображения в памяти и уменьшения среднего времени доступа к экранной памяти. Поставленная цель достигается тем, что устройство содержит блок 1 памяти, блок 2 синхронизации, регистр 3 адреса, интерфейсный блок 4, мультиплексор 5, счетчик 6 адреса, регистр 7 сдвига, буферный регистр 8, счетчик 9 цикла, блок 10 арбитража, вход-выход 11, информационный выход 12. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1

„„SU „„1566372 (51) 5 С 06 F 15/62

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

- Н ABT0PCHOMV СВИДЕТЕЛЬСТВУ (21) 4423 553/24-24 (22) 10.05.88 (46) 23. 05,90. Бюл. М 19 (72) l0.Â. александров и IO.Í. Савченко (53) 68 1.325(088.8) (56) Видеоконтроллер МРД 7220 фирмы

NFC. Техническое описание.

Видеоконтроллер Нц 6384 фирмы

Hitachi. Техническое описание.

Зая вка Японии Y 61-61408, кл. G 06 F 3/153, С 06 F 1/00, 1986.

МикроЭВМ "Электроника MC 0511"

У10.170.002. Техническое описание.

Микропроцессорные средства и системы. 1986, N 6, с. l4-16. (54) УСТРОЙСТВО ЭКРАННОЙ ПАМЯТИ (57) Изобретение относится к вычисли2 тельной технике и может быть использовано в растровых дисплеях персональных ЭВМ и графических терминалах.

Цель изобретения - повышение быстродействия устройства за счет увеличения скорости модификации битовой карты изображения в памяти и уменьшения среднего времени доступа к экранной памяти. Поставленная цель достигается тем, что устройство содержит блок 1 памяти, блок 2 синхронизации, регис; ð 3 адреса, интерфейсный блок 4, мультиплексор 5, счетчик

6 адреса, регистр 7 сдвига, буферный регистр 8, счетчик 9 цикла, блок 10 арбитража, вход-выход 11, информа ци" онный выход 12. 2 ил. )Z

15663 72

Изобретение от носится к вычислительной технике и может быль использова но в растровых дисплеях персональных ЭВМ и графических терминалах.

Цель изобретения - повышение бы5 стродейст вия устройст ва эа счет увеличения скорости модификации битовой карты изображения в памяти и уменьшения среднего времени доступа и экранной памяти.

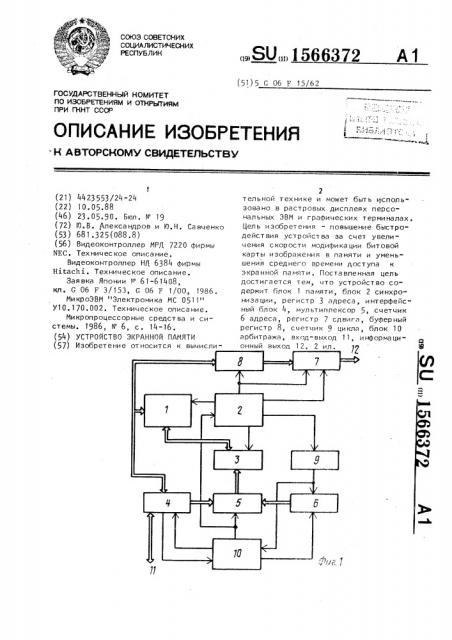

На фиг. 1 пока за на структурная схема устройства; на фиг. 2 - временная диаграмма разделения циклов памяти, Устройство содержит блок 1 памяти, блок 2 синхронизации, регистр 3 адреса, интерфейсный блок 4, мультиплексор 5, счетчик 6 адреса, регистр

7 сдвига, буферный регистр 8, счетчик 9 цикла и блок 10 арбитража. Уст- 20 ройство имеет вход-выход 11 и информационный выход 12.

Устройство работает следующим образомм.

При считывании из хранящейся в блоке 1 памяти битовой карты очередной строки телевизионного растра блок

2 синхронизации формирует непрерывную последовательность циклов памяти с периодом Т> При этом разрядность считываемого иэ блока 1 памяти слова для выдачи информа ции HB экран монитора и колич ест во бит на элемент и зображения выбраны таким образом, что для воспроизведения его на экра не необходимо считывать из блока 1 памяти по одному слову с периодом 2Т. Поэтому в отсутствие запросов на обмен с памятью со стороны процессора каждый первый из двух последовательных циклов памяти выделяется для считывания очередного слова из блока 1 памяти зап:,<си его в буферный регистр 8, что схематически показано на фиг.2 (нижняя штриховка на участках 1 и 2 диаграммы) .

Подсчет четных и нечетных циклов памяти производится c÷åT÷èêoì 9 цикла, по состоянию которого блок 10 арбитража в отсутствие запросов от интерфейсного блока 4 разрешает инкрементирование счетчика 6 адреса каждый нечетный цикл -и выработку строба записи слова иэ блока 1 памяти в hyферный регистр Я, При поступлении запросов на обмен со стороны интерфейсного блока 4 (эти моменты схематически показаны стрелками на фиг. 2) блок

1О арбитража ра зрешает обмен с блоком

1 памяти в следующем цикле (верхняя штриховка на участках 2, 4 и 5 диа— граммы, фиг.2), При этом, в зависимости от момента поступления запроса, для считывания и записи в буферный регистр 8 очередного слова видеост ро-. ки выделяется остающийся свободным цикл из текущей пары — либо второй, как на участках 4 и 5, либо первый, как на участке 3. Текущий адрес слова хранится на регистре 3 адреса, куда переписывается по сигналу от блока

2 синхронизации через мультиплексор

5 либо со счетчика 6 адреса, либо из интерфейсного блока 4, в зависимости от состояния блока 10 арбитража. Гиг— налы выборки для элементов памяти формируются блоком 2 синхронизации в каждом цикле, сигнал Запись выда—

pTcR интерфейсным блоком 4 в том случае, если текущий ци кл предста вляет собой цикл обмена с блоком 1 памяти и выполняется опера ция записи.

При ня т ый меха ни зм а рби т ража обеспечивает доступ к блоку 1 памяти в следующем цикле без нарушения процесса выдачи иэображения на экран мони-;ора и без помех на экране, Буферный регистр 8 введен в схему для обеспечения поступления очередного слова в регистр 7 сдвига через заданные промежутки времени, так как момент записи видеослова в буферный регистр

8 зависит от состояния блока 10 арбитража, а в регистр 7 сдвига очередное слово переписывается из буферного регистра S с периодом 2Т в конце ках<дого четного цикла блока 1 памяти, после чего поступает в виде групп разрядов (в зависимости от формата выдачи) на инфогча ционный выход 12, Блок 2 синхронизации (фиг.1) в состав контроллера управления ОЭУ предназначен для генерации последова тельности сигналов управления схемами блока 1 памяти в соответствии с их временной диаграммой. В частности, в

ПЭВМ "Электроника YK НЦ" применены микросхемы 03У динамического типа

К 565 РУ5, временная диаграмма их работы, состав и временные соотношения между сигналами управления приводятся в справочниках по интегральным ми кросхемам (сигналы Л@-А7, RAS, CAS) .

При создании более быстродейст вующих контроллеров, на которые рассчитано предлагаемое устройство, необходимо применять микросхемы памяти с умень5 1 r( шенным временем цикла, например с ra— тические ОЗУ типа К1Я2РУ10. В эт ом случае блек 2 синхронизации должен генерировать последовательность адресов, сигналов выборки и записи в соответствиии с временной диаграммой работы этой микросхемы (сигналы на шинах адреса, УР, СЕ, OE) .

Интерфейсный блок содержит средстваа для обеспечения временной диаграммы обмена по магистрали МПИ (g-BUS), принятой в качестве системной магистрали s ПЭВМ "Электроника

УК НЦ, Совместная работа блока 2 синхронизации и интерфейсного блока

4 обеспечивает доступ процессора к блоку 1 памяти по магистрали МПИ.

Блок 10 арбитража (фиг.11 представляет собой устройство анализа приоритета с двумя входами, выполненное по любой из известных схем с тем отличием, что приоритет процес— сора при обращении к видеопамяти изменяется в зависимости от того, поступает заявка на обмен в четном цикле памяти или в нечетном. Блок 10 арбитража является устройством анализа условного приоритета. В качестве условия анализа приоритетов в устройстве выступает состояние счетчика цикла. Этот счетчик отсчитывает четные и нечетные циклы блока памяти.

Запрос на обмен процессора с блоком

1 памяти в нечетном цикле имеет более высокий приоритет, а в четном более низкий, чем периодическая процедура чтения очередного слова данных из блока 1 памяти и записи его в буферный регистр 8. формула изобретения

Устройство экранной памяти, содержащее блок памяти, блок синхронизации, регистр адреса, интерфейсный блок> мультиплексор, счетчик адреса и регистр сдвига, причем синхровход блока памяти подключен к первому выходу блока синхрониза ции, второй выF>) 72

50 ход которого подключен к синхровходу регистра адреса, вход-выход которого подключен к адресному входу-выходу блока памяти, информационный вход-выход которого подключен к внутреннему входу-выходу интерфейсного бло ка, в не ш ни и вход — в ых од кот ор or o я вля ется входом-выходом уст ройст ва, выход интерфейсного блока подключен к первому информационному входу мультиплексора, второй информационный вход которого подключен к информационному выходу счетчика адреса, выход мультиплексора подключен к информа ционному входу регистра адреса, третий выход блока синхронизации подключен к входу сдвига регистра сдвига, выход которого является информационным выходом устройства, о т л и ч аю щ е е с я тем, что, с целью повышения быстродействия устройства за счет увеличения скорости модификации битовой карты изображения в памяти и уменьшения среднего времени доступа к экранной памяти, устройство содержит буферный регистр, с чет чи к ци кла и блок арбитража, причем вход записи буферного регистра подключен к входу записи регистра сдвига и к четвертому выходу блока синхронизации, выход буферного регист ра подключен к информационному входу регистра сдвига, информационный вход буферного регистра подключен к информационному входу-выходу блока памяти, вход блока синхронизации подключен к управляющему входу мультиплексора и к выходу состояния блока арбитража, вход управления приоритет ом которого подключен к выходу счетчика цикла и счетному входу счетчика адреса, вход разрешения счета которого подключен к Bblxo ду управления строкой блока арбитража, выход разрешения обмена и вход запроса которого подключены соответственно к входу разрешения и выходу запроса интерфейс> ого блока, счетный вход счетчика цикла подключен к пятому выходу блока синхронизации.

1566372

Ф 5 о

J t гт

Составитель С. Аверьянова

Редактор Н. Тупица Техред М.Дидык Корректор В, Кабаций

Заказ 1223 Тираж 5б3 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент",, r. Ужгород, ул. Гагарина, 101

1 г!

I T

I !