Устройство дешифрации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть применено в различных типах запоминающих устройств (ОЗУ, ПЗУ, ППЗУ, РПЗУ) для построения устройств дешифрации. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что устройство содержит коммутаторы 8 и элементы 7 разряда с соответствующими связями. Коммутаторы 8 подключают к входам 5, 6 устройства только один логический блок 1. В результате паразитная емкость входов 5,6 уменьшается. Следовательно, уменьшается и время перезаряда этой емкости. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИ Х

РЕСПУБЛИК (sl) 5 6 11 С 8/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 «.» х, ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГННТ СССР (21) 4404097 j24-24 (22) 04.04,88 (46) 23.05.90. Бюл. ¹ 19 (72) А.Ф.Хоменко, С.В.Высочина и

А.Г.Солод (53) 681.327.6 (088. B) (56) Петросян О,А. и др. Схемотехника БИС постоянных запоминающих устройств.—

М,: Радио и связь, 1987, с. 74, рис, 2. 3.

Алексенко А,Г., Шагурин И.И, Микросхемотехника, — M.: Радио и связь, 1982, с. 267, рис. 7. 16 и с. 142, рис. 323.

„„SU„„1566408 А 1

2 (54) УСТРОЙСТВО ДЕШИФРАЦИИ (57) Изобретение относится к вычислительной технике и может быть применено в различных типах запоминающих устройств (ОЗУ, ПЗУ, ППЗУ, РПЗУ) для построения устройств дешифрации. Цель изобретения— повышение быстродействия устройства, Поставленная цель достигается тем, что устройство содержит коммутаторы 8 и элементы 7 разряда с соответствующими связями. Коммутаторы 8 подключают к входам 5, 6 устройства только один логический блок 1. В результате параэитная емкость входов 5, 6 уменьшается. Следовательно, уменьшается и время перезаряда этой емкости. 1 ил. х„

1566408

Составитель С.Королев

Редактор Н.Тупица Техред М.Моргентал Корректор М.Самборская

Заказ 1225 Тираж 484 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

Изобретение относится к вычислительной технике и может быть применено в различных типах запоминающих устройств (ОЗУ, ПЗУ, ППЗУ, РПЗУ) для построения устройств дешифрации.

Цель изобретения — повышение быстродействия устройства.

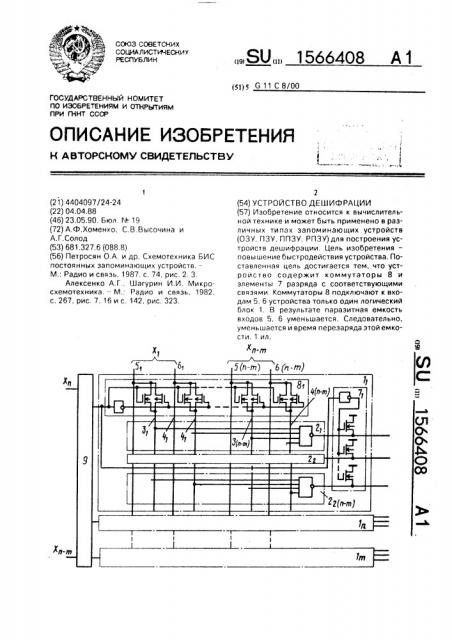

На чертеже представлена блок-схема устройства дешифрации.

Устройство дешифрации содержит логические блоки 1, элементы И 2, прямые 3 и инверсные 4 адресные шины, прямые 5 и инверсные 6 входы второй группы устройства, элементы 7 разряда, коммутаторы 8 и дешифратор 9. При этом коммутаторы 8, элементы И 2, элемент 7, прямые 3 и инверсные 4 адресные шины представляют логический блок 1.

Устройство работает следующим образом.

При подаче адресных сигналов дешифратор 9 старших разрядов обрабатывает их, при этом на одном иэ выбранных выходов дешифратора 9 старших разрядов появляется высокий потенциал. При этом коммутаторы 8 осуществляют подключение прямых 3 и инверсных 4 адресных шин к прямым 5 и инверсным 6 входам внутри данного блока

1. Одновременно происходит отключение транзисторов разряда в элементе 7 разряда от выходов устройства в выбранном блоке 1.

Выбранная адресная комбинация в виде высоких и низких потенциалов с входов 5 и

6 через блок коммутаторов 8, группу прямых

3 и инверсных 4 шин поступает на входы

5 элементов И 2, и на одном из их выходов появляется высокий потенциал. Очередная смена адресных сигналов вызывает обработку их по изложенному порядку в зависимости от кодовой ситуации адресных

10 сигналов на входе дешифратора 9 и входах

5 и 6.

Формула изобретения

Устройство дешифрации, содержащее дешифратор, входы которого являются вхо15 дами первой группы устройства, логические блоки, каждый из которых состоит из элементов И, выходы которых являются выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия ус20 тройства, в каждый логический блок введены коммутаторы и элемент разряда, выходы которого соединены с выходами соответствующих элементов И, а вход соединен с входами выборки коммутаторов, 25 выходы которых соединены с соответствующими входами элементов И, соответствующие информационные входы коммутаторов всех логических блоков объединены и являются входами второй группы устройства, а

30 входы элементов разряда соединены с соответствующими выходами дешифратора.