Устройство считывания для программируемой логической матрицы

Иллюстрации

Показать всеРеферат

Изобретение относится к микроэлектронике и предназначено для использования в программируемых логических интегральных схемах, изготовленных по КМОП-технологии. Целью изобретения является расширение функциональных возможностей устройства за счет отключения напряжения питания в режиме программирования. Устройство содержит формирователь напряжения питания, схему сброса триггера и ключевой транзистор. Вход формирователя напряжения питания является входом установки режима работы устройства, сток ключевого транзистора - информационным входом устройства. Схема сброса триггера состоит из двух ключевых транзисторов, затворы которых объединены и соединены с входом формирователя напряжения питания, а стоки соединены соответственно с входом и выходом триггера. 1 ил.

СОЮЗ СО6ЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (si) s 6 11 С 11/40

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ П(НТ СССР (21) 4454944/24-24 (22) 05.07.88 (46) 23.05.90. Бюл. № 19 (72) В.П.Сидоренко. Н.Б.Груданов, В.Е.Савицкий и В.Б,Невзоров (53) 381.327.66 (088.8) (56)! ЕЕЕ J. Solid — State circoits, ч.SC — 21, ¹ 55,, 11998866, р. 769 — 770.

Там же, р. 768 769. (54) УСТРОЙСТВО СЧИТ ЫВАНИЯ ДЛЯ

ПРОГРАММИРУЕМОЙ ЛОГИЧЕСКОЙ МАТРИЦЫ (57) Изобретение относится к микроэлектронике и предназначено для использования в программируемых логических интегральных схемах, изготовленных по КМОП-техноИзобретение относится к микроэлектронике и предназначено для использования в программируемых логических интегральных схемах, изготовленных по КМОП-технологии, Цель изобретения — расширение функциональных возможностей устройства считывания.

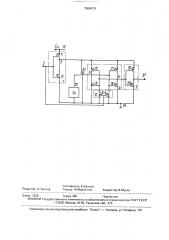

На чертеже представлена электрическая схема устройства.

На схеме обозначены формирователь 1 напряжения питания, вход 2 установки режима работы устройства, выход 3 формирователя напряжения питания, несимметричный триггер 4, вход 5 и выход 6 несимметричного триггера, выходной инвертор 7. первый ключевой транзистор 8 и второй ключевой транзистор 9 схемы 10 обнуления несимметричного триггера, нагрузочный транзистор 11 и переключающий транзистор 12 формирователя напряжения питаÄÄSUÄÄ 1566410 А 1 логии, Целью изобретения является расширение функциональных воэможностей устройства за счет отключения напряжения питания в режиме программирования. Устройство содержит формирователь напряжения питания, схему сброса триггера и ключевой транзистор. Вход формирователя напряжения питания является входом установки режима работы устройства, сток ключевого транзистора — информационным гходом устроиства. схема сброса триггера состоит из двух ключевых транзисторов. затворы которых обьединены и соединены с входом форл1ирователя напряжения питания. а стоки соединены соответственно с входом и выходом триггера. 1 ил. ния, шина 13 напряжения питания и шина

14 нулевого потенциала устроиства, нагрузочный транзистор 15, первыи переключающий транзистор 16. второй нагрузочный транзистор 17 и второй переключающий транзистор 18 несимметричного триггера, нагрузочный транзистор 19 и переключающий транзистор 20 выходного инвертора, информационные выход 21 и вход22 устройства, ключевой транзистор 23 устройства, ячейки 24 памяти программируел1ой логической матрицы.

Триггер 4 представляет собой асинхронный триггер в КМОП вЂ” исполнении на транзисторах 15 - 18. Транзисторы 15 и 17— р — канальные, транзисторы 16 и 18 — n-канальные. Истоки р- канальных транзисторов подключены к выходу 3 блока 1 формирования напряжения питания триггера, истоки п-канальных транзисторов подключены к общей шине 14. Затворы транзисторов 15 и

1566410

16 объединены со стоками транзисторов 17 и 18, образуя обратну,о т риггерную связь.

Затворы транзисторов 17 и 18 объединены со стоками транзисторов 15 и 16, образуя вторую обратную триггерную связь. При этом где Nl — ширина канала соответствующего транзистор:1, L — длина канала сэответствующего транзистора.

Инвертор 7 представляет собой КМОПинвертор, состоящий из р-канального транзистора 19 и и-канального транзистора 20.

Исток транзистора 19 подключен к выходу 3 блока 1 формирования напряжения питания

1риггера. Исток транзистора 20 подключен к общей шине 14, Затворы транзисторов 19 и 20 объединены и подключены к выходу 6 триггера 4. Стоки транзисторов 19 и 20 объединены и представляют выход 21 устройства считывания архитектурного бита программируемой логической матрицы, Транзисторы 8 и 9 обнуляют вход и выход триггера 4. Затворы этих транзисторов объединены и соединены с входом формирователя напряжения питания.

-Устройство работаеl следующим образом.

В зависимосги от уровня сигнала на входе 2 устройство считывания находится в двух режимах. Если сигнал равен уровню логического нуля, то устанавливается режим считывания, В этом режиме транзисторы 8 и 9 закрыты (снимается блокировка триггера) и напряжение питания три гера 4 на выходе 3 открывает транзистор 23. Если ячейка 24 памяти находится в непроводящем состоянии, то на входе 5 триггера 4 устанавливается уровень логической единицы, а на выходе 6 - уровень логического нуля, Этот уровень с Выхода 6 инвертируется инвертором 7 и на выходе 21 устройства устанавливается уровень логической единицы, Если ячейка 24 памяти находится в проводящем состоянии, то на входе 5 триггера

4 устанавливается уровень. логического нуля, а на выходе 6-- уровень логической единицы, На выходе 21 устроиства считывания устанавливается уровень логического нуля.

Если сигнал, поступающий на вход 2, равен уровню логической единицы, то устанавливается режим программирования. В этом режиме напряжение питания на выходе 3 равно нулю, транзисторы 8 и 9 открываются и потенциал на входе 5 и выходе 6 триггера равен нулю.

Сигналом на выходе 3, равным уровню логического нуля, закрыт транзистор 23, и высокое напряжение, необходимое для программирования ячейки 24 памяти и поступающее на вход 22, не передается на схемы 4 и 7 устройства.

В режиме считывания устройство считывания устанавливается в одно из двух состояний, и схема не потребляет ток источника питания. Это состояние можно изменить при переходе в режим программирования, когда уровни сигналов на обоих плечах триггера 4 равны нулю, т.е, триггер 4 сброшен и готов при переходе в режим считывания к повторному считыванию информации с входа?2.

Предлагаемое устройство может работать в режимах считывания и программирования, причем в режиме программирования устройство считывания обнуляется и готово к считыванию информации с перепрограммированного архитектурно о бита.

Формула изобретения

Устройство считывания для программируемои логической матрицы, содержащее несимметричный триггер, выходной инвертор. вход которого соединен с выходом несимметричного триггера, а выход является информационным выходом устройства, о тл и ч а ю щ е е с я тем, что, с целью расширения функциональных воэможностей устройства за счет отключения напряжения питания В режиме программирования, оно содержит формирователь напряжения питаниЯ, сОстОЯЩиЙ из КМОП-инВергора, ВХОД установки режима работы которого является входом установки режима работы устройства, ключевой транзистор, сток которого является информационным входом устройства. а затвор и исток соединены соответственно с выходом формирователя напряжения питания и входом несимметричного триггера, схему обнуления несимметричного триггера, состоящего из первого и второго ключевых транзисторов, истоки которых объединены и соеди-IeHbl c шиной нулевого потенциала устройства, эагворы объединены и соединены с входом формирователя напряжения питания, стоки первого и второго ключевых транзисторов соединены соответственно с входом и выходом несимметричного три гера, шины напряжения питания несимметричного триггера и выходного инвертора объединены и соединены с выходом формирователя напряжения питания, 1566410

Составитель Б,Венков

Техред М.Моргентал Корректор И.Муска

Редактор Н.Тупица

Заказ 1225 Тираж 486 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101