Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано для запоминания выборочных значений аналоговых сигналов. Цель изобретения - повышение быстродействия устройства. Для этого в устройство введена цепь форсированного заряда конденсатора 7, состоящая из второго диодного мостового ключа 4 с блоком управления этим ключом 6 и транзисторов 8, 9. Форсированный заряд конденсатора 7 осуществляется транзисторами 8, 9 при переходе устройства в режим выборки до тех пор, пока разность между входным и выходным напряжениями не уменьшится до 0,7 В. После этого происходит дозаряд конденсатора 7 через ключ 3. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 G 11 С 27/00,, 1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

rIO ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4459771/24-24 (22) 14.07.88 (46) 23.05.90, Бюл. М 19 (72) P.Ý.Êóðûëo (53) 681. 327. 66(088. 8) (56) Авторское свидетельство СССР

М 1345262, кл, G 11 С 27/00, 1986, EDN, 1984, ч,29, N. 13, р, 83, fig 1в. (54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано для запоминания

„„SU„, 1566412 А 1

2 выборочных значений аналоговых сигналов.

Цель изобретения — повышение быстродействия устройства. Для этого в устройство введена цепь форсированного заряда конденсатора 7, состоящая из второго диодного мостового ключа 4 с блоком управления этим ключом 6 и транзисторов 8, 9. Форсированный заряд конденсатора 7 осуществляется транзисторами 8, 9 при переходе устройства в режим выборки до тех пор, пока разность между входным и выходным напряжениями не уменьшится до 0,7 В. После этого происходит дозаряд конденсатора

7 через ключ 3. 1 ил.

1566412

Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано для запоминания выборочных значений и аналоговых сигналов.

Цель изобретения — повышение быстродействия аналогового запоминающего устройства.

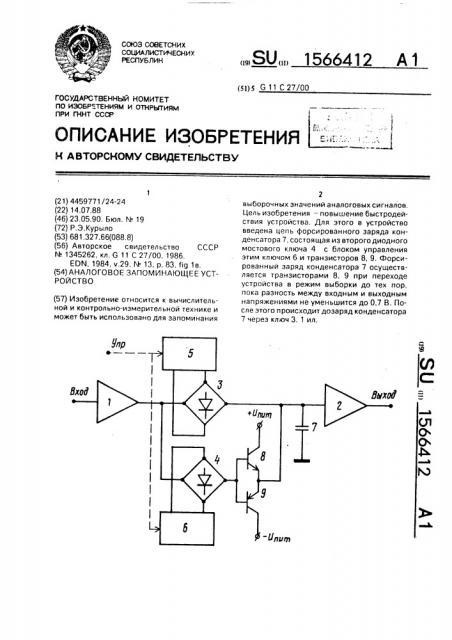

На чертеже приведена функциональная схема устройства.

Устройство содержит буферные усилители 1 и 2, диодные мостовые ключи 3 и 4, блоки 5 и 6 управления диодными мостовыми ключами, накопительный элемент 7 на конденсаторе и ускоряющие элементы на и-р-п транзисторе 8 и р-и-р транзисторе 9.

Аналоговое запоминающее устройство работает следующим образом.

Блоки 5 и 6 управления диодными мостовыми ключами по поступлению тактовых импульсов на вход управления устройства синхронно переводят диодные мостовые ключи 3 и 4 в открытое либо закрытое состояние, переводя аналоговое запоминающее устройство в режим выборки либо в режим хранения.

Если при переходе из режима хранения в режим выборки имеется разница потенциалов между текущим значением входного сигнала и дискретным значением выборочного сигнала, хранимым на накопительном элементе 7, то диодный мостовой ключ 3 разбалансируется и его выходной гок, величина которого определяется величиной тока встроенных генераторов тока схемы 5 управления, заряжает или разряжает накопительный элемент 7. Если разница потенциалов между текущим значением входного сигнала и дискретным значением выборочного сигнала, хранимым на накопительном элементе 7, превышает величину напряжения Ul,g транзисторов 8 и 9, то выходной ток дополнительного диодного мостового ключа 4, максимальная величина которого равна величине тока встроенных генераторов тока схемы 6 управления, открывает в зависимости от знака приращения входного напряжения за период дискретизации транзистор 8 либо 9. Коллекторный ток открытого транзистора 8 или 9, превышающий в Р раз величину выходного тока диодного мостового ключа 4, форсированно заряжает или разряжает накопитель25

55 ный элемент 7 до тех пор, пока разница между входным сигналом и напряжением накопительного элемента 7 не уменьшается до значения Овэ открыто о транзистора 8 либо 9, после чего происходит дозаряд накопительного элемента 7 малым током диодНОГО мостового ключа 3.

Наличие цепи форсированного заряда накопительного элемента 7 позволяет уменьшить время заряда накопительного элемента 7 до напряжения на входе устройства в режиме выборки и повысить тем

cBMblM быстродействие устройства. Повышение быстродействия особенно заметно при увеличении емкости накопительного элемента 7, когда требуется уменьшить поГрешность разряда конденсатора в режиме хранения.

Формула изобретения

Аналоговое запоминающее устройство, содержащее первый буферный усилитель, вход которого является входом устройства, а выход подключен к входу первого диодного мостового ключа, первый и второй управлящие входы которого соединены с соответствующими выходами первого блока управления диодным мостовым ключом, вход которого является входом управления режимом работы устройства, накопительный элемент на конденсаторе, одна обкладка которого подключена к шине нулевого потенциала устройства, другая обкладка --к выходу первого диодного мостового ключа и входу второго буферного усилителя, выход которого является выходом устройства, о тл и ч а ю щ е е с я тем, что. с целью повышения быстродействия устройства, в него введены первый и второй ускоряющие элементы на первом и втором транзисторах соответственно и — р -и- и р-п — р-типа, второй диодный мостовой ключ и второй блок управления диодным мостовым ключом, вход которого соединен с входом первого блока управления диодным мостовым ключом, первый и второй выходы — с соответствующими входами управления второго диодного мостового ключа, вход которого подключен к выходу первого буферного усилителя, а выход к базам и-р-и- и р — n — ртранзисторов, коллекторы которых подключены к шинам соответственно положительного и отрицательного источников питания устройства, а эмиттер — к входу второго буферного усилителя.