Адаптивный цифровой фильтр

Иллюстрации

Показать всеРеферат

Изобретение относится к технике цифровой обработки сигналов и позволяет повысить избирательность. Адаптивный цифровой фильтр содержит АЦП 1, сумматоры 2 и 9, умножители 3 и 10, тактовый генератор 4, регистр 5 сдвига, блок 6 памяти, блок 7 пороговых элементов, вычитатель 8, анализатор 11 уровня шума и блок 12 сравнения. Цель достигается путем уменьшения вероятности подавления высокочастотных компонентов полезных сигналов с помощью введенных анализатора 11 и блока сравнения 12. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„ 1 5664

А1 (51) 5 Н 03 Н 1 7/04

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCKOIVIV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTHPbfTHRM

ПРИ П(НТ СССР (21) 4437042/24-09 (22) 06.06.88 (46) 23. 05. 90. Вюл. 9 1 9 (72) 1П.О.Охлобыстин (53) 681 .32(088.8) (56) Авторское свидетельство СССР

У 1053274, кл. Н 03 Н 17j04, 24.11 ° 81 . (54) АДАПТИВНЫЙ ЦИФРОВОЙ ФИЛЬТР (57) Изобретение относится к технике цифровой обработки сигналов и позволяет повысить избирательность. Адаптивный цифровой фильтр содержит AIlP сумматоры 2 и 9, умнон ители 3 и

10, тактовый генератор 4, регистр 5 сдвига, блок 6 памяти, блок 7 пороговых элементов, вычитатель 8, анализатор 11 уровня шума и блок 12 сравнения . Цель достигается путем уменьшения вероятности подавления высокочастотных компонентов полезных сигналов с помощью введенных анализатора

11 и блока 12 сравнения. 3 ил.

1 566470

Изобретение относится к технике цифровой обработки сигналов и может быть исполь эовано в гидро- и радиолокации, электросвязи для адаптивной цифровой фильтрации сигналов.

Целью изобретения является повышение избирательности путем уменьшения вероятности подавления высоко1О частотных компонентов полезных сигналов .

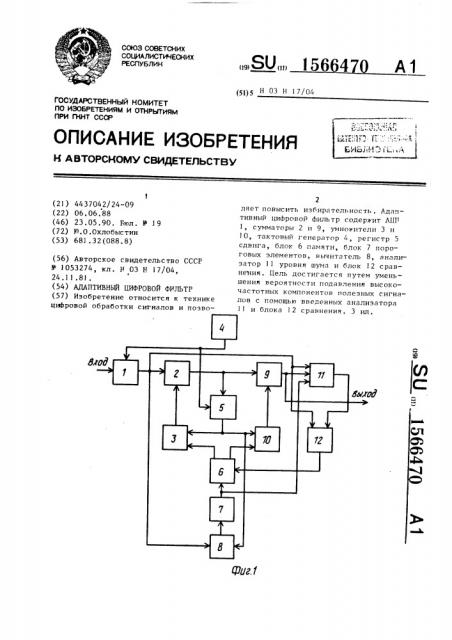

На фиг . 1 прив едена предлагаемого Фильтра; блок-схема анализатора на Фиг. 3 — блок-схема блок-схема на фиг. 2 уровня шума; блока сравне15 ния .

Адапт.ивный цифровой фильтр содержит аналого-цифровой преобразователь (А1Г) 1, первый сумматор 2, первый умножитель 3, тактовый генератор 4, 2О регистр 5 сдвига, блок 6 памяти, блок 7 пороговых элементов, вычитатель 8, второй сумматор 9, второй умножитель 1 О, анализатор 11 уровня шума и блок 1 2 сравнения. Анализа- 25 тор 11 уровня шума содержит вычитатель 13, взвешивающее устройство .14, накопитель 15, блок 12 сравнения накопитель 16 и компаратор 17 двоичных чисел. 30

Адаптивный цифровой фильтр работает следующим образом.

Входной сигнал преобразуется в пифровук Форму с помощью АЦП 1, после че— го пода е тс я на цифров.> и филь тр, и о— строенный на сумматорах 2 и 9, ре-гистре 5 сдвига, умножителях 3 и 10 и блоке 6 памяти коэФфициентов (с целью упрощения показан фильтр первого порядка, увеличение порядка мо- 40 жет быть достигнуто известными способами — каскадированием звеньев и т.п . с соответствующим увеличением числа сумматоров, регистров сдвига и умножителей). Оценка скорости изменения входного сигнала производится вь»читателе>» 8, выходной сигнал которого после преобразования в позиционный код блоком 7 пороговых элементов подается на один из адресных входов блока 6 памяти, хранящего несколько наборов значений весовых коэффициентов, соответствующих различным частотным характеристикам, реализуемым фильтром. Рри увеличении

55 скорости изменения входного сигнала, соответственно, увел»»»ивается выходной сигнал вычитателя 8 и меняется выходной код блока 7 пороговых элементов, вызыва я считывание из блока

6 памяти весовых коэффициентов, обеспечивающих расширение полосы пропускания устройства и более точную передачу полезного сигнала через Фильтр.

При малой скорости изменения сигнала (основная энергия сосредоточена в низкочастотной части спектра) вы— ходной сигнал вычитателя 8 также мал и выходной код блока 7 пороговых элементов вызывает считывание из блока

6 памяти такого набора весовых коэффициентов, которому соответствует более узкая полоса пропускания, что позволяет дополнительно подавить высокочастотные компоненты шума, пропуская без искажения полезный низко— частотный сигнал.

Для достижения цели изобретения необходимо получить оценку уровня аддитивного белого шума во всей полосе частот (вплоть до половины частоты дискретизации сигнала в АЦР 1), »То разрешается в предлагаемом Фильтре с помощью анализатора 11 уровня шума, который построен в виде последовательно соединенных вычитателя 13, Формирукщего разность модулей входных сигналов, взвешивающего устройства 14 (например, умножителя) и накопителя 15, обеспечивающего суммирование последних выходнь»х отсчетов взвешив »юшего устройства 14 (Фиг.2).

Возможность такого построения следующая. Если полоса пропускания Фильтра за время анализа (N последних отсчетов) постоянная, оценку среднего уровня внеполосного шума U ïîëó÷àþò по равенс тву где U (»), 0 „,>„(i) — входно»1 и выходной сигналы фильтра в -м тактовом интервале.

Таким образом для оценки уровня внеполосного шума необходимо произвести суммирование разностей модулей входных и выходных отсчетов Филь тра за N последних тактов. Считая, что шум обладает равномерным энергетическим спектром в полосе 0 — 1 (F

2 1

5 ) 5664 частота дискретизации сигнала в АПП 1), а полоса пропускания фильтра равна

h F от оценки () ) можно перейти к оценке уровня шума U „,,„ во всей полосе частот, введя соответствуюпий весовой коэффициент

"ж — 0 — - —

ГА, -AF F — 2))Р

10 (2) 15

Информация о значении полосы АР пропускания фильтра в каждый момент времени заключена в выходном коде блока 7 пороговых элементов, который поступает на взвешиваюшее устройство )4, 20 входящее в состав анализатора ) 1 уровня шума, последний при этом производит обработку отсчетов в соотчетствии с равенством (2) и формирует на своем выходе оценку уровня шума во всей ис- 25 пользуемой полосе частот )О; F4 )Блок 12 сравнения (фиг ° 3) построен на базе накопителя ) 6 и компаратора )7 двоичных чисел. Накопитель 16 формирует на своем выходе оценку сред-30 него уровня U „ входного сигнала фильтра (выходного сигнала AVP 1) за N последних тактов в соответствии с равенством, аналогичным (1) и

Г,„= —:Е10,„()/. (3)

;= 1

Компаратор 17 двоичных чисел может быть выполнен в виде логического блока, осуществляющего поразрядное сравнение чисел. Известны компараторы двоичных чисел в интегральном исполнении (например, ИС 564 ИП2 для четырехразрядных чисел). Алгоритм работы блока )2 сравнения может быть записан, например, следующим образом:

45

) при U U (4)

0 при в - ып ) где Q — выходной сигнал блока 12 сравнения.

На основании решения, принятого блоком 12 сравнения по (4), можно

1 сделать вывод о присутствии на входе устройства полезного сигнала или только шума (точнее, какое из этих собы70 6 тий является более вероятным) . При

1 наиболее вероятно, что на входе устройства присутствует полезный сигнал и полоса пропускания может быть несколько расширена по сравнению с полосой пропусКания известного фильтра при той же скорости изменения сигнала с целью уменьшения искажений полезного сигнала при прохождении че— рез фильтр. При Я = 0 наиболее вероятно, что на входе устройства присутствует только шум и полоса пропускания может быть несколько уменьшена с целью уменьшения уровня шума на выходе устройства. Такая добавочная перестройка полосы пропускания обеспечивается тем, что выходной сигнал блока 1 2 сравнения, воздействуя на дополнительный адресный вход блока 6 памяти, вызывает считывание из этого блока на умножители 3 и 10 набора весовых коэффициентов, соответствующих измененной полосе пропускания. Количество реализуемых АЧХ может быть и увеличено, например, при полоса пропускания остаЬ,П т ется беэ изменения (определяется, как и в известном Фильтре, только скоростью изменения сигпала), при

U „> С,„„увеличивается, а при

U gy < U шп уменьшается. При этом несколько усложняется компаратор 17 двоичных чисел (Фиг.3) и увеличивается число его выходов.

Таким образом, адаптивный цифровой фильтр позволяет уменьшить вероятность подавления высокочастотных компонент спектра полезного сигнала, т.е. уменьшить искажения полезных сигналов при прохождении через Фильтр, и уменьшить уровень шумов на выходе устройства при отсутствии на входе полезного сигнала

В изобретении на основании сформированной оценки уровня, шума принимается решение о том, какое событие является наиболее вероятным: присутствует на входе полезный сигнал или только шум. На основании этого решения соответствующим образом может быть изменена полоса пропускания.

Формула изобретения

Адаптивный цифровой Филь тр, содержащий последовательно соединенные тактовый генератор, аналого-циф1 566470

Ом аю

3prmycp уроЖчх

Составитель Л. Тимошина

Техред М.Ходанич Корректор Т.Палий

Редактор И. Шулла

Заказ 1228 Тираж 650 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5.

Производственно-издательский комбинат "Патент", г. Ужгород, ул. I ëãàðèíà, 101 ровой преобразователь, вход которого является входом адаптивного цифрового фильтра, вычитатель, блок пороговых элементов, блок памяти, первый умножитель, первый сумматор, к второму входу которого подключен выход аналого-циФрового преобразователя, регистр сдвига, выход которого подключен к второму входу вычитателя, второй. умножитель, к второму входу которого подключен второй выход рлока памяти, и второй сумматор, к второму входу которого подключен выход первого сумматора, выход второго сумматора является выходом адаптинного цифрового фильтра, а выход тактового генератора подключен к тактовому входу регистра сдвига, о т— л и ч а ю шийся тем, что с це" лью повышения избирательности путем

5 уменьшения вероятности подавления высокочастотных компонентов полезных сигналов, между выходом второго сумматора и вторым адресным входом блока памяти введены последовательно соединенные анализатор уровня шума, к второму входу которого подключен выход блока пороговых элементов, и блок сравнения, к второму входу которого и третьему входу анализатора уровня шума подключен выход аналогоциФрового преобразователя.